# A Performance Study of the Acorn RISC Machine

# A thesis

submitted in partial fulfilment of the requirements for the Degree

of

Master of Science in Computer Science

in the

University of Canterbury

by

David Vivian Jaggar

University of Canterbury 1990

# **Abstract**

The design decisions behind the development of the Acorn RISC Machine (ARM) are investigated, by implementing the architecture with a software emulator, to record the effectiveness of the unusual architectural features that make the ARM architecture unique.

The adaption of an existing compiler construction tool (the Amsterdam Compiler Kit) has demonstrated that an optimising compiler can exploit the RISC architecture to maximize CPU performance.

By compiling high level language algorithms, a complete picture of the effectiveness of the ARM architecture to support high performance computing is formed.

# Contents

| Abst                 | tract                               | 2  |

|----------------------|-------------------------------------|----|

|                      | tents                               |    |

|                      | ares and Tables                     |    |

|                      | nputer Design                       |    |

|                      | The Central Processing Unit         |    |

|                      | The Instruction Set                 |    |

|                      | Microcode                           |    |

|                      | Registers                           |    |

|                      | The Memory                          |    |

|                      | Advancing Technology                |    |

| RISC                 | C Architectures                     |    |

|                      | Improving Performance               |    |

|                      | Cycles per Instruction              |    |

|                      | Time per Cycle                      |    |

|                      | Instructions per Task               |    |

|                      | RISC Development                    |    |

|                      | Commercial RISC Designs             |    |

|                      | Other Commercial RISC Architectures |    |

| The                  | Acorn RISC Machine                  |    |

| 1110                 | Architecture Characteristics        |    |

|                      | The Impact on Performance           |    |

|                      | Evaluating an architecture          |    |

| Com                  | puter Software                      |    |

| Com                  | The Operating System                |    |

|                      |                                     |    |

|                      | Application Programs                |    |

| An C                 | Optimising Compiler for ARM         | 76 |

| $\Delta \Pi \Lambda$ | ADDITION TO THE TOT A DAY.          |    |

| Compiler Building Tools76                         |

|---------------------------------------------------|

| EM code and the Code Generator Generator8         |

| Global and Peephole Optimisers8                   |

| The Assembler and Linker8                         |

| The After–Burner Optimiser90                      |

| Register Allocation92                             |

| Compiler Validation9                              |

| Evaluating an Architecture96                      |

| Architectural Features96                          |

| Measuring the Quality of an Architecture9         |

| Architectural Emulation100                        |

| Emulator Validation and Performance103            |

| The Quality of the ARM Architecture105            |

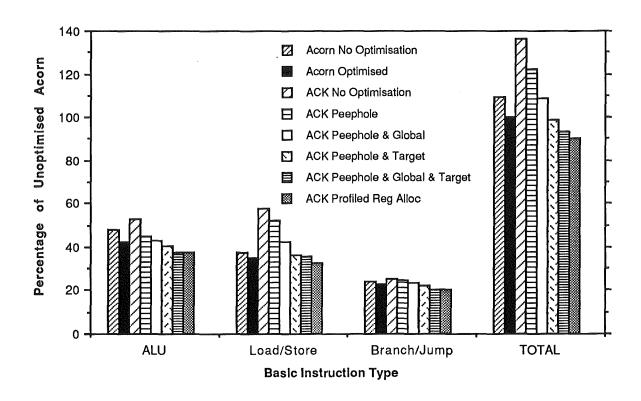

| Compiler Performance106                           |

| Architecture Performance109                       |

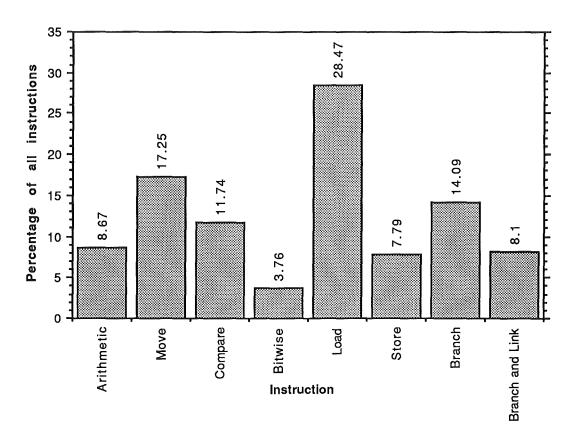

| Instruction Usage110                              |

| Branch and Conditional Instruction Utilisation115 |

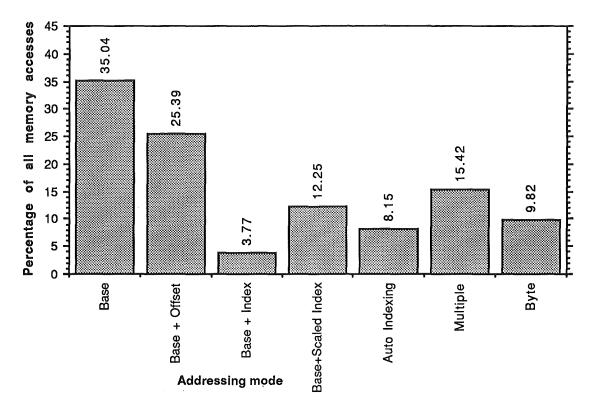

| Memory Accessing Instructions118                  |

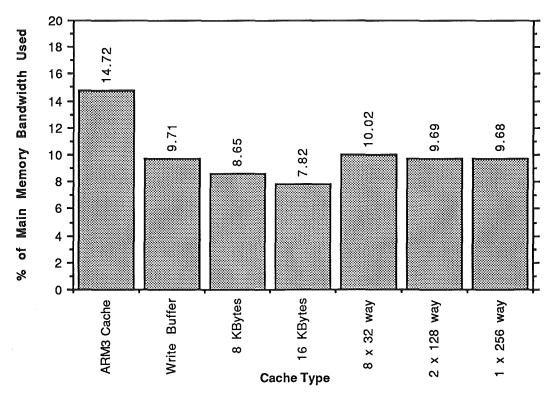

| Cache Effectiveness119                            |

| Improving the ARM architecture120                 |

| Conclusion                                        |

| Acknowledgements                                  |

| Bibliography131                                   |

| ARM 3 Instruction Set Format                      |

| EM Instruction Set                                |

| Floating Point Accelerator Instruction Set145     |

# Figures and Tables

| Figure 1: A Simple CPU                                        | 8    |

|---------------------------------------------------------------|------|

| Figure 2: An Instruction Pipeline                             | 27   |

| Figure 3: SPARC Register Window Layout                        | 38   |

| Figure 4: ARM Register Layout                                 | 52   |

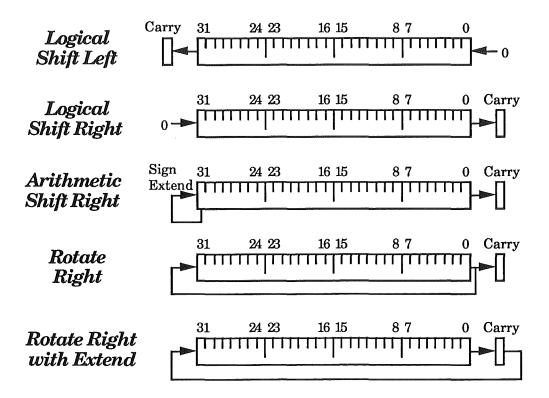

| Figure 5: ARM Shift Operations                                | 53   |

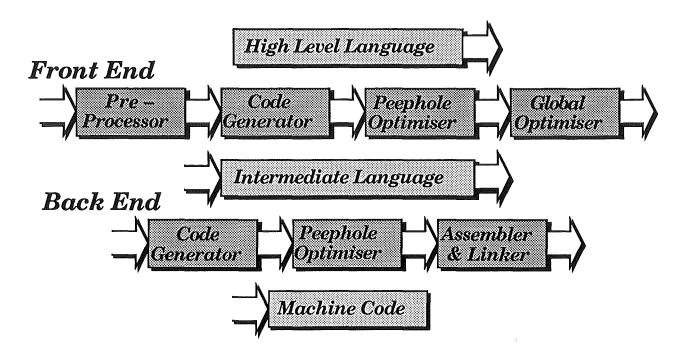

| Figure 6: Compiler Stages                                     | 67   |

| Figure 7: ARM Signed Divide Routine                           | 87   |

| Figure 8: Emulator Execution Breakdown                        | .104 |

| Figure 9: Acorn and ACK Compiler Performance                  | .107 |

| Figure 10: Relative Instruction Usage                         | .111 |

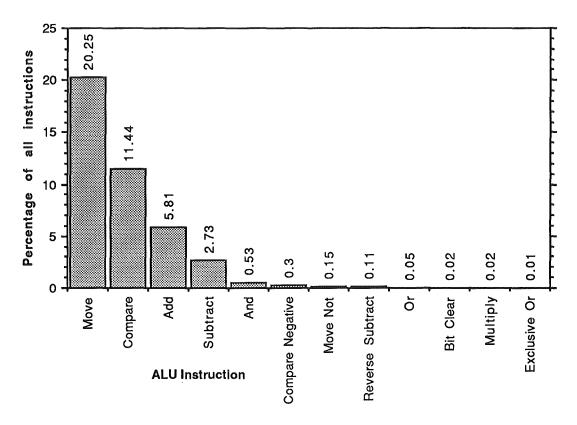

| Figure 11: Data Processing Instructions                       | .113 |

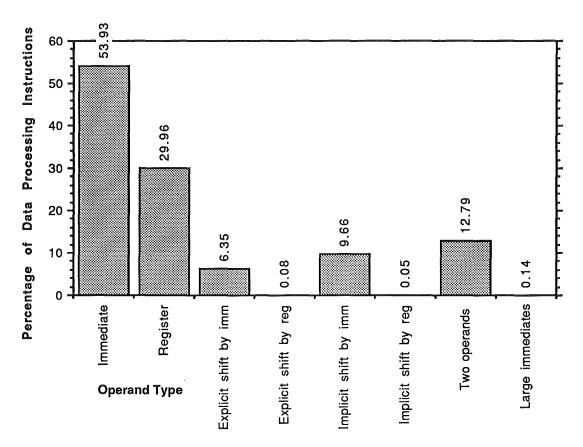

| Figure 12: Data Processing Operands                           | .114 |

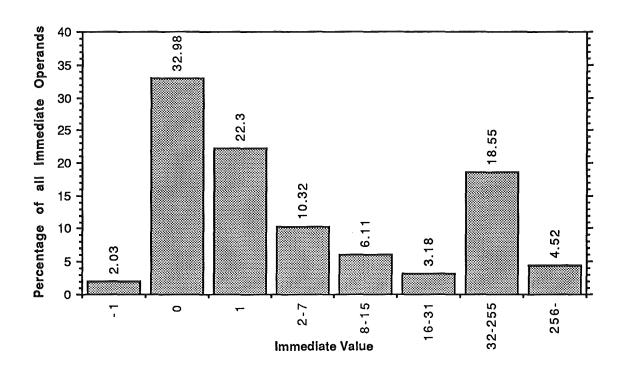

| Figure 13: Data Processing Immediate Operands                 | .116 |

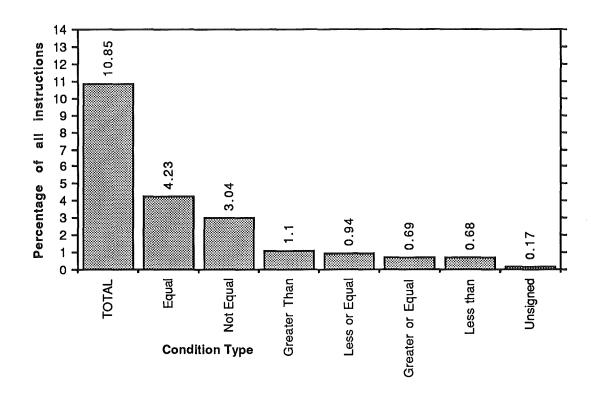

| Figure 14: Conditional Non-Branch Instructions                | .117 |

| Figure 15: Addressing Modes                                   | .119 |

| Figure 16: Cache Strategies                                   | .124 |

|                                                               |      |

| Table 1: A Simple Instruction Set                             | 10   |

| Table 2: Code Size for CISC (MC68020) and RISC (SPARC)        | 31   |

| Table 3: Relative Frequency of High Level Language Statements | 36   |

| Table 4: ARM Instruction Set                                  | 46   |

| Table 5: Architectural Benchmarks                             | .105 |

To my Mother and Father

# Chapter 1 Computer Design

The performance of a computer system is measured by the time that it takes to execute programs, the shorter the elapsed time the higher the performance rating. To maximise the performance a designer must find ways to match the performance of each component in the computer, to yield a balanced system. As technology changes and new discoveries are made, different parts of a computer become the performance bottle—neck.

The architecture of a computer defines the major attributes of the design. The number of registers, their layout, the instructions and addressing modes that the computer understands are all part of the architecture, while the number of clock cycles taken to execute each instruction, the type of transistor logic used to build the CPU, and the layout of memory are part of the implementation.

# The Central Processing Unit

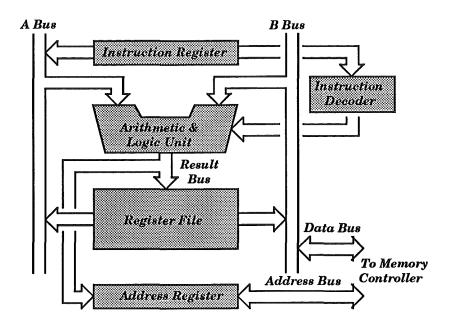

The Central Processing Unit (CPU), as shown in Figure 1, is the part of the computer that executes instructions. The CPU is composed of a number of specialized functional units (for example the Arithmetic Logic Unit, or ALU). These functional units are controlled by the Instruction Decoder, which activates the necessary sections of each unit to carry out the operation specified by each instruction. Each functional unit is connected by data paths, along which data, parts of decoded instructions and internal control information flows.

Figure 1: A Simple CPU

#### The Instruction Set

The instruction set of a computer (the machine code) is the language that is used to directly program the CPU. The instruction sets of computers are significant factors in the overall price/performance of the machine. Each instruction of the CPU must be implemented using digital logic that must be custom designed (using "microprogramming" to replace some logic by sacrificing performance is discussed later). This "custom silicon" is extremely labour intensive to construct, so that a large and/or complex instruction set is very expensive to implement in hardware. Emulating some instructions with software is less expensive, but lowers the performance of the computer, due to the inefficiency of using combinations of the existing instructions to emulate missing instructions.

Whilst machines exist whose instruction set is tailored for one specific high level language, such a design would be inappropriate for a general purpose microcomputer. Table 1 illustrates a simple instruction set. An instruction set must be able to efficiently support the many unique features specific to different high level languages, although programming languages have major features in common —

#### i) arithmetic operations for integer and floating point data.

An instruction set will need operations to move data to and from the memory and registers, and be able to perform some simple arithmetic on that data. Integer addition and subtraction instructions are found in the simplest of CPUs, while multiply and divide are quite common in more complex architectures. The results of such instructions usually update the processor's condition flags: a negative result will set the negative flag, a zero result will set the zero flag, a carry or borrow from additions and subtractions will set the carry flag, and an overflow will set an overflow flag. Floating Point operations are usually carried out in a totally separate processor, the Floating Point Unit (FPU), but the functions it performs are similar to the integer unit.

#### ii) operations on Boolean data.

Boolean values, arrays of Boolean values, and sets require bit—wise logical operators like And, Or and Exclusive Or. The And operator is used to clear a bit, Or is used to set a bit, and Exclusive Or is used to toggle a bit. Operations on bit fields such as Not, Left Shift, Right Shift and Rotate can be used to build values for comparison with Boolean data.

| Instruction            | Mnemonic              | Operation                                                             |

|------------------------|-----------------------|-----------------------------------------------------------------------|

|                        |                       |                                                                       |

| Add                    | ADD                   | Dest := Src1 + Scr2                                                   |

| Subtract               | SUB                   | $\mathbf{Dest} := \mathbf{Src1} - \mathbf{Src2}$                      |

| Logical AND            | AND                   | Dest := Src1 AND Src2                                                 |

| Logical OR             | OR                    | $\mathbf{Dest} \coloneqq \mathbf{Src1} \ \mathbf{OR} \ \mathbf{Src2}$ |

| Logical EOR            | EOR                   | Dest := Src1 EOR Src2                                                 |

| Logical NOT            | NOT                   | Dest := NOT Src1                                                      |

| Logical Shift Left     | LSL                   | $Dest := Src1 * 2^{Src2}$                                             |

| Logical Shift Right    | LSR                   | $Dest := abs(Src1/2^{Src2})$                                          |

| Rotate                 | ROT                   | Dest := Src1 Rotated Src2 bits                                        |

| Arithmetic Shift Right | ASR                   | Dest := Src1/2                                                        |

| Compare                | CMP                   | Src1 - Src2                                                           |

| Move                   | MOV                   | Dest := Src1                                                          |

| Multiply               | $\mathbf{MULT}$       | Dest := Src1 * Src2                                                   |

| Divide                 | DIV                   | Dest := Src1 / Src2                                                   |

| Jump                   | JMP                   | PC := Dest                                                            |

| Procedure Call         | $\operatorname{CALL}$ | Dest := PC, PC := Dest                                                |

| Procedure Return       | RET                   | PC := Dest                                                            |

| Conditional Branch     | Bcc                   | IF cc PC:=PC+offset                                                   |

Where: Dest, Src1 and Src2 are registers or memory addresses

PC is the program counter

cc is a condition code

offset is an address offset

Table 1: A Simple Instruction Set

# iii) support for the conditional execution of instructions depending on some previous condition.

A compare instruction can be used to compare two pieces of data. The condition flags are usually set to reflect the result of the last compare instruction, the negative flag indicating which operand was the larger and zero flag if they were equal. A branch instruction will jump to a different part of the program depending on the state of one

or more condition flags, for example "Branch on Greater Than or Equal to". Many architectures combine the compare and branch instructions, as they are usually used together. These instruction are used to implement IF statements, conditional loops (FOR, WHILE etc.) and CASE type statements.

#### iv) jump instructions to change the flow of execution.

High level language constructs like infinite loops, premature loop terminators and GOTO statements require a Jump instruction to unconditionally alter the value held in the program counter.

#### v) constructs to implement procedure calls.

By storing the current value of the program counter, and using a jump instruction, a program can execute a procedure and then continue execution just after the point of call by jumping back to the value in the stored program counter. If the return address is pushed onto a stack, then procedure calls can be nested, and procedure recursion is possible.

#### vi) addressing modes to access data structures held in memory.

Data structures like Pascal's arrays and records require the processor to be able to load data to and from an address determined by adding an offset to a base address. The base address holds the address of the start of the array or record and the offset holds the distance of the required element from the beginning. These same addressing modes can be used to access data held in the stack frame of a procedure held on the stack.

Of course, all programming languages have their own characteristic features, and a general purpose architecture must cater for these. The microprocessors designed in the early 1980's added many instructions and addressing modes to the simple instruction set shown in Table 1 to add hardware support for the features of many high level languages. This has the unfortunate side effect that some instructions will be completely useless in some situations, effectively a waste of "silicon real estate" on the CPU chip.

#### Microcode

The amount of custom logic required to directly implement a very large instruction set to support high level languages is too large to fit on a single chip. Only implementing a small number of instructions in hardware and emulating all others in software is inefficient, due to the overheads involved in the trap handler for unimplemented instructions (each unimplemented instruction must be fetched from memory, decoded in software, and its action emulated with other instructions). Microcode is a very low level instruction format that is suitable for complete implementation in hardware, and is tailored for the efficient emulation of machine code instructions. Each machine code instruction is executed by running a sequence of microcode instructions (called a micro program). The microcode sequences are stored in a Read Only Memory (ROM) that is part of the CPU. The uniform nature of a ROM makes much more efficient use of logic than the custom logic used in a functional unit, so that the entire machine code instruction set can be implemented. Microcode is extremely tedious to write, because the program must obey stringent timing restrictions when accessing each functional unit of the CPU. Thus the microcode is usually fixed at the time of manufacture, and

the CPU can be programmed using the higher level machine code. Different implementations of the same architectures can be produced by adding extra functional units to the CPU to eliminate the need for certain microcode sequences. Microcoding is a price/performance compromise — another level of interpretation has been added to the CPU which, although it reduces the cost and makes more efficient use of chip space, also lowers the performance compared to a CPU with a complex "hard—wired" instruction set.

## Registers

The program data is usually kept in registers in the CPU while it is being referenced frequently, so that access to it is as fast as possible. The ALU and registers are connected by data paths, called buses, which carry 32 bits of information in parallel in a 32 bit computer. The buses connect to the register file via a port. The register file will need two read ports and a write port if an instruction like "add the contents of two registers and store the result in a third register" is to be executed in a single clock cycle. The registers are arranged in a bank (or file), which usually consists of a small, fast Static Random Access Memory (SRAM). The actual number of registers is usually limited by the number of bits required in each instruction word to encode the register numbers and the amount of CPU chip area that is available. Not all CPU's have registers (data is accessed directly in memory [Ditz87]), some have as many as 192 [AMD87, Lehr89], but typical numbers are 16 and 32.

#### The Memory

The memory of the computer stores instructions and data. Several separate memory chips are attached to one memory controller to provide a homogeneous memory bank. The CPU is connected to a memory controller via two buses, the data bus (which carries data to and from the memory) and the address bus (which dictates the required memory address). The memory controller is responsible for activating the correct memory chip(s) for the memory address required.

Size and speed of memory are major influences on the cost and the execution speed of the computer. The size of the memory is directly proportional to the cost; pay twice as much and get twice as much.

Modern microcomputer applications need at least 1 MegaByte of main memory, larger machines have 8 to 16 MegaBytes. The speed of the memory is more subtly related to the cost, being dependent on two factors—

#### (i) Latency.

The time taken for the memory to return the first word of data.

#### (ii) Bandwidth.

The rate at which data can be transferred to the CPU, once the initial flow is established.

The execution speed of a program is dependent on both these factors. The performance of a program that consists entirely of jump or branch instructions and data accesses to non contiguous memory locations will be limited by the memory latency, because after every branch or jump the memory must restart the flow from a new location, while the performance of a program that has no branch or jump instructions and contiguous

data accesses will be limited by the memory bandwidth. Of course a real program will have some branch or jump instructions and some random and some contiguous data memory accesses, so the demand on the memory will be between these two extremes. There are several ways of increasing memory access speed —

#### (i) Faster Memory Devices.

Using faster memory chips will increase the bandwidth and reduce the latency. Dynamic Random Access Memory (DRAM) can deliver up to about 6 Million random accesses per second. To gain more speed than this, Static Random Access Memory (SRAM), which can provide 100 Million accesses per second, must be used. The price difference between DRAM and SRAM makes it too expensive to build a microcomputer with a memory made only of SRAM; a compromise is discussed below, which utilises both SRAM (for speed) and DRAM (for its low cost) to implement a fast, relatively inexpensive memory.

#### (ii) Wider buses.

Multiple memory devices connected in parallel, each connected to the same memory controller, increases the memory bandwidth but does not alter the latency. A bus that is twice as wide will deliver nearly twice the usable performance despite the wastage that occurs due to operations involving data objects much smaller than the bus size (for example, byte operations on a 16 bit bus leaves the bus 50% unused, whilst on a 32 bit bus the bus is 75% unused). Unfortunately increasing the size of a memory bus beyond 32 bits is currently too expensive to be used in a low cost micro-computer.

#### (iii) Interleaved memory banks.

Multiple (interleaved) memory devices connected in parallel to separate memory controllers allow one bank of memory to supply data to the processor while the other(s) are recovering from supplying previous data. This increases both the bandwidth (because separate banks have more time to recover between accesses) and reduces the latency (because on average a memory access will be to a memory bank that has already had some recovery time), but the added cost of a separate memory controller for each bank of memory may be prohibitive.

#### (iv) Fast access modes.

By exploiting the physical layout of DRAM consecutive memory accesses to sequential memory locations can be significantly faster than completely random ones, without increasing the price of each memory device. These type of DRAMs are known as Page Mode DRAMs or Static Column DRAMs. This technique will increase the bandwidth of the memory, but not alter latency. The cost of this implementation is merely adding an extra control line from the CPU to the memory system to indicate that the current memory reference is in sequence with the last.

#### v) Harvard architecture.

Rather than storing both instruction and data in a single memory (a von Neumann architecture), there may be two physically separate memories for instructions and data – a Harvard architecture, to double the memory bandwidth. Of course a Harvard architecture will require two address buses and two data buses, but it will be possible to read the next instruction and perform a load or store operation in

parallel. This extra performance comes with the cost of building a computer with twice as many bus lines, which is extremely expensive.

#### vi) Cache memory.

Because programs tend to reference the same areas of memory repeatedly (while executing loops and accessing data structures in memory) it will be more efficient to store frequently used instructions and data temporarily in a small, very fast SRAM, rather like holding data in CPU registers while it is being accessed, and use less expensive DRAM for the rest of the memory. Every time data is loaded from DRAM it is stored in the SRAM "cache" as well as being passed to the CPU. Then if the CPU requests this same data from the memory again, it can be supplied much sooner from the cache, allowing the CPU to maintain its maximum instruction and data throughput.

A cache "hit" occurs when the requested data currently resides in the cache, a cache "miss" occurs when requested data does not reside there. The performance of a cache is measured by its hit ratio – the proportion of cache hits in relation to the total number of memory references. The hit ratio of a cache is dependent on various design parameters, for instance the algorithm used to decide where to put new data in the cache. The following algorithms are suitable for a fast implementation in hardware –

#### a) Direct Mapped Cache.

This is the simplest system: low order bits of the main memory address are used to determine a unique location in the cache memory for the data. Unfortunately if a program references two blocks of memory that have the same low order address bits, the cache will be repeatedly filled with new data (or instructions) from alternate memory blocks, continually overwriting data that will be required again.

#### b) Dual Set Associative Cache.

To ease the problem with a direct mapped cache, two locations can be reserved for each low order address bit combination, and new data will be placed in the Least Recently Used (LRU) location. A single bit is enough to record the last location used. Now three separate memory references with the same low order address bits will be required to spoil the cache's efficiency; this situation is very rare.

#### c) Multi Set Associative Cache.

The associativity of the cache may be increased to four or further, but the LRU algorithm for deciding the position of new data becomes much more complex. The associativity is usually a power of two because this makes the most efficient use of LRU hardware.

#### d) Fully Associative Cache.

Now each item of data can reside anywhere in the cache, and corresponding addresses must be stored to identify the data. A content addressable memory is used to store the data. This special memory instantaneously returns the data associated with an identifier (in this case the data associated with a memory address). A disadvantage of this scheme is the need for every

piece of data in the cache to have its associated address stored with it, using up valuable hardware space that could have been used to make a larger, less complex cache. The solution is to store the contents of a number of successive locations with a single address, called a cache line. When a cache miss occurs, a complete cache line is fetched from the main memory. Although this sounds theoretically inefficient, in practice sequential cache locations are likely to be accessed together anyway, thus caching an entire line at once allows for the utilisation of the page mode access feature of the DRAM main memory. Using an LRU algorithm to find a location for new data in a fully associative cache is very complex to implement in hardware, and has a pathologically worst case when the number of items to be cached is just bigger than the size of the cache and the items are always accessed in the same order (such as the instructions in a loop or the elements of an array) – the LRU algorithm always replaces oldest (soon to be needed) data in the cache with the new data, so the cache always misses. An alternate to LRU is a random replacement scheme. The value from a fast counter is used to provide a pseudo random location for new data. This scheme is easy to implement, and works as well as LRU whilst avoiding LRU's pathological case.

The cache can be used for virtual or physical memories (or even separate caches for each), and each alternative has disadvantages. A virtual memory (or "virtually mapped") cache will need to have some entries invalidated every time a new page translation is calculated, and a physical memory (or "physically mapped") cache will be slowed because it must wait for the virtual to physical address translation

before it can look up any data. Both these types of cache are common in commercial computers.

There are two ways of maintaining the consistency of data between the cache and the main memory when a memory store operation is executed –

#### a) Write through.

The obvious approach is to write data to the cache and main memory at the same time. Unfortunately this simple scheme means that main memory will be referenced by every store operation, which is contrary to the caching principle.

#### b) Write back.

Data can be just written to the cache and then copied to memory if the cache entry is ever to be overwritten again. This strategy will avoid memory references between successive writes to the same memory address, but requires a "dirty" flag for each cache entry to indicate if the data needs to be saved back to memory before the location is reused.

A "write buffer" can be used in with either strategy to allow the processor to continue instead of waiting for the data to be written to main memory.

A cache memory is particularly useful for a Harvard architecture.

Instead of having two separate main memories for instructions and data, two caches are used, one for instructions, the other for data.

Separate address and data buses are still required for instructions

and data, but they only connect to their associated caches, because both caches share a common address and data bus to access a common main memory. The main memory only needs enough bandwidth to supply data for cache misses, rather than all CPU traffic. For a more complete description of cache principles see [Smit82]

It is possible to combine two or more of these implementation techniques to achieve the performance required for a microcomputer memory system.

## **Advancing Technology**

The microprocessors designed in the early 1980's tended to have large number of complex instructions and addressing modes, intended to provide similar computational power with a single chip CPU as the mainframe computers of the 1970's achieved with their multiple chip (and usually multiple circuit board) CPUs. This level of micro-processor complexity was made possible by the advent of Very Large Scale Integration (VLSI), and the resulting computers using these micro-processors have become known as Complex Instruction Set Computers (CISCs). This complexity was used to alleviate several problems –

#### i) Slow core memory.

The magnetic core memory used for main memory was very slow compared to the speed of access to the on-chip microcode ROM, causing the execution time of programs to be proportional to the number of instructions in the program. Thus more complex instructions were implemented with microcode to replace sequences of simple instructions, to avoid repeated accesses to core memory.

#### ii) Compact assembly language.

Complex instructions aided assembly language programmers by replacing common sequences of instructions with a single instruction. As software was becoming a significant factor in the cost of a computer system, and a large proportion of software was written in assembly code to reap the maximum performance of the machine, any such aid given to assembly language programmers would be useful.

#### iii) High level language support.

Complex instructions and addressing modes were thought to help compiler builders by closing the semantic gap between high level languages and assembly language. Designers supported high level language features with fast hardware to improve performance. Making high level languages efficient was also important to help keep software costs down.

#### iv) Good compiler targets.

These complex designs had few registers, because compilers for stack or memory to memory architectures were far easier to construct. Registers were difficult to allocate optimally for local variable use, so were mainly used as temporary storage in expression evaluation, and as pointers to data structures.

#### v) Easily adaptable.

Microcode was an efficient way to utilise the advancing technology

used to build a CPU. As more transistors could be placed on a chip, more microcode could easily be added to build a bigger and more complex instruction set, and more dedicated hardware could be added to speed up microcode instructions.

The Digital Equipment VAX architecture is a good example of an elaborate instruction set, with instructions for polynomial evaluation, queue manipulation and cyclic redundancy checks. The Intel 80x86 series microprocessors are some of the most complex, having instructions to operate on entire strings, complex looping instructions and table look up instructions. The Motorola 680x0 series has instructions to insert and extract bit fields to and from a word, to search words for a set or clear bit, and complex module calling instructions.

# Chapter 2 RISC Architectures

There are several deficiencies with the Complex Instruction Set approach to improving computer performance –

#### i) Compilers cannot utilise the complexity.

Modern compilers have extreme difficulty applying complex instructions to high level languages. Complex instructions rarely perform the exact task required by a high level language: if an instruction does not quite do what is required then its action must be modified with other instructions, or completely replaced with new instructions. An instruction that does more than is required is wasting execution time doing wasted work. In tracing compiled code executing on a complex architecture, researchers noticed that the same twenty percent of instructions accounted for eighty percent of all executed instructions, and a further ten percent of instructions accounted for almost all instructions executed. The remainder of the instruction set was unused and therefore unnecessary. [Sun87a].

#### ii) Complexity implies poor performance.

Complex instructions take a long time to load from core memory and take a long time to decode. Because of the variable lengths of complex instructions, each must be partially decoded before it can be executed. This complexity makes it extremely difficult to have a complex instruction loaded and decoded, ready for execution after a sequence of fast instructions, so the ALU must wait for the complex instruction to be loaded and decoded. Even worse, the complex instructions add extra length to the main execution data path which

decreases the execution speed of all instructions. Thus an instruction which lengthens a data path by ten percent must increase the execution speed of programs by more than ten percent to be justified.

### iii) Memory to memory architectures are inefficient.

Although it is difficult to write compilers for register based architectures, registers are very efficient for the storage of variables and procedure parameter values. Memory to memory models access memory too often to be as efficient. Stack based machines can be made efficient, but a considerable amount of hardware is still required to approach the efficiency of registers.

#### iv) Assembly language is a slow programming environment.

The compiler that can produce good machine code from a high level language will replace the assembly language programmer, because writing programs in assembly language is too slow to use for most programming tasks. A good architecture should make it possible for a good optimising compiler to produce code of comparable quality to assembly language programmers.

#### v) Long design time.

Complex architectures are difficult to design, take a long time to verify and manufacture, and therefore cannot be designed to take advantage of the latest technological advances.

## **Improving Performance**

The time it takes for a computer to perform a task is a product of three factors —

Time per Task =  $C \times T \times I$

where C is the cycles per instruction

T is the time per cycle

I is the instructions per task

Improving any of these factors will improve performance. The first two factors tend to be complementary – an architecture may have a long cycle time to accommodate complex instructions, or it may have multiple (shorter) cycles per instruction.

Complex Instruction Set Computers attempt to minimise the time per task by minimising the instructions per task, by making each instruction do a lot of work. In practice this lengthens either or both of the cycles per instruction and the time per cycle in greater proportion, so that performance suffers as a result.

Reduced Instruction Set Computers (RISCs) follow new computer architecture and implementation design disciplines — minimising the number of cycles per instruction and decreasing the cycle time to increase performance.

# Cycles per Instruction

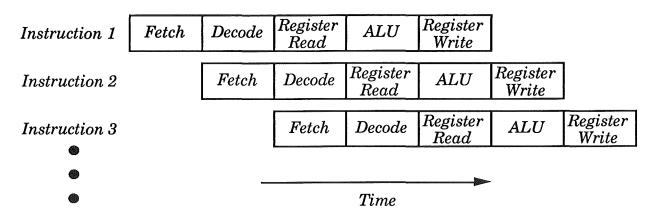

RISCs achieve a short cycle time by implementing a very simple, but very fast instruction set. This simple instruction set allows several instructions to be "pipelined" – several instructions are at different stages

of execution at one time, to maximise the usage of different functional units of the processor. Figure 2 shows a pipeline with five stages, instruction load, decode, register read, ALU operation, register write. Instructions still require several cycles to be executed, but because each stage is done in parallel with other instructions at a different stage, a throughput approaching one instruction per cycle can be maintained.

Figure 2: An Instruction Pipeline

Data dependencies occur between each instruction in the pipeline because an instruction can read from the registers before the previous instruction has written its results. These dependencies are resolved by adding forwarding logic to the CPU to by—pass the register file, routing the result value directly from one instruction to the input value of the next instruction.

The number of cycles each instruction adds to the total number of cycles taken to execute a program is potentially reduced by the number of stages in the pipeline (called the pipeline depth). Fulfilling this potential requires the pipeline be always filled with instructions, a task that is very difficult unless all instructions are the same (encoded) length, and take approximately the same amount of time to execute. So RISC instructions

are always one (usually thirty two bit) word long, and most require only a single cycle ALU operation. A CISC architecture cannot fully achieve either of these goals: its complex instructions are impossible to encode using the same number of bits or to execute in the same time period (cycle length). The data paths in a RISC architecture need only carry word sized objects around the CPU, a CISC architecture must be able to move its multi word instructions around the CPU, which adds cost and complexity.

Instructions that change the value of the program counter (branches, jumps, traps, procedure calls and procedure returns) make it difficult to keep the instruction pipeline full. To avoid stalling the CPU while new instructions are loaded from the new memory location, instructions like branch are usually implemented with a delayed action: the instruction immediately after the branch instruction (said to be in the branch delay slot) is always executed after the branch instruction is executed. The compiler can often find an instruction to put in the delay slot to do useful work, if it cannot a NOP (No-OPeration) instruction must be inserted.

Instructions that access memory require special attention for two reasons. Firstly a full memory addressing mode takes many instruction bits to encode — too many to specify each operand of every thirty-two bit instruction, so a "load/store" architecture is implemented: only the load and store instructions can access memory; all other instruction only access data that is held in registers. The second problem is that the data from a load instruction will not be available to all subsequent instructions, due to the slow access speed of main memory. The solution is to provide delayed load instructions, the instruction after the load (in the load delay slot) cannot access the register into which the load instruction will place

the data. Again the compiler attempts to find a suitable instruction for the load delay slot, if this is not possible a NOP must be inserted.

#### Time per Cycle

The length of a single machine cycle is determined by several factors. Firstly the instruction decode time is related to both the number of instructions in the instruction set and the number of instruction formats supported. Clearly a CISC architecture will require a longer decode time than a RISC architecture. Most RISC architectures have only a few levels in their decode strategy: the instructions are first split into broad "families" by examining a few key bits in each word, then each instruction can be fully decoded. Complex addressing modes in CISC architectures lengthen the decode time substantially, although the National 32x00 series of processors have a very uniform instruction set, which results in a fast instruction decode time. Other CISC architectures, such as the Motorola 680x0 and Intel 80x86 architectures have very complex instruction formats, due to their backward compatibility with their respective ancestors.

The second factor in the time per cycle is the instruction operation time. RISC architecture instructions usually have a single cycle ALU stage, so that the flow of instructions through the processor is not interupted. Instructions that require more ALU work (such as integer multiply and divide) are often set running in parallel with single cycle instructions. CISC architectures have many multi—cycle instructions, which makes efficient pipelining of instructions very difficult. Considerable amounts of extra hardware are required to support data dependencies between instructions (i.e. the result of one may be required for a source operand of

the next instruction), which uses precious chip space and lengthens critical processor data paths.

The time needed to fetch instructions from main memory is the third factor influencing the time per cycle, and is inversely proportional to the memory bandwidth. Instruction memory latencies are only incurred by instructions that alter value of the program counter, as new instructions must be loaded from a new memory address. The techniques described in Chapter 1 can be utilised to increase the memory bandwidth to decrease its influence on the time per cycle. RISC architectures can load a new instruction in every memory access, because all instructions are the same length. CISC architectures require multiple memory accesses to load multi word instructions, again making efficient pipeline management much more complex.

The last factor in the time per cycle is caused by the basic architectural complexity of an architecture. RISC designers can spend more time hand optimising critical processor features such as the processor data path and functional units. CISC architectures have a much longer design and implementation cycle, and hand optimising a complex architecture is a task too large to be practicable.

# **Instructions per Task**

Because of the simple instruction set, RISC architectures require more instructions than CISC architectures to perform the same task. Table 2 illustrates the length of the machine code of fifteen UNIX utilities, for two common architectures, a Motorola 68020 [Moto85] based Sun 3/60, and a SPARC based SUN SPARCstation [Sun87b], using similar compiler

technology, and compiling for the same Operating System. The 68020 CISC architecture has quite compact machine code, the SPARC architecture is a good example of a RISC architecture.

| Program               | MC68020 | SPARC  | <u>SPARC</u><br>MC68020 |

|-----------------------|---------|--------|-------------------------|

|                       |         |        |                         |

| awk                   | 43856   | 50014  | 1.14                    |

| bc                    | 10314   | 12462  | 1.21                    |

| cmp                   | 3000    | 3232   | 1.08                    |

| $\cosh$               | 91902   | 118138 | 1.29                    |

| diff                  | 20752   | 25512  | 1.23                    |

| eqn                   | 25726   | 29306  | 1.14                    |

| grep                  | 7174    | 9394   | 1.31                    |

| ls                    | 8608    | 10536  | 1.22                    |

| $\mathbf{nroff}$      | 54826   | 71162  | 1.30                    |

| od                    | 7232    | 8560   | 1.18                    |

| $\operatorname{sort}$ | 12194   | 15658  | 1.28                    |

| tee                   | 2800    | 2992   | 1.07                    |

| unpack                | 4936    | 6104   | 1.24                    |

| write                 | 5302    | 6142   | 1.24                    |

| yacc                  | 28909   | 37730  | 1.31                    |

Table 2: Code Size for CISC (MC68020) and RISC (SPARC)

The code expansion is not as great as might be first expected, because the RISC architecture contains the twenty or thirty percent of instructions that the compiler could generate for the CISC architecture, which almost negates the code expansion which might be caused by having only simple instructions. The expansion that does occur is due to the simple (low information density) RISC instructions — to speed up the instruction decode stage. In practice the performance loss caused by the code expansion is outweighed by the performance gains made by decreasing the cycle time and reducing the average number of cycles per instruction.

Optimising compilers also help to mitigate the code expansion in RISC architectures, the simple instruction set means the code sequence for a

given high level language statement is much easier to generate, compared to the complex alternatives a CISC may offer. The simple instructions also offer better opportunities for optimisation, they only perform the actions required, whereas CISC instructions often have useless side effects. Simple instructions allow the compiler to re-order code, to avoid data dependencies and remove code duplication, operations which are of course impossible with fixed microcode sequences. A simple architecture also shortens hardware development time, allowing RISC implementations to utilise the latest hardware technology, and the resulting implementations are much more likely to operate correctly (unlike CISC machines which usually undergo several hardware revisions). The compiler can be continually improved to fully utilise the hardware.

In practice the effect of such streamlining of an architecture is a large performance increase, with a lower hardware cost due to the short development time, resulting in a significant decrease in the price/performance ratio compared to CISC architectures.

# **RISC Development**

In 1975 IBM began a project to "achieve significantly better cost/performance for High Level Language programs than that attainable by existing systems" [Radi82]. The 801 project had pioneering design goals for a computer architecture, which now form the basis of RISC architecture and implementation design decisions —

#### i) maximum utilisation of all sections of the CPU.

A three stage instruction pipeline was designed so that instructions

could take three cycles to execute: the first cycle was used to load the instruction from memory, the next cycle to decode the instruction, read the operands and perform the ALU operation, and the last cycle to perform shift operations, write the result and set the processor flags. Functions that needed a longer time to execute, for instance integer multiplication and division, were handled with a primitive step instruction. Several multiplication step instructions must be executed sequentially to perform a complete multiplication. An effective throughput of one instruction per cycle was realised.

- ii) regular instruction format to simplify the decoding of instructions.

All instructions were made one word (four bytes) long and aligned on a word boundary when stored in memory. Data objects were aligned on a boundary equivalent to their size, bytes on a byte boundary, halfwords on a halfword boundary etc.

- iii) All instruction operands and results stored in registers.

Thirty two registers were used to hold as much data as possible because accessing memory three times (two operands and a result) in each instruction was too slow. A load/store architecture was implemented. The destination register of a data processing instruction was specified independently of its operand registers, unlike earlier architectures which placed the result back into an operand register.

- iv) A fast memory system to supply a new instruction every cycle.

Research showed thirty percent of all executed instructions were loads or stores, and because a new instruction was required in every cycle, a Harvard architecture with separate caches connected to a

common memory was used to provide the required memory bandwidth. The cache had a 32 byte line and a write—back strategy.

#### v) Simple but fast addressing modes.

Only two addressing modes were provided, base register plus immediate index and base register plus register index. The result of the base plus index calculation could be stored back into the base register after each memory access, providing an "auto—increment" facility. Because one cycle was required to calculate the address and another cycle to access the main memory, delayed loads were implemented, so that execution of the following instruction could continue if it did not reference the register into which the load instruction was loading the data. The CPU was "interlocked" — it went into an "idle" state if the register for the new data was referenced before the data was available. The high level language compilers were usually able to re—sequence instructions so that this idle state was rarely used, maintaining the primary goal of one instruction per cycle.

# vi) Branch instructions to enhance the instruction pipeline's efficiency. Delayed branch instructions were implemented to maximise the pipeline efficiency and ordinary (two cycle) branch instructions were implemented to avoid lengthening programs by placing NOP instructions in the branch delay slot.

#### vii) Powerful compilers to utilise the hardware.

The compiler had to be able to make efficient use of the CPU registers, re-order instruction sequences to find instructions to put after the instructions with delayed actions (load and branch) and

provide powerful code optimisation. The PL.8 and Pascal compiler produced for the 801 project pioneered many of the optimising compiler techniques still used today [Ausl82].

The resulting computer was extremely fast, approximately five times faster than machines using comparable hardware technology. Although the 801 CPU was spread across multiple chips, it pioneered the technology for all future single chip RISC designs. It established the principle that the architecture be designed to support the compiler, not trying to second guess the programmer by providing a static set of high level functions in microcode, but provide the low level tools to let the compiler produce simple and efficient code, and utilise the cache to provide a dynamic set of frequently used code sequences.

# Commercial RISC Designs

# Sun Scalable Processor Architecture (SPARC)<sup>TM</sup>

The RISC acronym was actually coined by a research team at Berkeley University in 1980, led by Dr Dave Paterson. The object of the research was to show that Very Large Scale Integration (VLSI) could be exploited to build a small, very fast 32 bit microprocessor on a single chip, eventually named RISC 2 (RISC 1 was an earlier design) [Patt80, Patt81,Patt82, Patt85]. Sun Microsystems Scalable Processor Architecture (SPARC) is an extended version of RISC 2 (an FPU and a different register layout are the major differences).

The constructs used in a wide range of high level language programs were studied to arrive at a suitable set of instructions and addressing modes, as summarized in Table 3. The number of instructions for each high level language construct was based on code produced by compilers for the DEC VAX, DEC PDP 11 and Motorola 68000 architectures.

| Measure     | Occurrence |    | Weighted by # instructions |          | Weighted by # memory refs |       |

|-------------|------------|----|----------------------------|----------|---------------------------|-------|

| Language    | Pascal     | С  | Pascal                     | <u>C</u> | Pascal                    | C     |

| Call/Return | 12         | 12 | 30                         | 33       | 43                        | 45    |

| Loops       | 4          | 3  | 40                         | 32       | 32                        | 26    |

| Assignments | 36         | 38 | 12                         | 13       | 14                        | 15    |

| IF          | 24         | 43 | 11                         | 21       | 7                         | 13    |

| BEGIN       | 20         | _  | 5                          | _        | 2                         | ***** |

| WITH        | 4          | _  | 1                          |          | 1                         | _     |

| CASE        | 1          | 1  | 1                          | 1        | 1                         | 1     |

| GOTO        |            | 3  |                            | 0        | _                         | 0     |

Table 3: Relative Frequency of High Level Language Statements.

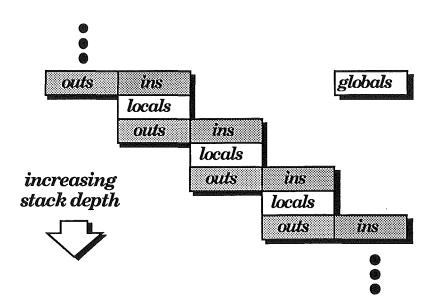

Because memory bandwidth is a performance bottle—neck for a microcomputer CPU, it was desirable to reduce the number of memory references as much as possible. The procedure call and return sequences were particularly memory intensive, because parameters and return values reside on the call stack, which is held in memory. In these designs a very large number of registers (138 on RISC 2, 120 on the first SPARC implementation) are provided on the chip, to make the load/store architecture as efficient as possible by keeping as much of the stack data as possible in registers. All the registers cannot be addressed at once,

because of the large number of bits required to encode a register number, so just thirty two are "visible" at any one time, divided into four groups –

#### i) Global registers

Eight registers (0 to 7) are always "visible" and are used to hold global data. Register 0 always contains zero, and cannot be altered, it is mainly used to simulate a move instruction with an add instruction (one operand is Register 0), or to simulate a compare instruction with a subtract instruction (the destination register is Register 0).

#### ii) "IN" registers.

The next eight registers (8 to 15) are used by a procedure to access its parameters. This is done automatically by the call instruction, see (iv) below.

#### iii) Local registers

These eight registers (16–23) are automatically made unique to each procedure by the call and return instructions. They are used by a procedure to store its local variables.

#### iv) "OUT" registers

The last eight registers (24–31) are used to store the arguments for a procedure call. The "out" registers of the calling procedure are automatically mapped onto the "in" registers of the called procedure when a call instruction is executed, so that parameters that fit in a CPU register do not need to be placed on to the call stack before the call, do not have to be accessed on the stack by the called procedure, and do not have to be removed from the stack after the call. The called procedure may pass data back to the calling procedure (as required

by Pascal's "var" parameters) by putting it in the "in" registers and executing a "return" instruction — the "in" registers will be mapped as the previous procedure's "out" registers..

The registers are arranged in a circular queue, and overlap as shown in Figure 3. A procedure call allocates a new register window, partially overlapping the previous window. The return instruction shifts the window back to reveal the previous procedure's registers. A SPARC implementation may have any number of windows, seven or eight is a typical hardware size/speed tradeoff [Tami83,Wall88]. When the bank is full (the window cannot be advanced any further without overwriting a previous procedure's registers) a trap occurs in the processor and the Operating System must copy the register window to memory. A similar trap occurs if the window is retarded back to the point where register values must be copied back from memory. Programs tend not to have procedure calls more than seven or eight levels deep, so these CPU traps do not occur very often, making the register windows very efficient.

Figure 3: SPARC Register Window Layout

Overall, register windows reduce memory traffic about ten percent, and a program with many procedure calls can have up to a fifty percent memory traffic reduction [Morr88]. Unfortunately, the large number of registers incur two penalties —

- i) The transistors used in the register file must be small to physically fit on the CPU chip. These small transistors cannot drive the ALU bus by themselves (as can the large transistors in a small register file), so must be pre-charged before read operation to overcome the capacitance of the bus. This lengthens the critical CPU data path, thus affecting performance by lengthening the cycle time.

- ii) A considerable proportion of the total chip area is used for registers, this could be used for optimisation of other CPU operations (such as fast multiply and divide hardware, memory management, or a small cache) if another method for optimising register usage could be found.

These penalties indicate register windows are not the best way to lower the memory traffic around procedure calls, good register allocation does nearly as well, and avoids both disadvantages. [Wall88]

SPARC has been used as the CPU and FPU architecture for many SUN high performance microcomputers (workstations) such as the SUN 4/110, SUN 4/260, SPARCstations (currently 3 models), and SPARCservers (at least 6 models) offering performance from six to eighteen VAX Units of Performance (VUPs) [SPEC90]. A DEC VAX 11/780 Minicomputer has one VUP by definition. The high performance of the SUN implementations has been achieved without the help of the best optimising compilers.

# Microprocessor without Interlocked Pipeline Stages (MIPSTM)

This project started in 1981 at Stanford University, using a large research team consisting of both hardware and software (mainly compiler) experts, led by Dr John Hennessey [Henn82, Henn84]. Several architectures were designed and implemented to offer the maximum performance by shifting functionality from the hardware into the compiler, where performance penalties are only incurred at compile time, rather than every time the program is executed. MIPS Computer Systems was formed in 1984 to build a commercial product based on an extended version of the latest Stanford Architecture. Optimising compilers were designed to exploit the architecture, especially the usage of the thirty-two integer and sixteen floating point registers. The optimisations performed by the compiler produced code so superior to the Sun compilers that any performance gain provided by register windows was overshadowed by the speed of the entire MIPS architecture [Morr88]. A five stage instruction pipeline is used to split the execution of each instruction into sections executable in a single cycle. [Kane88]. The MIPS architecture has a number of interesting features -

#### i) No pipeline interlocks.

The architecture has delayed loads and branches, but the pipeline is not interlocked, so instructions placed in the load delay slot will not be able to access the loaded data. The onus is on the compiler to schedule instructions so that pipeline interlocking to support data dependencies (and hence the associated hardware in the processor data path) is unnecessary. This may require the insertion of "nops" into the load delay slots.

## ii) No processor flags.

The architecture does not use the usual method of a single set of processor flags (zero, negative etc) to store the result of compare instructions. Instead the compare instructions (actually labelled SET) store their result in one of the integer registers, and the branch instructions compare the contents of the register to zero (Branch Equal and Branch Not Equal). The condition codes in a normal architecture make some code re—orderings impossible, because any instruction may alter the flags. The MIPS approach allows the result of a comparison to be left in a register so that the compiler may insert any instruction between the compare and branch instructions. Furthermore, the very common Branch and Branch Not Equal operations can test a value in any register, so do not require any explicit comparison instruction.

#### iii) Unaligned word access.

Special instructions in the ALU (Load Word Left and Right) allow data words that are not aligned on a word boundary to be loaded in two instructions (rather than the usual three (two to load the data and one to combine the two parts) plus a load delay slot). These unusual RISC features were deemed important enough by the MIPS designers to justify their inclusion.

#### iv) Integer multiply and divide instructions.

The CPU has multi cycle instructions which perform signed and unsigned 32 bit multiplication yielding a 64 bit result, and a 32 bit division instruction yielding a 32 bit quotient and a 32 bit remainder. These instructions are hardware interlocked, as their execution times are likely to change between implementations, and the same

code has to be supported by all the different implementations. Considerable amounts of CPU chip space were required by these instructions, but again their relative usefulness was enough to justify their inclusion.

#### v) Simplified Floating Point Unit.

The MIPS FPU (housed on a separate chip) also has a reduced instruction set. Add, Subtract, Multiply, Divide, Absolute Value, Move, Negate and Convert to and from integer are the only instructions supported. CISC FPU's usually have Sine, Cosine, Arc Tangent, Polar functions, Exponent and Root functions, which must be implemented in software on a MIPS, extending the RISC philosophy. Communication between the CPU and FPU is via "coprocessor" instructions in the CPU instruction set. The FPU was optimised by hand, a feat no CISC design team could hope to perform, due to the size of a CISC FPU [Rowe88].

#### vi) On chip memory management.

The CPU chip also contains hardware to manage large off-chip caches, and a 64 entry Translation Lookaside Buffer (TLB) of recent virtual to physical address translations. The provision of these functions on the CPU chip makes communication with them very fast, resulting in fast, flexible memory systems.

The MIPS architecture has the best performance of any VLSI architectures(SPEC90]. The removal of considerable amounts of hardware from the critical data path (condition code setting, data dependency interlocks) allows very fast clock rates to be implemented. Optimising compilers exploit the architecture to produce thirty percent more efficient

code (less instructions) than compilers for other RISC architectures [Morr88]. The processor does require a high performance (expensive) memory system, but this will be required by any system of such high performance. The Harvard architecture utilising two caches (one for instructions, the other for data) connected to a common memory allows some control of the price/performance ratio of the architecture by varying the cache size. The R2000 and R3000 are implementations of the MIPS architecture, used in MIPS products with performance from twelve to twenty VUPs, Digital Equipment also use MIPS processors in their DECStation range. The MIPS architecture has been extended to a multiple chip implementation for use in a mini-computer (using a different family of transistor logic) called the R6000, used to produce a 66.7 MegaHertz, 55 VUP machine called the RC6280. This machine has a twin level cache system: the primary level has two virtually addressed, direct mapped, write through caches, 64 Kilobyte for instructions and 16 Kilobyte for data; the secondary cache is physically mapped, two way set associative with write back, and is shared by both instructions and data. It has 512 Kilobytes, and requires an extra cycle to be accessed. This cache system has a 99.5 percent hit rate.

#### Other Commercial RISC Architectures

Several other RISC architectures are currently being used as the CPU for high performance microcomputer systems. Data General Corporation use the Motorola 88000 series chips in their Aviion™ workstation. The 88000 architectures consists of a 88100 CPU and two 88200 Cache and Memory Management Units (CMMUs), one CMMU for instructions, the other for data [Dobb88, Jone88, Jone89, Mele89]. The 88100 architecture has some

instructions to support the emulation of the 680x0 architecture (single cycle bit field manipulation instructions provide the most support).

IBM have developed the Performance Optimisation With Enhanced RISC (POWER) architecture, and this is used in the RISC System/6000 series of workstations. The integer performance of this architecture is similar to other RISC processors, but the floating point performance is very good, approximately twice the performance of competitors' Floating Point Units [IBM90]. The architecture has a separate processor to predict branch destination addresses and to execute branch instructions, to keep the integer and floating point instruction pipelines full.

The AMD29000 architecture is targeted for embedded applications [AMD87, Lehr89]. It has been used as a graphics accelerator in the Apple MacIntosh IIfx<sup>TM</sup> personal workstation [Heid90].

The Systems Performance Evaluation Cooperative (SPEC) have developed a suite of "benchmark" programs, representative of real world computer applications, which can be used to compare the performance of different architectures [SPEC90]. These "SPECmarks" provide useful comparisons between the performance of different architectures, and indicates the MIPS architecture to have the highest performance at a given clock speed. Other RISC architectures have similar performance, while the CISC architectures (of the same generation) achieve around one quarter of the RISC performance.

# Chapter 3

# The Acorn RISC Machine

The Acorn RISC Machine (ARM) is a processor that achieves an excellent price/performance ratio, for different reasons to other RISC processors and implementations, as it offers reasonable performance at a low cost, rather than maximum performance at any cost. [Furb89, VTI89]. The 32 bit architecture is tailored towards low cost applications: inexpensive micro-computers, embedded controllers for laser-printers, graphics accelerators and network adaptors [Cate88, Wils89a]. The architecture has three implementations –

- i) ARM1 (now obsolete, used only in development machines) mentioned only for completeness.

- ii) ARM2, a faster implementation of ARM1 (with added multiply and co-processor instructions).

- iii) ARM3, essentially an ARM2 combined with a cache on a single chip (and an added semaphore instruction) [Wils89b].

The ARM instruction set is shown in Table 4, the instruction format is shown in Appendix A. The architecture has been designed to be coupled with a relatively slow DRAM memory, to avoid a fast (expensive) memory system which would significantly increase the price for the low cost applications ARM was targeted for. Because one new instruction was required from the memory in every clock cycle, the clock cycle time is limited by the instruction transfer time of the memory. The 26 bit address bus (and Program Counter) allow 64 MegaBytes of memory to be directly addressed.

| Function                    | Mnemoni        | c Operation                  | Cycles       |

|-----------------------------|----------------|------------------------------|--------------|

| Data Processing             |                |                              |              |

| Add                         | ADD            | Rd :=Rn + Shift(Rm)          | 18           |

| Add with carry              | ADC            | Rd := Rn + Shift(Rm) + C     | 18           |

| Subtract                    | SUB            | Rd := Rn - Shift(Rm)         | 18           |

| Subtract with Carry         | SBC            | Rd := Rn - Shift(Rm) - 1 + C | 2 1S         |

| Reverse Subtract            | RSB            | Rd := Shift(Rm) - Rn         | 1S           |

| Reverse Subtract with Carry | RSC            | Rd :=Shift(Rm) - Rn - 1+ 0   | 2 1S         |

| And                         | AND            | Rd :=Rn AND Shift(Rm)        | 18           |

| Inclusive OR                | ORR            | Rd :=Rn OR Shift(Rm)         | 1S           |

| Exclusive OR                | EOR            | Rd :=Rn XOR Shift(Rm)        | 1S           |

| Bit Clear                   | BIC            | Rd :=Rn AND NOT Shift(I      | Rm) 1S       |

| Move                        | MOV            | Rd :=Shift(Rm)               | 1S           |

| Move Negative               | MVN            | Rd :=NOT Shift(Rm)           | 1S           |

| Compare                     | CMP            | Rn - Shift(Rm)               | 1S           |

| Compare Negative            | CMN            | Shift(Rm) + Rn               | 1S           |

| Test for Equality           | $\mathbf{TEQ}$ | Rn XOR Shift(Rm)             | 1S           |

| Test Masked                 | TST            | Rn AND Shift(Rm)             | 18           |

| Multiply                    | MUL            | Rd :=Rm x Rs                 | 1S +16I max  |

| Multiply with Accumulate    | MLA            | $Rd := Rm \times Rs + Rn$    | 1S +16I max  |

| Data Transfer               |                |                              |              |

| Load Register (& Byte)      | LDR            | Rd :=Address contents        | 1S + 1N + 1I |

| Store Register. (& Byte)    | STR            | Address contents := Rd       | 2N           |

| Swap Memory & Register (ARI | M3) SWAP       | Rd :=: Address contents      | 2S+1N+1I     |

| Multiple Data Transfer      |                |                              |              |

| Load Multiple               | LDM            | Rlist :=Address contents     | (n-1)S+1N+1I |

| Store Multiple              | STM            | Address contents := Rlist    | (n-1)S+2N    |

|                             |                |                              |              |

Table 4: ARM Instruction Set

| Function               | Mnemoni | c Operation               | Cycles       |

|------------------------|---------|---------------------------|--------------|

| Flow Control           |         |                           |              |

| Branch                 | В       | PC := PC + Offset         | 2S + 1N      |

| Branch with link       | BL      | R14 := PC, PC := PC + Off | set 2S + 1N  |

| Software Interrupt     | SWI     | R14 := PC, PC := Vector # | 2S + 1N      |

| Co-Processor           |         |                           |              |

| CP data processing     | CDP     | CP dependent              | 1S + bI      |

| Move ARM reg to CP reg | MRC     | Rdc := Rm                 | 1S+bI+1C     |

| Move CP reg to ARM reg | MCR     | Rmc := Rd                 | 1S+(b+1)I+1C |

| Load CP register       | LDC     | Rdc := Address contents   | (N-1)S+bI+1C |

| Store CP register      | STC     | Address contents := Rdc   | (N-1)S+bI+1C |

#### **Execution Conditions**

Always (AL), Never(NV): Equal (EQ), Not Equal(NE)

Overflow Set (VS), Overflow Clear (VC): Carry Set (CS), Carry Clear (CC)

Minus (MI), Plus (PL): Higher (HI):Lower or Same(LS)

Greater than (GT), Less than or Equal (LE): Greater than or Equal (GE), Less than (LT)

# **Shift Operations**

Logical Shift Left, Logical Shift Right, Arithmetic Shift Right Rotate Right, Rotate Right with Extend by one bit

# **Key to Cycle Length**

S cycle time is determined by the sequential access speed of the memory

N cycle time is determined by the random access speed of the memory

I cycle time is the processor internal clock speed (usually the same as S)

C cycle time is the co-processor clock speed

n is the number of registers to be saved

b is the number of cycles the processor must wait for the co-processor to be ready

Table 4 (continued): ARM Instruction Set.

#### **Architecture Characteristics**

The type of applications for which the ARM was targeted at resulted in a number of interesting features –

## i) DRAM memory support.

The ARM CPU provides the memory controller with a signal, indicating sequential memory addresses, to utilise fast DRAM access modes. Continuous instruction sequences (i.e. not containing any taken branch instructions) use this signal to achieve over fifty percent more memory bandwidth when coupled to DRAM memory. The cycle times for instructions reflects this, a normal instruction takes one S (sequential) cycle, a branch instruction has one N (non-sequential) cycle to load the first instruction from the branch destination, and two S cycles to load the next two instructions to refill the instruction pipeline. Acorn have designed a memory management chip for the ARM, which uses the sequential signal to access the attached memory and to supply the clock signal to the processor. The memory controller also contains a 128 entry content addressable memory, which is used as a Translation Lookaside Buffer (TLB) for virtual addresses.

## ii) Atypical instruction complexity.

The ARM instruction set is more complex than the IBM 801, SPARC and MIPS architectures, because the CPU was designed to be very memory efficient, to maximize the available memory bandwidth for loading instructions. Most RISC architectures suffer a performance loss due to the low information density of their simple instructions (as shown in Table 3) because more instructions are loaded and

executed in comparison to a CISC architecture. This performance loss is usually outweighed by the performance gain that the fast instruction decode facilitates. The ARM architecture has ten different instruction "families", in comparison to the three or four which is more typical of other RISC architectures.

The elementary instruction pipeline has three stages: fetch, decode and execute. The complexity of the instructions means that each instruction must be substantially decoded before the operand values are known and execution may begin. Reading the operand registers is performed at the start of the execution stage, rather than at the end of the decode stage (which is typical). This lengthens the execution stage, but because the CPU cycle time is limited by the memory speed no performance penalty results.

#### iii) Conditional instructions

All instructions in the ARM architecture contain a condition field, which determines, depending on the values in the processor's condition flags, if the instruction will execute, similar to the way most architectures conditionally execute branch instructions. The sixteen possible conditions are shown in Table 4. Having conditions on all instructions results in better utilisation of the condition code evaluation hardware normally used exclusively for branch instructions, but does require a four bit field in each instruction. Branch instructions are often used to conditionally execute just one or two normal instructions: in ARM code these few instructions can be conditionally executed and the branch instruction (which may stall the CPU to refill the pipeline) can be removed. The setting of the condition codes by arithmetic operations is also optional, making it

possible to preserve the condition codes throughout a sequence of such instructions. Consider the code for a Greatest Common Divisor algorithm, the C code is to find the GCD of a and b (leaving the result in both a and b)

The assembly code for a "normal" architecture would be

```

/* reached the end yet ? */

gcd

cmp

r1, r2

beq

end

blt

bgtra

/* if a is greater than b */

r1,r1,r2 /* subtract b from a */

sub

bal

qcd

/* subtract a from b */

r2, r2, r1

bgtra sub

bal

gcd

end

```

But the assembly for ARM is

```

gcd cmp r1,r2  /* if a is greater than b */

subgt r1,r1,r2 /* subtract b from a */

sublt r2,r2,r1 /* subtract a from b */

bne gcd /* reached the end yet ? */

```

These instructions are particularly useful for range checking – the code for absolute value (of register 1) is

```

abs cmp r1,0 /* test sign */

rsbmi r1,r1,0 /* a:=0-a (two's complement) */

```

The code to replace ASCII control code in register 1 with a "?" is

```

repl cmp r1,127 /* is it a DEL */

cmpne r1," "-1 /* or less than space */

movls r1,'?' /* then replace it */

```

#### iv) No delayed branches.

Branch instructions take three cycles to execute if they jump to a new memory address (i.e. if they really do branch, but only take one cycle if they do not branch). The first of the three cycles is used to execute the branch instruction, the two remaining cycles are needed to reload the instruction pipeline from the branch destination address. To simplify the processor no instructions are executed while the pipeline is reloaded (i.e. the instruction after the branch is not executed as a branch delay instruction). A delayed branch architecture requires two program counters because a trap can occur in the branch delay slot as well as in the branch destination; one PC contains the address of the instruction in the branch delay slot, the other contains the branch destination address. Of course both program counters must be saved when a process switch occurs, which as shown later, would complicate ARM too much to justify the performance gain of delayed branches, so they are not used. Because ARM has a 26 bit address bus a condition code, instruction identifier and a complete memory address can be encoded in a single instruction.

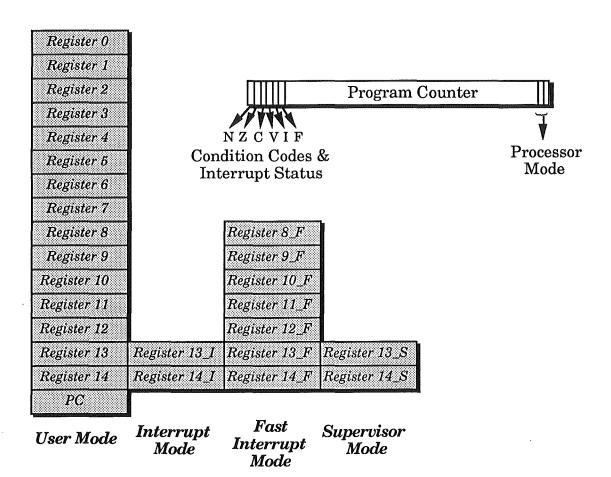

#### v) Uniform register file.