# HIGH PULSE AC/DC CONVERTORS AND THEIR APPLICATION TO HVDC TRANSMISSION

A thesis presented for the degree of

Doctor of Philosophy

in

Electrical and Electronic Engineering

at the

University of Canterbury,

Christchurch,

New Zealand.

by Miguel Villablanca January 1992 ENGINEERING LIBRARY THESIS TK 2796 V712

# Abstract

AC/DC convertors used in HVdc transmission systems inject harmonics into their associated AC and DC systems. A conventional approach to filter these harmonics is to use passive filters on both AC and DC sides of the convertor. Apart from their technical problems, harmonic filters constitute a considerable part of the volume and cost of present DC terminal stations. Another possible alternative of harmonic suppression is to increase the number of pulses of AC/DC convertors by transformer phase-shifting techniques, but the resulting complicated circuitry together with its problems of insulation produce significant technical and economical disadvantages.

In this thesis a novel method of harmonic suppression for HVdc transmission systems is presented. It is a technique producing the same effect as transformer phase-shifting but without complicated circuitry. Moreover, the possibility of increasing the number of pulses of AC/DC convertors to any desired extent is proposed. The concept can be applied to parallel and series connections of convertors. Further applications, other than HVdc transmission, are also suggested.

# Acknowledgements

There are a number of people whom I wish to thank for their contribution to my work. I wish to thank Professor Jos Arrillaga, my supervisor, for suggesting the subject of this thesis and for his help and guidance during this investigation. He has also carefully edited successive drafts of research papers and this thesis. Without Jos's efforts, my work would have been less clearly expressed.

The postgraduate students and staff with whom I have been associated at the University of Canterbury have provided a friendly and stimulating environment in which to work. I would especially like to thank Dr. S. Sankar and my other postgraduate colleagues G. Anderson, J.R. Camacho, D. Gilbert, S. Macdonald, A. Medina, A. Miller, J. de Souza, A. Wood and M. Zavahir.

I would like to thank my father for his encouragement and all the members of my family for their continued support.

Last, but certainly not least, I wish to express my deep appreciation to Monica for her care and patience during the course of my studies.

# List of Publications

Eight papers have been written as a result of this research, and are listed below.

- 1. Arrillaga J., Villablanca M., "A Modified Parallel HVDC Convertor for 24 Pulse Operation", IEEE Trans. on Power Delivery, vol. 6, no. 1, pp. 231-237, January 1991.

- 2. Arrillaga J., Villablanca M., "Pulse doubling in parallel convertor configurations with interphase reactors", IEE Proc., vol. 138, pt. B, no. 1, pp. 15-20, January 1991.

- 3. Arrillaga J., Villablanca M., "24-pulse HVDC conversion", IEE Proc., vol. 138, pt. C, no. 1, pp. 57-64, January 1991.

- Arrillaga J., Villablanca M., Joosten A., "High Pulse Naturally Commutated AC-DC Conversion", Proc. 6th Conference on Power Electronics and Motion Control, vol. 2, pp. 384-388, Budapest, Hungary, October 1990.

- 5. Arrillaga J., Villablanca M., Camacho J.R., "A New Concept in HVDC Generation", accepted for presentation (and publication) in 1992 IPENZ (Institution of Professional Engineers New Zealand) Conference, 16th-19th February, Christchurch, New Zealand.

- 6. Villablanca M., Arrillaga J., "Pulse multiplication in parallel convertors by multitap control of the interphase reactor", IEE Proc., vol. 139, pt. B, no. 1, pp. 13-20, January 1992.

- Villablanca M., Arrillaga J., "High pulse HVDC transmission", accepted for presentation (and publication) in 1992 session of CIGRE, 30th August-5th September, Paris, France.

- 8. Villablanca M., Arrillaga J., "Single-Bridge Unit-Connected HVDC Generation with Increased Pulse Number", accepted for presentation (and publication) in IEEE/PES 1992 Winter Meeting, New York, February 2-6, 1992.

# Contents

| Chapter 1 | Inti | roduction                                             | 1  |

|-----------|------|-------------------------------------------------------|----|

|           | 1.1  | General                                               | 1  |

|           | 1.2  | Main Aims                                             | 2  |

|           | 1.3  | Chapter Presentation                                  | 2  |

| Chapter 2 | Me   | thods of Harmonic Elimination                         | 3  |

|           | 2.1  | Introduction                                          | 3  |

|           | 2.2  | Conventional Methods                                  | 3  |

| *         |      | 2.2.1 Pulse Number Increase                           | 3  |

| •         |      | 2.2.2 Filters                                         | 4  |

|           | 2.3  | Alternative Methods                                   | 5  |

|           |      | 2.3.1 Active Filters for AC Harmonic Suppression      | 5  |

|           |      | 2.3.2 Pulse Width Modulated HVdc Transmission         | 6  |

|           |      | 2.3.3 Harmonic Injection                              | 6  |

|           |      | 2.3.4 DC Ripple Reinjection                           | 6  |

| Chapter 3 | Ger  | neralized Pulse Multiplication in Parallel Convertors | 9  |

|           | 3.1  | Introduction                                          | g  |

|           | 3.2  | General Conditions and Circuit Configuration          | g  |

|           | 3.3  | <u> </u>                                              | ç  |

|           |      | 3.3.1 Derivation of the Output Voltage Waveform       | g  |

|           |      | 3.3.2 Reactor Tap Positions                           | 13 |

|           |      | 3.3.3 Effect of Tap Position Alterations              | 14 |

|           |      | 3.3.4 Conditions for Natural Commutation              | 15 |

|           |      | 3.3.5 Mean Rectified Voltage                          | 17 |

|           |      | 3.3.6 Asymmetrical Effect on Waveform $v_z$           | 18 |

|           | 3.4  | Current Considerations                                | 20 |

|           |      | 3.4.1 Current Analysis on DC Side                     | 20 |

|           |      | 3.4.2 Current Analysis on AC Side                     | 22 |

|           | 3.5  | Design of the Interphase Reactor                      | 24 |

|           |      | 3.5.1 Minimum Load Current                            | 24 |

|           |      | 3.5.2 Magnetising Current Calculation                 | 25 |

|           |      | 3.5.3 Relationship Between $I_{Zmin}$ and $L_B$       | 27 |

|           | 3.6  | Component Ratings                                     | 28 |

|           |      | 3.6.1 Main Thyristors                                 | 28 |

viii

|           |     | 3.6.2 Convertor transformers                          | 29 |

|-----------|-----|-------------------------------------------------------|----|

|           |     | 3.6.3 Reactor Thyristors                              | 30 |

|           |     | 3.6.4 Interphase Reactor                              | 31 |

|           | 3.7 | Experimental Verification                             | 32 |

| Chapter 4 | Ger | neralized Pulse Multiplication in Series Convertors   | 39 |

|           | 4.1 | Introduction                                          | 39 |

|           | 4.2 | General Conditions and Circuit Configuration          | 39 |

| *         | 4.3 | Voltage Considerations                                | 41 |

|           |     | 4.3.1 Derivation of the Output Voltage Waveform       | 41 |

|           |     | 4.3.2 Feedback Transformers Turns Ratio               | 44 |

|           |     | 4.3.3 Turn Ratio Alterations of Feedback Transformers | 44 |

|           |     | 4.3.4 Conditions for Natural Commutation              | 45 |

|           |     | 4.3.5 Mean Rectified Voltage                          | 47 |

|           |     | 4.3.6 Asymmetrical Effect on Waveform $v_z$           | 49 |

|           | 4.4 | Derivation of Current Waveforms                       | 51 |

|           |     | 4.4.1 Current Analysis on DC Side                     | 51 |

|           |     | 4.4.2 Current Analysis on AC Side                     | 52 |

|           | 4.5 | The Feedback Transformers                             | 57 |

|           |     | 4.5.1 Minimum Load Current                            | 57 |

|           |     | 4.5.2 Magnetising Current Calculation                 | 58 |

|           |     | 4.5.3 Relationship Between $I_{Zmin}$ and $L_B$       | 60 |

|           | 4.6 | The Blocking Capacitors                               | 61 |

|           | 1.0 | 4.6.1 Voltage and Current Waveforms of Capacitors     | 61 |

|           |     | 4.6.2 Distortion of the Output Voltage                | 62 |

|           |     | 4.6.3 Selection of Capacitance                        | 63 |

|           | 4.7 |                                                       | 64 |

|           | 7.1 | 4.7.1 Main Thyristors Currents                        | 64 |

|           |     | 4.7.2 Main Transformer Currents                       | 65 |

|           |     | 4.7.3 Feedback Thyristors                             | 66 |

|           |     | 4.7.4 Blocking Capacitors                             | 68 |

|           |     | 4.7.5 Feedback Transformers                           | 69 |

|           | 4.8 | Experimental Verification                             | 70 |

| <b></b>   | _   |                                                       |    |

| Chapter 5 | Des | sign of Physical Scaled-Down Model                    | 79 |

|           | 5.1 | Introduction                                          | 79 |

|           | 5.2 | The Power Switching Devices                           | 79 |

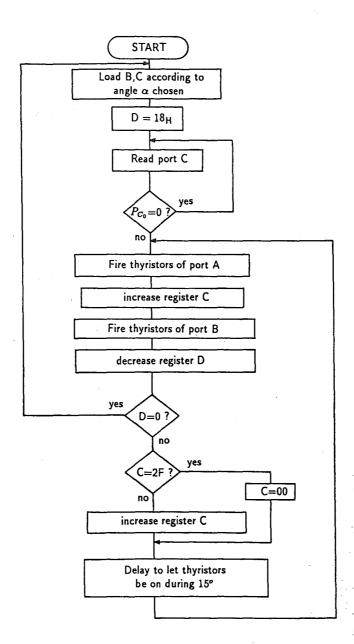

|           | 5.3 | The Convertor Controller                              | 80 |

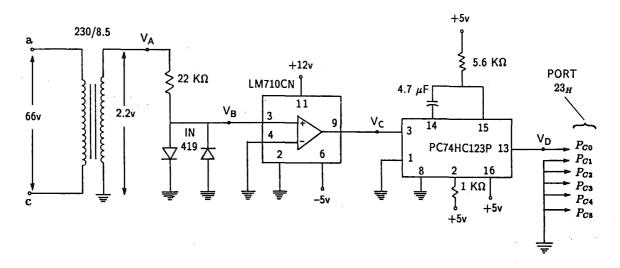

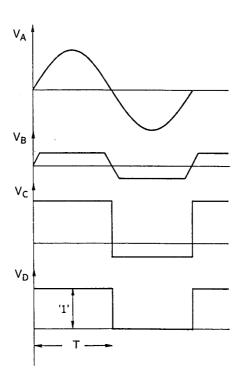

|           |     | 5.3.1 Synchronisation with Power System               | 82 |

|           |     | 5.3.2 Convertor Controller Software                   | 83 |

| Chapter 6 | App | plications to HVdc Transmission                       | 89 |

|           | 6.1 | Introduction                                          | 89 |

|           | 6.2 | Potential Benefit of the Reinjection Technique        | 89 |

|           |     | 6.2.1 Design                                          | 89 |

|           |     | 6.2.2 Compactness                                     | 90 |

| CONTENTS  |                                                           | ix |

|-----------|-----------------------------------------------------------|----|

|           | 6.2.3 Reliability                                         | 90 |

|           | 6.2.4 Reactive Power Requirements                         | 91 |

|           | 6.3 Unit Connected Schemes                                | 91 |

|           | 6.3.1 Modified Unit-Connected Schemes                     | 92 |

|           | 6.4 Conclusions                                           | 93 |

| Chapter 7 | Conclusions                                               | 95 |

|           | 7.1 Suggestions for Further Research in HVdc Transmission | 95 |

|           | 7.2 Suggestions for Further Research in Other Areas       | 96 |

|           | References                                                | 99 |

# Chapter 1

# Introduction

#### 1.1 General

In recent years there has been a significant increase of interest in HVdc transmission. This increased interest results from economic, functional and environmental advantages offered by an HVdc system [Arrillaga, 1983; Breuer et al., 1984].

Clearly it has not been easy for the HVdc technology to reach its present status. Throughout its development innumerable technical problems have been overcome. One of them, of a very complicated nature, is the limitation of the harmonics generated by the convertor. That subject constitutes the main topic of this research project.

From the early days of HVdc technology, filters have been a basic component in all HVdc installations. Apart from their considerable cost and complex design, filters often create their own harmonic problems reported in several contributions [Andersen et al., 1985; Stanley et al., 1977; Campos Barros, 1989].

There have been several attempts to achieve harmonic control by alternative means and one of them, the DC ripple reinjection technique, is investigated further in this work. This technique was first proposed in the late 1970's and basically allowed to operate a single bridge as a twelve-pulse convertor. This present research project has developed the technique to a stage where it is now possible to obtain any desired pulse and step multiplication on the AC and DC sides of the convertor respectively. This is achieved by natural commutation and is equally valid for rectification and inversion. In addition, the convertors can be connected in either series (high voltage applications) or parallel (high current applications) as required by conventional HVdc transmission systems (point-to-point and back-to-back respectively). A 2kW laboratory model has been specially designed to verify the theoretical waveforms and a complete set of experimental results is given in Chapters 3 and 4.

Applications of the DC ripple reinjection concept are mostly dedicated in this thesis to HVdc transmission systems. The absence of filters is likely to simplify the design and improve the transient performance of conventional and unit connected HVdc schemes. The concept, however, is an innovative approach to accomplishing AC/DC conversion and is expected to have important effects in other areas.

#### 1.2 Main Aims

The main objectives of the thesis are:

- 1. To present a general formulation of the DC ripple reinjection technique so that high pulse AC/DC convertors can be achieved with the possibility of connecting them in series or parallel.

- 2. To develop a flexible experimental model capable of representing alternative convertor designs.

- 3. To explore the capabilities of the technique to become a real alternative to the use of pasive filters in HVdc transmission systems.

#### 1.3 Chapter Presentation

The material studied in this research project is organized as follows:

Chapter 2 briefly reviews conventional and alternative methods of harmonic suppression applicable to HVdc transmission systems. It shows that several attempts have been made to find suitable alternatives to filters, however, no alternative so far put forward copes with the problem satisfactorily in all its complexities.

Chapters 3 and 4 present the so called 'DC ripple reinjection technique' and its application to parallel and series connection of convertors respectively. A rigorous mathematical treatment is included together with comprehensive experimental verification.

Chapter 5 considers the design of a laboratory model to verify the principles involved in the DC ripple reinjection technique. This was built with sufficient flexibility to investigate different (parallel and series) configurations up to a maximum pulse number of 48. A detailed description of the hardware involved is given. Although the software is described with reference to 24-pulse operation, enough information is given for its extension to other pulse numbers.

Chapter 6 shows that the HVdc field is a promising area for the application of the DC ripple reinjection technique. Conventional (back-to-back and point-to-point) HVdc schemes as well as unit connected schemes are shown to benefit from the use of this technique.

Chapter 7, finally, presents the major conclusions reached by the present research project. Further research is suggested in both HVdc transmission and other areas.

### Methods of Harmonic Elimination

#### 2.1 Introduction

HVdc convertor stations are normally designed for 12-pulse operation and consist of one or more groups of two series-connected bridges with 30° phase-shifted transformers. Such a 12-pulse convertor arrangement is a source of voltage harmonics of the order 12n (n = 1, 2, 3...) on the DC side and a source of current harmonics of the order  $12n \pm 1$  (n = 1, 2, 3...) on the AC side. The amplitudes of the harmonics decrease with increasing order: the AC harmonic current of order h is less than  $I_1/h$ , where  $I_1$  is the amplitude of the fundamental current.

The necessity of preventing these harmonics from flowing through the AC and DC networks is due mainly to the degradation of telephone communications caused by induced harmonic noise. In addition, these harmonics on the AC side result in overheating and extra losses in electric machines and capacitors in the AC system, and overvoltage due to excited resonances. These effects may not be confined to the vicinity of the convertor station but may be propagated over great distances. The most difficult of these to eliminate is the telephone interference. The conventional approach to filter these harmonics is to use passive filters on both AC and DC sides of the convertor [Arrillaga, 1983; Kimbark, 1971].

In the following, different methods of harmonic suppression are presented. They can be divided in two groups; 1) conventional methods and 2) alternative methods.

#### 2.2 Conventional Methods

There are two widely used means of diminishing the harmonic output of convertors, namely increase of pulse number and installation of filters. Any solution wich increases the pulse number, reduces the harmonic orders penetrating into both sides of the convertor and should be fully exploited. Beyond the economic range of higher pulse configurations, harmonic elimination will normally require the use of filters [Arrillaga, 1983].

#### 2.2.1 Pulse Number Increase

The relationship between pulse number and harmonic order indicates that the higher the pulse number, the higher the frequency of the lowest order harmonic produced. The use

of increased pulse numbers, however, has the following disadvantages [Arrillaga, 1983]:

- Increased levels of lower order harmonics when convertors are temporarily out of service during maintenance.

- Increased number of transformers, both in service and spares.

- Increased complexity of transformer connections and the consequent problems of insulation.

- At higher pulse numbers the harmonic cancellation becomes more dependent on unbalances and distortion of the supply voltage as well as on the precision of the phase-shifting of the transformers.

In high voltage convertors such as those used in HVdc transmission, the insulation problem dictates simple transformer connections. A pulse number of 12, easily obtained by star and delta transformer connections, has been accepted as the building block of modern HVdc transmission systems. Any further harmonic suppression is carried out by making extensive use of passive filters which is explained next.

#### 2.2.2 Filters

Any necessary reduction in harmonic distortion of the convertor beyond that accomplished by the increased pulse number is normally achieved by harmonic filters.

The passive filter approach, however, has some limitations as follows [Arrillaga, 1983; Kimbark, 1971; Duke et al., 1990; Stephen et al., 1991; Wong et al., 1989]:

- 1. The filtering is incomplete due to the fact that the network impedance at harmonic frequencies may not be much greater than that of the filter impedance. As a result, the filtering may not be satisfactory.

- 2. In practice a filter is not always tuned exactly to the frequency of the harmonic that it is intended to suppress for the following reasons:

- Variations of the power system frequency, which result in proportional changes in the harmonic frequency.

- Changes in the inductance and capacitance of the filter due to ageing and temperature variations.

- The accuracy of the actual tuning is restricted by the discrete nature of tuning steps.

- 3. Filters occupy a large area and their cost is a significant portion of the cost of the HVdc terminal.

In addition to these drawbacks, the passive filters on the AC side have further limitations:

- 4. Passive filters are non-selective, so they not only filter out the unwanted harmonic components from the supply they are installed on, but they also serve as a 'sink' for the distortion components produced by other consumers in the vicinity.

- 5. Filters, while meeting the harmonic criteria, generate excessive reactive power at light loads, which in turn gives rise to undesirable overvoltages.

#### 2.3 Alternative Methods

Apart from their considerable cost and complexity, filters often create their own harmonic problems and tend to delay convertor recoveries following large disturbances. Also, effective filter design is still a complex process, mostly because the system impedance is part of the design criteria, which does not occur with the alternative methods.

There have been several attempts to achieve harmonic control by alternative means which is explained in the following subsections.

#### 2.3.1 Active Filters for AC Harmonic Suppression

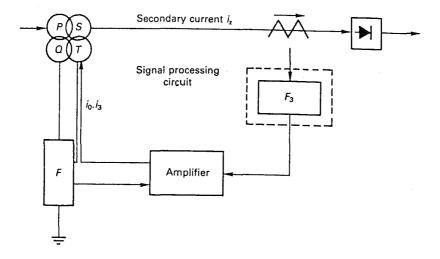

This method of harmonic elimination is basically illustrated in Figure 2.1. A current transformer is used to detect the harmonic components coming from the non-linear load which are then controlled in magnitude, frequency and phase. These are injected through an amplifier, into the tertiary winding of a transformer in such a manner as to cause cancellation of the harmonic currents concerned. Such harmonic currents need to be injected into the AC system through proper means.

The main areas of concern with this system involve the coupling of the output of the amplifier to the tertiary winding in such a way that the fundamental current flow does not damage the amplifier. A quaternary winding and filter are used, as shown in Figure 2.1, to reduce the fundamental current in the amplifier output.

One advantage with this scheme is its ability to take account of uncharacteristic harmonics, such as the third and ninth. The main disadvantage of the scheme is its inability to effectively remove the large magnitude lower order characteristic harmonics without the need for a very high power feedback amplifier.

Figure 2.1 Basic configuration of an active filter.

The concept of injecting harmonic currents for AC harmonic suppression is not new [Sasaki and Machida, 1971]. An improved and more practical means for generating and injecting the characteristic harmonic currents for large power convertors has been already presented [Herfurth, 1986]. The possibility of including power factor correction by phase-shifting a derived fundamental sinusoid has also been proposed [Duke et al., 1990].

#### 2.3.2 Pulse Width Modulated HVdc Transmission

The advances of high power, high frequency, solid-state switches with gate "turn-off" capability (GTO's) have encouraged research and development in the PWM generation of HVdc [Ooi et al., 1991]. This is following the remarkable advances of the pulse width modulation (PWM) technique in the motor-drive industries.

The challenge is to perfect the PWM technique to handle hundreds of KV and thousands of MVA. HVdc transmission systems, however, require higher reliability standards than motor drive systems, thus any further examination of the PWM tecnique in this area must consider its behaviour under transient conditions. This is not to imply that the technique must track transient changes in harmonic patterns, but rather that its response to system disturbances must be understood and controlled. Costs and losses of GTO convertors is another concern and the reduction of them is of prime importance in expanding the application of the PWM technique to HVdc transmission systems [Yamada et al., 1990].

#### 2.3.3 Harmonic Injection

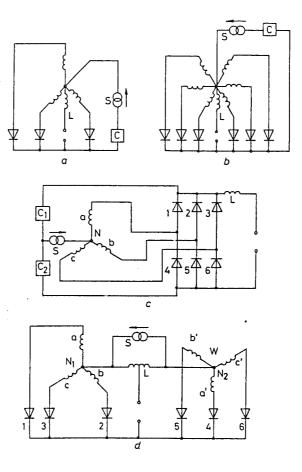

Another means by which harmonics can be eliminated is to modify the convertor rectangular current waveform by adding a harmonic current from an external source, as shown in Figure 2.2. In such a scheme, as originally proposed by Bird [1969] and further developed by Ametani [1972], a triplen harmonic from the source is injected in the conducting transformer phases.

The following disadvantages of this method can be outlined:

- 1. need of a triplen harmonic current generator and its synchronisation to the supply main frequency.

- 2. difficulty in adjusting the amplitude and phase of the sinusoidal injected current to suit each particular operating condition.

- 3. restriction in the amount of harmonic suppression.

- 4. poor efficiency due to ineffective dissipation of the triplen harmonic power injected.

- 5. the passive system proposed by Bird although solving (1) and (2) above is only applicable to rectifiers operating with 0° delay.

#### 2.3.4 DC Ripple Reinjection

A technique, producing the same effect as transformer phase-shifting and referred to as DC ripple reinjection, was proposed in the late 1970's and basically allowed the operation of a single bridge as a twelve-pulse convertor [Baird and Arrillaga, 1979; Baird and Arrillaga, 1980]. However, such technique did not find favour in conventional HVdc schemes, because their power ratings are normally high enough to require several transformers and convertor groups; these groups can then be arranged in twelve-pulse pairs at relatively low cost.

That pioneering work, however, set the foundations for the generalization of the technique attempted in this thesis, a concept that is expected to play an important role in the design of future HVdc systems. As will be shown in the following chapters, the DC ripple reinjection technique overcomes all the disadvantages present in the previous alternative methods and probably it is the most challenging alternative to the traditional practice of harmonic suppression by passive filters.

L = smoothing or interphase reactor N = neutral point S = injected current source C = cutoff circuit for direct current

Classical harmonic injection with various configurations.

a) 3-phase half-wave rectifier

b) Diametrical rectifier

c) 3-phase bridge rectifier

d) 6-phase double-star rectifier Figure 2.2

# Generalized Pulse Multiplication in Parallel Convertors

#### 3.1 Introduction

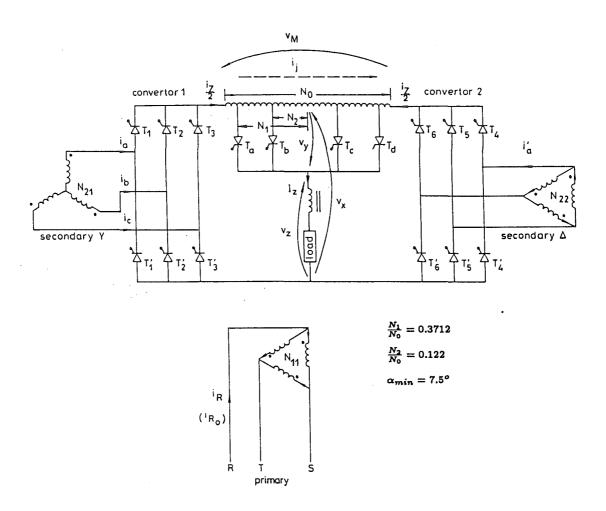

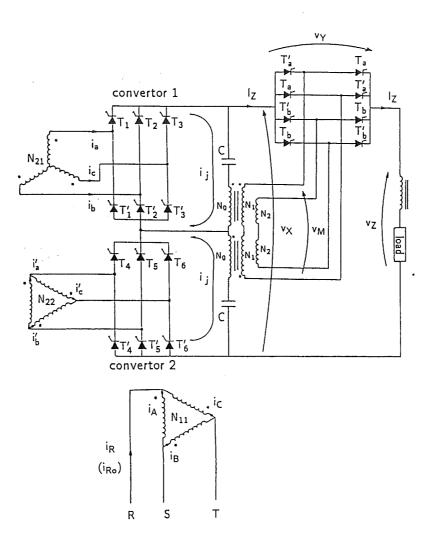

Traditionally the idea of AC/DC convertors with pulse number higher than 12 has always been associated with complicated transformer connections. A novel concept, so called 'DC ripple reinjection technique', has been developed at this University by which AC/DC convertors with any desired number of pulses can be obtained without complicated circuitry. The application of the concept to parallel connection of convertors is given in this chapter. A rigorous analysis of the general configuration shown in Figure 3.1 is included. This analysis, provides general formulas and diagrams that permit a straight-forward design of high-pulse parallel-connected convertors, giving in addition a clear understanding of the principles involved. A complete set of experimental results is given at the end of this chapter that validates thoroughly the concept.

#### 3.2 General Conditions and Circuit Configuration

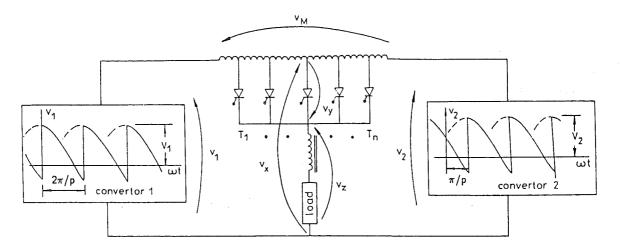

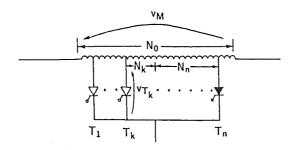

Figure 3.1 shows a general diagram of the proposed multipulse convertor. The average output voltages of the two convertors are the same but their waveforms are displaced by an angle  $\pi/p$ , where p is the pulse number of each convertor. As will be shown, appropriate firings of the additional feedback thyristors  $T_1, ..., T_n$  permit the establishment of a variable  $v_y$ , which if added to the conventional variable  $v_x$ , increases the pulse number of the output variable  $v_z$  in proportion to the number of controlable taps on the interphase reactor. A corresponding increase of current steps modifies the AC current on the AC system side.

#### 3.3 Voltage Considerations

#### 3.3.1 Derivation of the Output Voltage Waveform

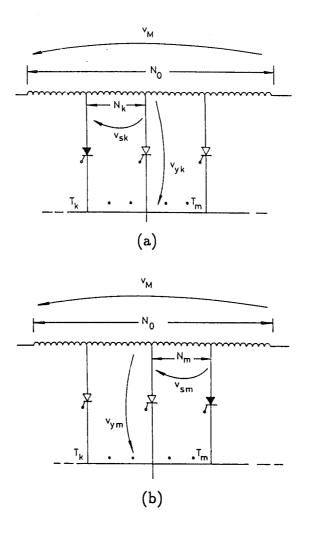

Figure 3.2 shows the effect of firing  $T_k$  and  $T_m$  on the variable  $v_y$ . When any left group thyristor conducts

$$v_{sk} = \frac{N_k}{N_0} v_M$$

Figure 3.1 Multi-pulse convertor configuration.

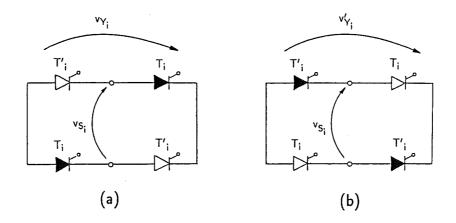

Figure 3.2 Voltage  $v_Y$  composition. a) When  $T_k$  conducts b) When  $T_m$  conducts

then

$$v_{yk} = v_{sk} = \frac{N_k}{N_0} v_M \tag{3.1}$$

And when any right group thyristor conducts

$$v_{sm} = \frac{N_m}{N_0} v_M$$

then

$$v_{ym} = -v_{sm} = -\frac{N_m}{N_0} v_M \tag{3.2}$$

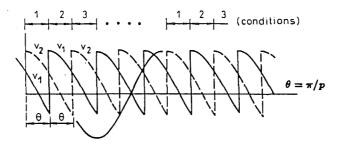

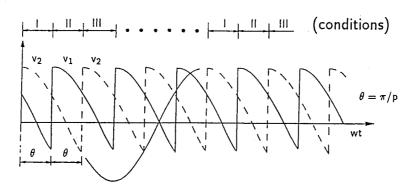

Figure 3.3 shows the successive circuit conditions of both convertors 1 and 2 caused by the alternating changes of the conducting state. Figure 3.3 also shows that the same circuit condition is repeated every  $2\pi$  radians so that the number of different circuit conditions is  $2\pi/\theta = 2p$ .

Figure 3.3 Successive circuit conditions of convertors 1 and 2.

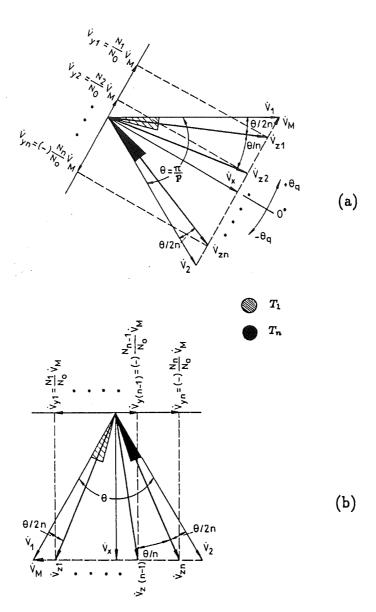

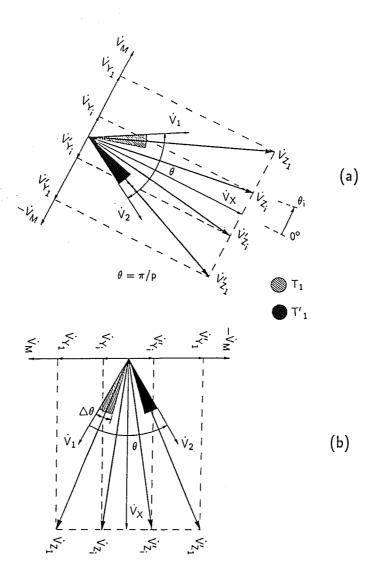

Figure 3.4a shows the phasor diagram corresponding to condition 1 where  $\dot{V}_2$  lags  $\dot{V}_1$  by  $\theta$ . Condition 2 is shown in Figure 3.4b, where  $\dot{V}_2$  is in phase with the previous diagram whereas  $\dot{V}_1$ , displaced by  $2\theta$ , lags  $\dot{V}_2$  by  $\theta$ . The rest of the circuit conditions can be represented in a similar way. The diagrams of Figure 3.4 also include phasors  $\dot{V}_M$ ,  $\dot{V}_x$ ,  $\dot{V}_{yq}$ ,  $\dot{V}_{zq}$ , where, from Figure 3.1

$$\dot{V}_M = \dot{V}_1 - \dot{V}_2 \tag{3.3}$$

$$\dot{V}_x = \frac{\dot{V}_1 + \dot{V}_2}{2} \tag{3.4}$$

$$\dot{V}_{zq} = \dot{V}_x + \dot{V}_{yq} \tag{3.5}$$

with  $\dot{V}_{uq}$  defined in equations 3.1 and 3.2.

For a critical turns ratio  $N_q/N_0$ , the waveform of the output voltage  $v_z$  becomes a sequence of sine-wave portions, which by an appropriate selection of the firing angle of the feedback thyristors can be modified to yield the required shape and value.

For simplicity Figure 3.4 only shows (shaded and dark areas) the conduction pattern of thyristors  $T_1$  and  $T_n$  respectively. The angle of conduction of any feedback thyristor is  $\theta/n$  which is also the duration of each sine-wave portion.

Figure 3.4 Diagrams with reference to Figure 3.3.

a) Circuit condition 1

b) Circuit condition 2

Therefore the pulse number  $p_z$  of the output voltage  $v_z$  for each cycle of the supply system voltage is given by

$$p_z = \frac{2\pi}{\theta/n}$$

But because  $\theta = \pi/p$ , then

$$p_z = 2pn \tag{3.6}$$

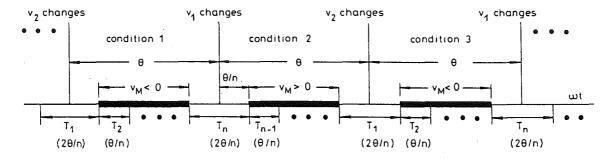

The conduction pattern of the feedback thyristors is clarified in the time diagram of Figure 3.5 where the following rule can be stated for the triggering co-ordination of the feedback thyristors and the main thyristors of convertors 1 and 2.

Every change of conducting state in convertor 2 must be followed by a sequential turnon of the feedback thyristors from  $T_2$  to  $T_n$ . The same applies for convertor 1 except that the triggering order is from  $T_{n-1}$  to  $T_1$ . The interval between sequential firings is  $\theta/n$ .

Figure 3.5 General triggering co-ordination.

#### 3.3.2 Reactor Tap Positions

In Figure 3.4a,  $\theta_q$  defines the position of phasors  $\dot{V}_{zq}$  through the following equation:

$$\theta_q = \frac{\theta}{2n}(n+1-2q) \quad q = 1, ..., n$$

(3.7)

From equations 3.1 and 3.2 (where  $V_M$ ,  $V_{yq}$ ,  $V_x$  and  $V_1$  are maximum values)

$$\frac{N_q}{N_0} = \frac{V_{yq}}{V_M} \tag{3.8}$$

From Figure 3.4a

$$V_{yq} = V_x \tan|\theta_q| \tag{3.9}$$

$$V_x = V_1 \cos(\theta/2) \tag{3.10}$$

$$V_M = 2V_1 \sin(\theta/2) \tag{3.11}$$

From equations 3.7-3.11

$$rac{N_q}{N_0} = rac{ an | heta_q|}{2 \ an( heta/2)} \ ; \ heta = \pi/p$$

then

$$\frac{N_q}{N_0} = \frac{\tan\left|\frac{\pi}{2np}(n+1-2q)\right|}{2\tan(\pi/2p)} \qquad q = 1, 2, ..., n$$

(3.12)

where:

n : Total feedback thyristors

p : Pulse number of convertors 1 and 2

$N_q/N_0$ : Relative tap position of thyristor q

#### 3.3.3 Effect of Tap Position Alterations

The exact tap position expressed in equation 3.12 cannot be implemented in a practical situation and the effect of the deviation from that value will be now examined.

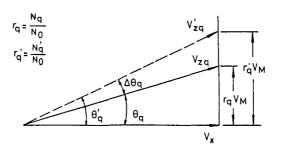

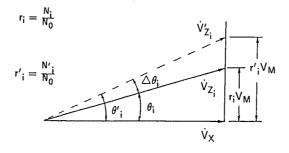

With reference to Figure 3.4a, Figure 3.6 illustrate the angular displacement of phasor  $\dot{V}_{zq}$  ( $\Delta\theta_q$ ) when its tap position is altered. Then the respective angular displacement

$$an heta_q' = rac{r_q' V_M}{V_x}$$

$$an heta_q = rac{r_q V_M}{V_x}$$

$$\frac{\tan\theta_q'}{\tan\theta_q} = \frac{r_q'}{r_q}$$

then

$$\Delta \theta_q = \theta_q' - \theta_q = \tan^{-1} \left( \frac{r_q'}{r_q} \tan \theta_q \right) - \theta_q \tag{3.13}$$

With  $\theta_q$  and  $r_q$  defined in equations 3.7 and 3.12 respectively.

From Figure 3.4a,  $\triangle \theta_q$  must be compared with  $\theta/n$  to appreciate the effect of modifying  $r_q$ .

Figure 3.6 Angular effect of tap position alterations.

This effect is illustrated in Table 3.1 with reference to two simple examples, both using the same reactor and a tap position of 0.25. The asymmetry is not seen to be significant and in most cases only the second digit in equation 3.12 is important.

|          | P                | n | $r_1 = \frac{N_1}{N_0}$ | $r_1' = \frac{N_1'}{N_0}$ | Δθ1    | θ/n  | Δθ <sub>1</sub> % |

|----------|------------------|---|-------------------------|---------------------------|--------|------|-------------------|

| (Case 1) | <sub>3</sub> (*) | 2 | 0.232                   | 0.25                      | 1.105° | 30 ° | 3.68 %            |

| (Case 2) | 6(**)            | 2 | 0.246                   | 0.25                      | 0.12°  | 15 ° | 0.8 %             |

- (\*) Convertors 1 and 2 are half-wave circuits

- (\*\*) Convertors 1 and 2 are bridge circuits

Table 3.1 Example of turn ratio deviation.

#### 3.3.4 Conditions for Natural Commutation

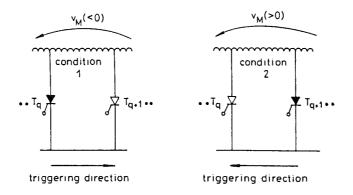

The appropriate polarities of  $v_M$  (i.e.  $v_1 - v_2$ ) that will enable the incoming thyristor to turn on by natural commutation are shown in Figure 3.7.

Figure 3.7 Natural commutation conditions.

From Figures 3.3 and 3.5 it is clear that the conditions of  $v_M$  in Figure 3.7 are easily satisfied. However there are some restrictions for  $\alpha$  close to zero.

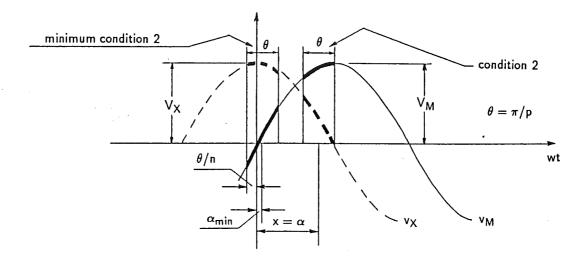

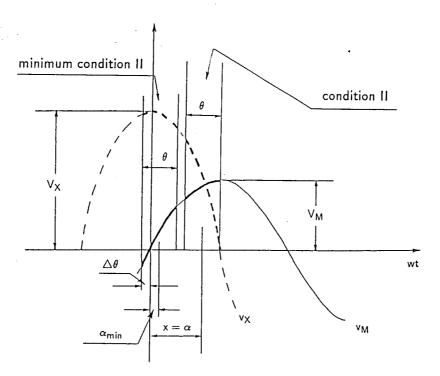

Figures 3.4b and 3.8 illustrate the behaviour of  $v_M$  and  $v_x$  for the specific condition 2 and x defines the location, along the respective sinusoids, of  $v_M$  and  $v_x$ . It is obvious that

$x = \alpha$  considering that waveform  $v_x$  is at a maximum when  $x = 0^o$ .

The minimum condition 2 illustrated in Figure 3.8 permits to calculate the angle  $\alpha_{MIN}$  that satisfies the restriction for  $v_M$  in Figure 3.5.

That is

$$\alpha_{MIN} = \frac{\theta}{2} - \frac{\theta}{n} \tag{3.14}$$

Equation 3.14 indicates that a fully uncontrolled circuit using the DC ripple reinjection concept is possible, but that alternative is limited to the use of only two thyristors as taps of the interphase reactor as in that case  $\alpha = 0^{\circ}$ .

Figure 3.8 Minimum condition for  $\alpha$ .

Figure 3.9 Output voltage of any convertor.

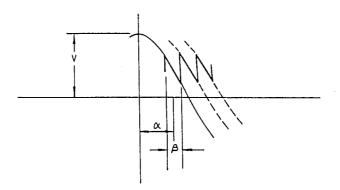

#### 3.3.5 Mean Rectified Voltage

Figure 3.9 shows the generic output waveform of any convertor. The mean rectified voltage  $V_{DC}$  of that waveform is

$$V_{DC} = \frac{1}{\beta} \int_{\alpha - \beta/2}^{\alpha + \beta/2} V \cos wt \, d(wt) = \frac{2V}{\beta} \sin \frac{\beta}{2} \cos \alpha \tag{3.15}$$

Applying equation 3.15 to the conventional configuration yields

$$V = V_x$$

$$\beta = \theta$$

$$V_{XDC} = \frac{2V_x}{\theta} \sin \frac{\theta}{2} \cos \alpha \tag{3.16}$$

and in the case of the modified configuration

$$V = V_z$$

$$\beta = \theta/n$$

$$V_{ZDC} = \frac{2nV_z}{\theta} \sin \frac{\theta}{2n} \cos \alpha \tag{3.17}$$

The increased mean rectified voltage  $\triangle V_{DC}$  is

$$\Delta V_{DC} = \frac{V_{ZDC} - V_{XDC}}{V_{XDC}} = \frac{V_{ZDC}}{V_{XDC}} - 1 \tag{3.18}$$

and substituting equations 3.16 and 3.17

$$\frac{V_{ZDC}}{V_{XDC}} = \frac{nV_z \sin \theta / 2n}{V_x \sin \theta / 2} \tag{3.19}$$

Observing an equal length of phasors  $\dot{V}_z$  in Figure 3.4

$$V_z = V_{z1} = V_{zn} = \frac{V_x}{\cos\left(\frac{\theta}{2} - \frac{\theta}{2n}\right)}$$

(3.20)

Then

$$\frac{V_z}{V_x} = \frac{1}{\cos\left(\frac{\theta}{2} - \frac{\theta}{2n}\right)} \tag{3.21}$$

Finally combining equations 3.18, 3.19 and 3.21

$$\Delta V_{DC}\% = \left[\frac{n\sin\theta/2n}{\sin\theta/2\cos\left(\frac{\theta}{2} - \frac{\theta}{2n}\right)} - 1\right] 100 \tag{3.22}$$

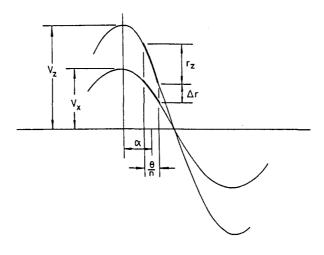

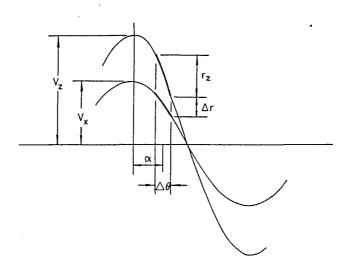

#### 3.3.6 Asymmetrical Effect on Waveform $v_z$

Although the AC current is well behaved for any value of n, from the point of view of  $v_z$  two cases need to be considered:

- (a) n=2: The pulse multiplication is perfect as phasors  $\dot{V}_{zq}$  in Figure 3.4a have the same length and there is no restriction for  $\alpha$  as  $\alpha_{MIN}=0$  in equation 3.14.

- (b)  $n \geq 3$ : Comparing phasors  $\dot{V}_z$  and  $\dot{V}_x$  in Figure 3.4, or the corresponding waveforms in Figure 3.10, it clearly shows the presence of a ripple increase  $\triangle r$  which becomes zero as  $\alpha$  approaches 90° and is defined as follows:

$$\triangle r = (V_z - V_x)\cos(\alpha + \theta/2n)$$

for  $\alpha \le (\pi/2 - \theta/2n)$

$$\Delta r = 0 \qquad \text{for } (\pi/2 - \theta/2n) \le \alpha \le (\pi/2 + \theta/2n) \tag{3.23}$$

$$\triangle r = (V_x - V_z)\cos(\alpha - \theta/2n)$$

for  $\alpha \ge (\pi/2 + \theta/2n)$

and

$$r_Z = V_z[\cos(\alpha - \theta/2n) - \cos(\alpha + \theta/2n)]$$

$$r_Z = 2V_z \sin \alpha \sin(\theta/2n)$$

for  $\theta/2n \le \alpha \le (\pi - \theta/2n)$  (3.24)

where  $V_x$  and  $V_z$  are defined in equations 3.10 and 3.20, respectively.

Figure 3.10 Illustration of ripple increase.

The ripple increase indicated in equation 3.23 is valid only if n is odd, as in that case the smallest vector in Figure 3.4 is  $\dot{V}_x$ . When the smallest vector is not in the middle point but displaced by an angle  $\theta/2n$  (position of thyristor q=n/2 in equation 3.7),  $V_x$  must be replaced by  $V_x/\cos(\theta/2n)$  in equation 3.23.

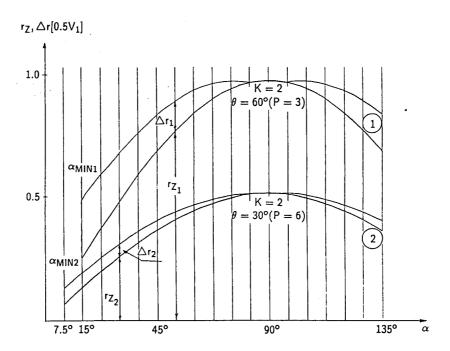

Two cases are illustrated in Figure 3.11 for 24-pulse and 48-pulse configurations.

Figure 3.11 Two examples of ripple increase.

#### 3.4 Current Considerations

#### 3.4.1 Current Analysis on DC Side

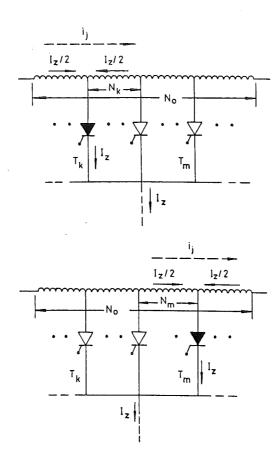

In Figure 3.12  $I_z/2$  and  $I_z$  are the currents produced by the conventional configuration where the DC output is derived from the centre point of the reactor. The superimposed current  $i_j$  represents the effect of connecting the output terminal to alternative taps of the reactor, thus establishing an effective MMF balance.

Figure 3.12 Currents in reactor.

With reference to Figure 3.12, the behaviour of the current  $i_j$  is now considered under the assumption that  $I_Z$  is perfectly smooth.

Equalising ampere-turns, when any left group thyristor conducts

$$(I_Z/2 + i_j)(N_0/2 - N_k) = (I_Z/2 - i_j)(N_0/2 + N_k)$$

$$-\frac{I_Z}{2}N_k + i_j\frac{N_0}{2} = \frac{I_Z}{2}N_k - i_j\frac{N_0}{2}$$

and

$$i_j = \frac{N_k}{N_0} I_Z$$

Similarly when any right group thyristor conducts

$$(I_Z/2 + i_j)(N_0/2 + N_m) = (I_Z/2 - i_j)(N_0/2 - N_m)$$

$rac{I_Z}{2}N_m + i_jrac{N_0}{2} = -rac{I_Z}{2}N_m - i_jrac{N_0}{2}$

and

$$i_j = -\frac{N_m}{N_0} I_Z$$

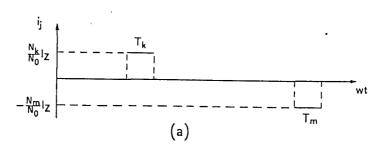

The construction and general waveform of  $i_j$  are shown in Figures 3.13a and 3.13b respectively which is easier to understand with reference to Figure 3.5.

Current  $i_j$ , with a frequency p times the fundamental, circulates through the appropriate main thyristors and phase windings in the clockwise direction, modifying the currents in all the windings including the primary and as a result, the distortion of the AC input current reduces. This effect will be discussed further in the following section.

Figure 3.13 Current  $i_j$  composition.

a) Construction

b) General waveform

#### 3.4.2 Current Analysis on AC Side

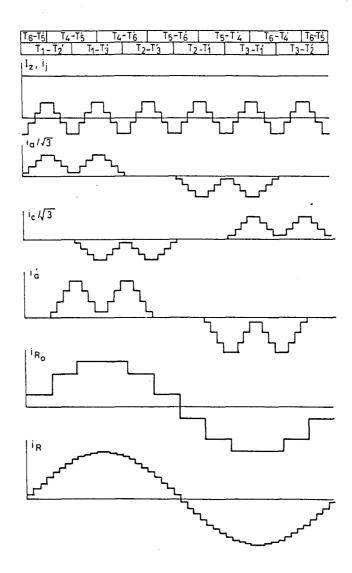

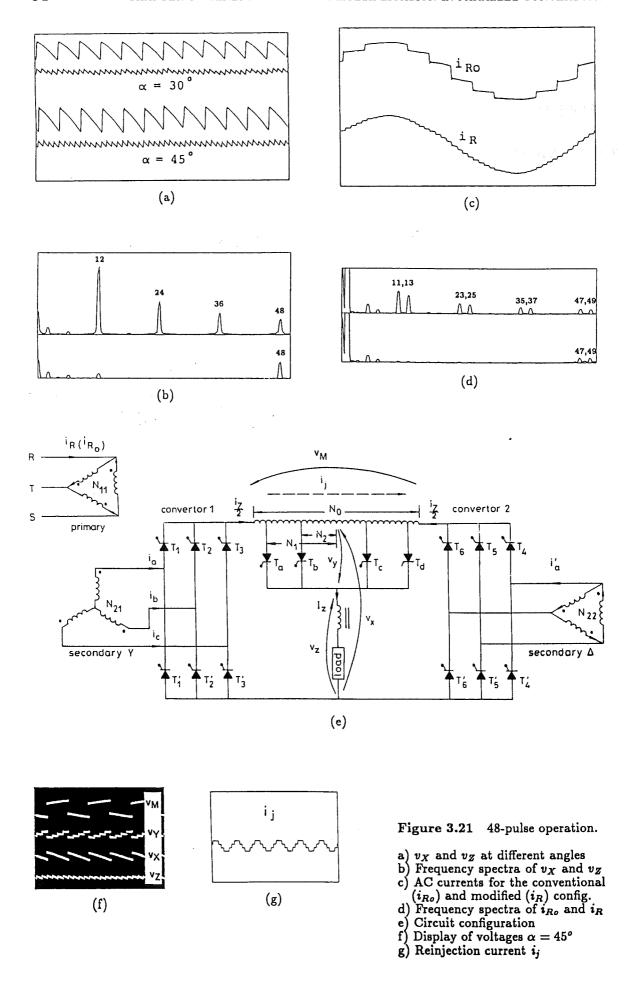

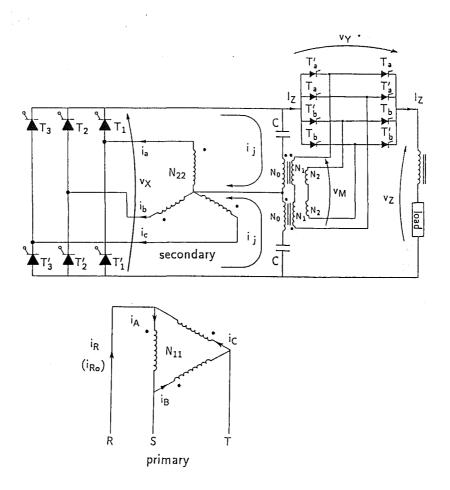

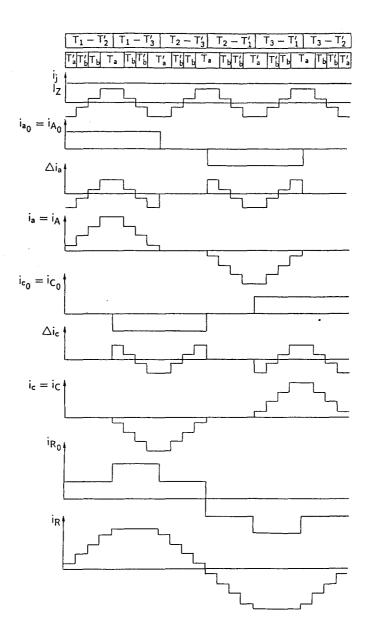

Although the graphical procedure is generally applicable, the results illustrated relate to the specific configuration shown in Figure 3.14.

Figure 3.14 48-pulse configuration.

Figure 3.15 shows all the relevant current waveforms for the circuit of Figure 3.14 under the assumption that

$$N_{11}=N_{22}=\sqrt{3}N_{21}$$

For comparison the AC input current produced by the conventional configuration  $(i_{R_0})$  is also included. Finally with reference to the circuit of Figure 3.14 the following expressions can be written for the AC input current of the modified and conventional configurations respectively

$$i_R=rac{1}{\sqrt{3}}(i_a-i_c)+i_a'$$

$$i_{R_0} = rac{1}{\sqrt{3}}(i_{a_0} - i_{c_0}) + i'_{a_0}$$

Figure 3.15 Theoretical current waveforms of circuit shown in Figure 3.14.

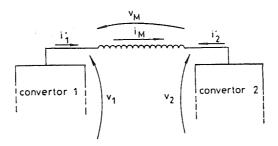

#### 3.5 Design of the Interphase Reactor

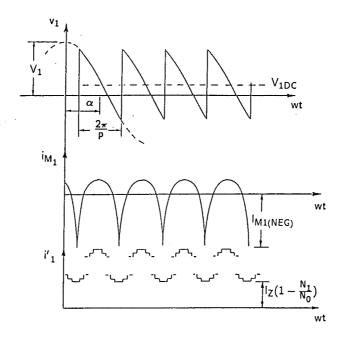

Although in the earlier formulation the reactor magnetising current  $(i_M)$  has been ignored, this current plays an important part in the design of the reactor. For a voltage  $v_M$  to be developed across the reactor (Figure 3.16) there must be a change of magnetic flux caused by the magnetising current. The  $v_M$  and  $i_M$  reactor variables as well as the convertor current  $i'_1$ , are shown in Figure 3.16 and their respective waveforms in Figure 3.17.

Figure 3.16 Magnetisation of reactor.

#### 3.5.1 Minimum Load Current

Let us now analyse the electrical interrelation (voltage and current) between both convertors.

In Figure 3.16  $i'_1$  and  $i'_2$  are the currents produced by the conventional configuration plus the superimposed current due to the effect of connecting the output terminal to alternative taps of the reactor, i.e.:

$$i_1' = I_Z/2 + i_j$$

$$i_2' = I_Z/2 - i_j$$

From Figure 3.13

$$-i_j=i_j(wt-\pi/p)$$

Then

$$i_2' = i_1'(wt - \pi/p)$$

(3.25)

From Figure 3.3

$$v_2 = v_1(wt - \pi/p) \tag{3.26}$$

From equations 3.25 and 3.26 the electrical behaviour of each convertor is the same but every variable displaced by an angle  $\pi/p$ , thus it is enough to analyze one convertor.

In the left convertor  $i'_1$  must be positive enough to compensate for the negative peak of  $i_M$  because of the unidirectional behaviour of convertors, otherwise below a certain value of  $I_Z$ , known as the minimum load current  $I_{Zmin}$ , the magnetising current cannot circulate freely, the reactor no longer continues to provide the voltage  $v_M$ , the circuit reverts to a more complex intermittent conduction and in the limit  $I_Z = 0$ ,  $i_M$  and  $v_M$  become zero.

#### 3.5.2 Magnetising Current Calculation

Let us first assume that  $I_Z$  is sufficient to enable the magnetising current  $i_M$  to circulate freely and that full symmetry exists, so that the reactor is not saturated and therefore its inductance  $L_B$  remains constant.

Figure 3.17 Waveforms of  $v_M$ ,  $i_M$  and  $i'_1$ .

With reference to Figure 3.17, during the positive half-period of  $v_M$  the magnetising current is as follows:

$$L_B \frac{di'_M}{dt} = V_M \sin wt \quad for \quad (\alpha - \pi/2p) < wt < (\alpha + \pi/2p)$$

$$i_M' = (-)\frac{V_M}{wL_B}\cos wt + K_1$$

The corresponding current  $i_M''$  for the negative half-period of  $v_M$  in Figure 3.17 is derived as follows:

$$L_B rac{di_M''}{dt} = -V_M \sin(wt - \pi/p)$$

for  $(\alpha + \pi/2p) < wt < (\alpha + 3\pi/2p)$

$$i_M'' = \frac{V_M}{wL_B}\cos(wt - \pi/p) + K_2$$

In order for  $v_M$  to be finite,  $di_M/dt$  must also be finite, and therefore  $i_M$  must be continuous, hence:

$$i_M'(\alpha+\pi/2p)=i_M''(\alpha+\pi/2p)$$

$$-\frac{V_M}{wL_B}\cos(\alpha+\pi/2p)+K_1=\frac{V_M}{wL_B}\cos(\alpha-\pi/2p)+K_2$$

$$-\frac{V_M}{wL_B}\cos\alpha\cos\pi/2p + K_1 = \frac{V_M}{wL_B}\cos\alpha\cos\pi/2p + K_2 \tag{3.27}$$

The mean value of  $i_M$  must be zero, then

$$\int_{lpha-\pi/2p}^{lpha+\pi/2p}i_M'\,d(wt)+\int_{lpha+\pi/2p}^{lpha+3\pi/2p}i_M''\,d(wt)=0$$

$-rac{V_M}{wL_B}\Big[\sin(lpha+\pi/2p)-\sin(lpha-\pi/2p)\Big]+rac{K_1\pi}{p}+$   $rac{V_M}{wL_B}\Big[\sin(lpha+\pi/2p)-\sin(lpha-\pi/2p)\Big]+rac{K_2\pi}{p}=0$

Therefore

$$K_1 + K_2 = 0 (3.28)$$

The solution of equations 3.27 and 3.28 is

$$K_1 = -K_2 = \frac{V_M}{wL_B}\cos\alpha\cos\pi/2p$$

Finally

$$i_M' = -\frac{V_M}{wL_B}(\cos wt - \cos \alpha \cos \pi/2p) \quad for \quad (\alpha - \pi/2p) < wt < (\alpha + \pi/2p) \quad (3.29)$$

$$i_M'' = \frac{V_M}{wL_B} \left[ \cos(wt - \pi/p) - \cos\alpha\cos\pi/2p \right] \quad for \quad (\alpha + \pi/2p) < wt < (\alpha + 3\pi/2p)$$

Figure 3.17 illustrates waveforms  $v_M$ ,  $i_M$  and  $i'_1$  which will be better understood with reference to Figure 3.13.

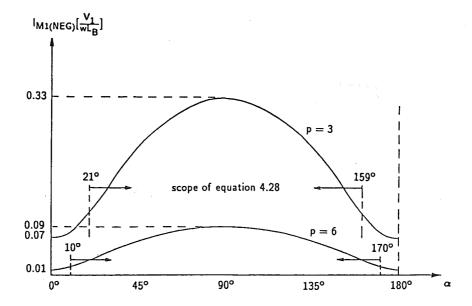

The peak value of the magnetising current is given by:

$$I_M = i_M'(wt = \alpha + \pi/2p) = \frac{V_M}{wL_B}\sin \pi/2p\sin \alpha$$

and taking into consideration equation 3.11

$$V_M = 2V_1 \sin \pi/2p$$

Therefore

$$I_M = \frac{2V_1 \sin^2 \pi / 2p}{w L_B} \sin \alpha \tag{3.30}$$

However equation 3.30 does not provide appropriate values for  $\alpha = 0^{\circ}$  and  $\alpha = 180^{\circ}$ . A graphical analysis of equation 3.29 reveals that

$$I_M = \left|i_M'(wt = 0^o)\right| = \frac{2V_1 \sin \pi/2p}{wL_B} (1 - \cos \alpha \cos \pi/2p) \quad for \quad \alpha \le \pi/2p$$

$$I_M=i_M'(wt=lpha+\pi/2p)=rac{2V_1\sin^2\pi/2p}{wL_B}\sinlpha \quad for \quad \pi/2p\lelpha\le(\pi-\pi/2p)$$

$$I_{M} = i'_{M}(wt = 180^{\circ}) = \frac{2V_{1}\sin\pi/2p}{wL_{B}}(1 + \cos\alpha\cos\pi/2p)$$

for  $\alpha \ge (\pi - \pi/2p)$

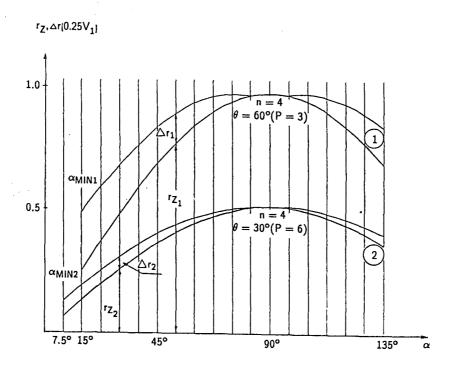

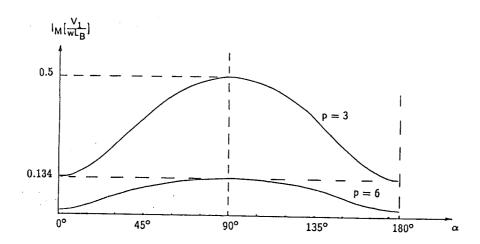

The variation of  $I_M$  with  $\alpha$  is plotted in Figure 3.18 for p=3 and p=6.

Figure 3.18 Variation of  $I_M$  with  $\alpha$ .

#### 3.5.3 Relationship Between $I_{Zmin}$ and $L_B$

In Figure 3.16 the limiting operating condition is

$$min(i'_1) = max negative peak of i_M$$

From Figures 3.17 and 3.18

$$\frac{I_{Zmin}}{2} - \frac{N_n}{N_0} I_{Zmin} = I_M(for \ \alpha = 90^\circ)$$

and from equation 3.30

$$I_{Zmin}\left(\frac{1}{2} - \frac{N_n}{N_0}\right) = \frac{2V_1\sin^2\pi/2p}{wL_B}$$

and considering equation 3.12 finally

$$L_B = \frac{2V_1 \sin^2 \pi / 2p}{w I_{Zmin} (1/2 - N_n / N_0)} \quad [H]$$

where:

$$\frac{N_n}{N_0} = \frac{\tan\frac{\pi(n-1)}{2np}}{2\tan\frac{\pi}{2p}}$$

#### 3.6 Component Ratings

The rating of the main thyristors and convertor transformers will be obtained for the particular configuration of Figure 3.14, however for the rating of the reactor thyristors and interphase reactor, general expressions will be considered.

#### 3.6.1 Main Thyristors

The maximum voltage across the main thyristors remains unchanged for the conventional and modified configurations.

The current rating of the main thyristors for the conventional configuration is as follows:

$$I_{MAX} = I_Z/2 = 0.5I_Z$$

$$I_{MEAN} = I_Z/6 = 0.167I_Z$$

$$I_{RMS} = I_Z/(2\sqrt{3}) = 0.289I_Z$$

Where  $I_Z$ , the load current, is assumed to be constant.

Considering now the particular configuration of Figure 3.14 and with reference to Figures 3.12, 3.13 and 3.15

$$I_{MAX} = I_Z \left(\frac{1}{2} + \frac{N_1}{N_0}\right) = I_Z \left(\frac{1}{2} + 0.371\right)$$

$$I_{MAX} = 0.871I_Z$$

**Besides**

$$I_Z \left( \frac{1}{2} + \frac{N_2}{N_0} \right) = 0.622$$

$$I_Z \left( \frac{1}{2} - \frac{N_2}{N_0} \right) = 0.378$$

$$I_Z\Big(\frac{1}{2} - \frac{N_1}{N_0}\Big) = 0.129$$

Then

$$I_{MEAN} = rac{1}{2\pi} igl[ 4\pi/24(0.129 + 0.378 + 0.622 + 0.871) I_Z igr]$$

$$I_{MEAN} = 0.167I_Z$$

and

$$I_{RMS}^2 = \frac{1}{2\pi} \left[ 4\pi/24(0.129^2 + 0.378^2 + 0.622^2 + 0.871^2)I_Z^2 \right]$$

$$I_{RMS} = 0.33I_Z$$

#### 3.6.2 Convertor transformers

The RMS current in the star secondary for the conventional configuration is (considering Figure 3.15)

$$I_{a0_{RMS}}^2 = rac{1}{\pi} \int_0^{2\pi/3} \left(rac{1}{2}I_Z

ight)^2 d heta$$

$$I_{a0_{RMS}} = 0.408I_Z$$

and for the proposed configuration

$$I_{a_{RMS}}^2 = \frac{1}{\pi} \left[ 4\pi/24(0.129^2 + 0.378^2 + 0.622^2 + 0.871^2)I_Z^2 \right]$$

$$I_{a_{RMS}} = 0.466I_Z$$

Similarly the RMS current in the delta secondary for the conventional configuration is

$$I_{a0_{RMS}}^{"2} = \frac{1}{\pi} \Big[ 2\pi/3(1/6I_Z)^2 + \pi/3(1/3I_Z)^2 \Big]$$

$$I_{a0_{RMS}}^{\prime\prime}=0.236I_Z$$

and for the proposed configuration

$$I_{a_{RMS}}^{"2} = \frac{I_Z^2}{\pi/2} \left[ \pi/12(0.043^2 + 0.126^2 + 0.207^2 + 0.29^2) + \right]$$

$$+\pi/24(0.086^2+0.252^2+0.415^2+0.58^2)$$

$$I_{a_{RMS}}^{\prime\prime}=0.269I_Z$$

Corresponding currents on the delta primary are

$$I_{A0_{RMS}}^2 = \frac{I_Z^2}{\pi/2} \pi/6 \left[ (1/6)^2 + (0.455)^2 + (0.622)^2 \right]$$

$$I_{A0_{PMS}} = 0.455I_Z$$

for the conventional and

$$I_{A_{RMS}}^2 = \frac{I_Z^2}{\pi/2} \Big[ \pi/24(0.043^2 + 0.126^2 + 0.207^2 + 0.290^2 + 0.365^2 + 0.425^2 + 0.485^2 + 0.545^2 + 0.589^2 + 0.611^2 + 0.633^2 + 0.655^2) \Big]$$

$$I_{A_{RMS}} = 0.46I_Z$$

for the proposed configuration.

## 3.6.3 Reactor Thyristors

Figure 3.19 Voltage across feedback thyristors.

With reference to Figure 3.19 let us analyse the maximum voltage across any left half thyristor when  $T_n$  conducts (since this is the worst condition).

Then

$$v_{T_k} = \frac{N_n + N_k}{N_0} v_M$$

The maximum voltage across  $T_k(V_{T_k})$  is

$$V_{T_k} = \frac{N_n + N_k}{N_0} V_M$$

considering equation 3.11

$$V_{T_k} = \frac{N_n + N_k}{N_0} 2V_1 \sin \pi / 2p \tag{3.31}$$

and the same voltage distribution, symmetrically, is established on the right half when  $T_1$  conducts.

With reference to Figure 3.14 for n = 4 and p = 6

$$V_{T_a} = V_{T_d} = (0.371)4V_1 \sin \pi/12$$

$$= 0.384V_1$$

and

$$V_{T_b} = V_{T_c} = (0.371 + 0.122)2V_1 \sin \pi / 12$$

$$= 0.255V_1$$

Where  $V_1$  is the peak phase to phase voltage on the convertor side of the transformers. Also, with reference to Figures 3.13 and 3.5, during each cycle  $2\theta$ , each thyristor carries current  $I_Z$  during a total conduction period of  $2\theta/n$ , then the following expressions are obtained for the current of the feedback thyristors

$$I_{MAX} = I_Z$$

$$I_{MEAN} = \frac{1}{2\theta} \frac{2\theta}{n} I_Z = I_Z/n$$

$$I_{RMS} = \sqrt{\frac{1}{2\theta} \frac{2\theta}{n} I_Z^2} = \frac{I_Z}{\sqrt{n}}$$

with reference to Figure 3.14 for n = 4

$$I_{MEAN} = I_Z/4 = 0.25I_Z$$

$$I_{RMS} = \frac{I_Z}{\sqrt{4}} = 0.5I_Z$$

# 3.6.4 Interphase Reactor

The maximum voltage across the interphase reactor (when  $\alpha = 90^{\circ}$ ) remains unchanged and is given (considering Figure 3.8) by

$$V_{RMS} = \sqrt{\frac{p}{\pi} \int_{-\pi/2p}^{\pi/2p} V_M^2 \cos^2 wt \, d(wt)} = V_M \sqrt{\frac{1}{2} + \frac{p}{2\pi} \sin \pi/p}$$

considering equation 3.11

$$V_{RMS}=2V_1\sin\pi/2p\sqrt{rac{1}{2}+rac{p}{2\pi}\sin\pi/p}$$

With reference to Figure 3.14 for p = 6

$$V_{RMS} = 0.512V_1$$

Let us now consider the different currents through the reactor illustrated in Figure 3.20.

Figure 3.20 Currents through the reactor.

From Figures 3.12 and 3.13

$$i_0 = I_Z/2 + i_j (3.32)$$

Then its RMS value

$$I_0^2 = \frac{1}{\theta} \frac{\theta}{n} I_Z^2 \left[ \left( \frac{1}{2} + \frac{N_1}{N_0} \right)^2 + \left( \frac{1}{2} + \frac{N_2}{N_0} \right)^2 + \right]$$

..... +

$$(\frac{1}{2} - \frac{N_{n-1}}{N_0})^2 + (\frac{1}{2} - \frac{N_n}{N_0})^2$$

For any other current the contribution  $I_Z/2$  in equation 3.31 is no longer constant but variable in sign depending on which thyristor is conducting. Therefore the RMS current of branch k is

$$I_k^2 = \frac{I_Z^2}{n} \left[ \left( -\frac{1}{2} + \frac{N_1}{N_0} \right)^2 + \dots + \left( -\frac{1}{2} + \frac{N_k}{N_0} \right)^2 + \dots \right]$$

$$+(\frac{1}{2}+\frac{N_{k+1}}{N_0})^2+\dots+(\frac{1}{2}-\frac{N_n}{N_0})^2$$

With reference to Figure 3.14 the currents through the reactor are

$$I_0 = I_d = 0.571I_Z$$

$$I_a = I_c = 0.375I_Z$$

$$I_b = 0.282I_Z$$

Table 3.2 summarises the ratings of the main elements of the conventional (without thyristor taps) and modified (with thyristor taps) configurations with reference to the output current  $(I_Z)$  and the transformer secondary voltage peak  $(V_1)$ .

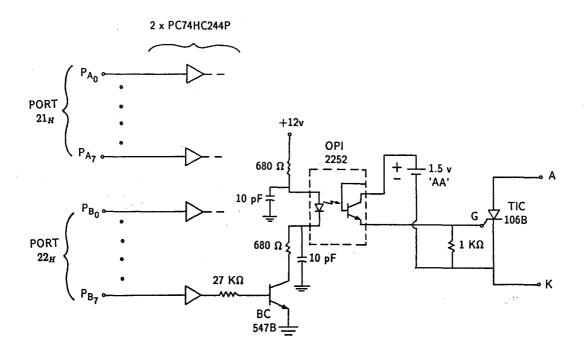

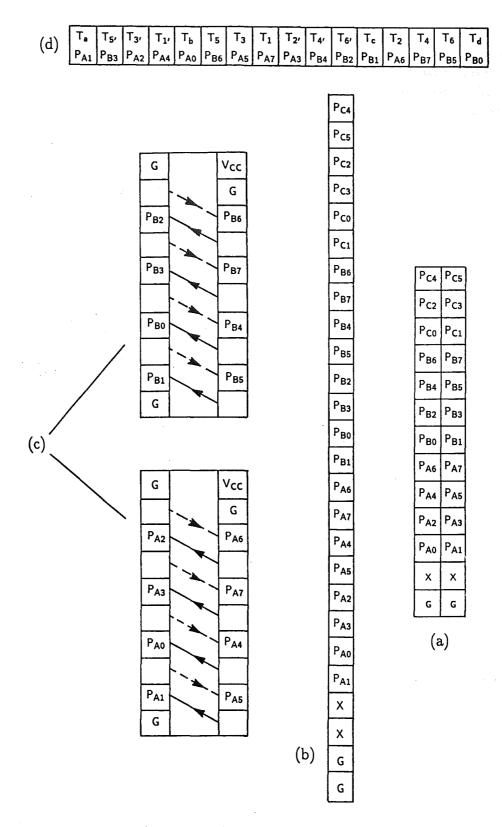

# 3.7 Experimental Verification

A laboratory model, considered in Chapter 5, has been specially designed to verify the theoretical waveforms and a complete set of experimental results is given in this section.

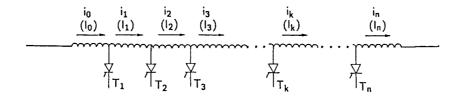

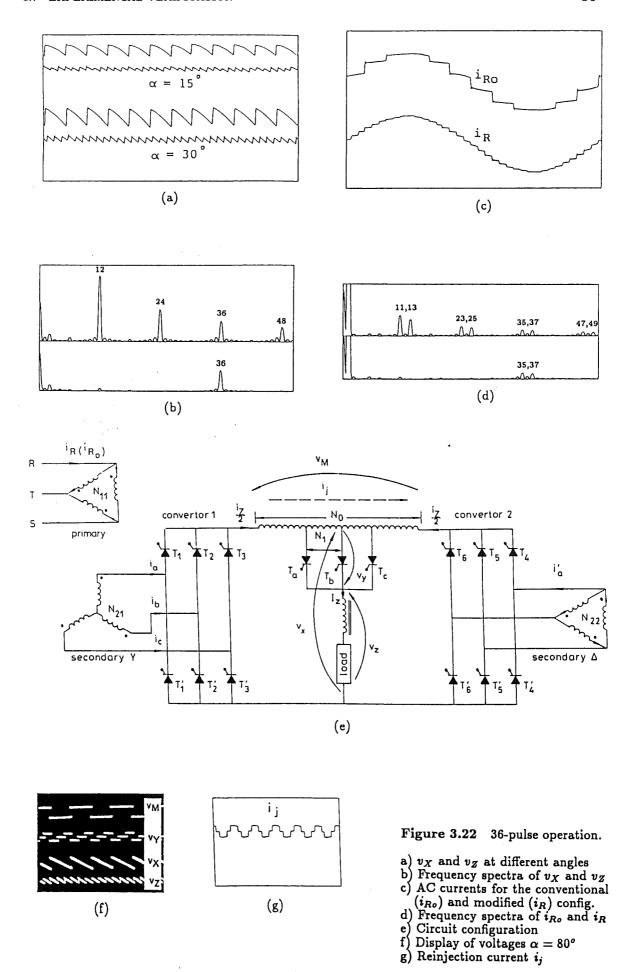

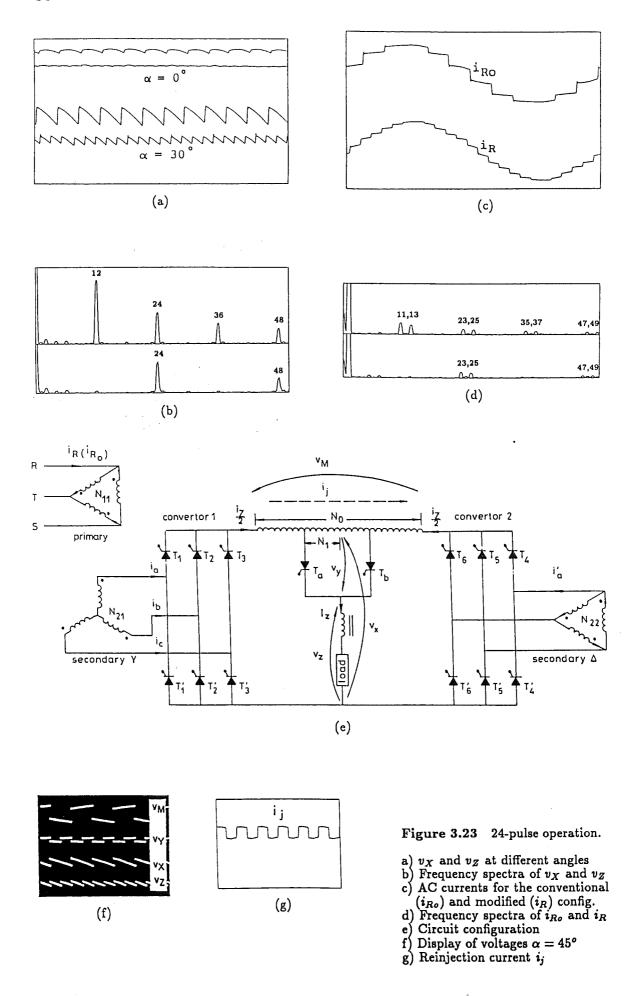

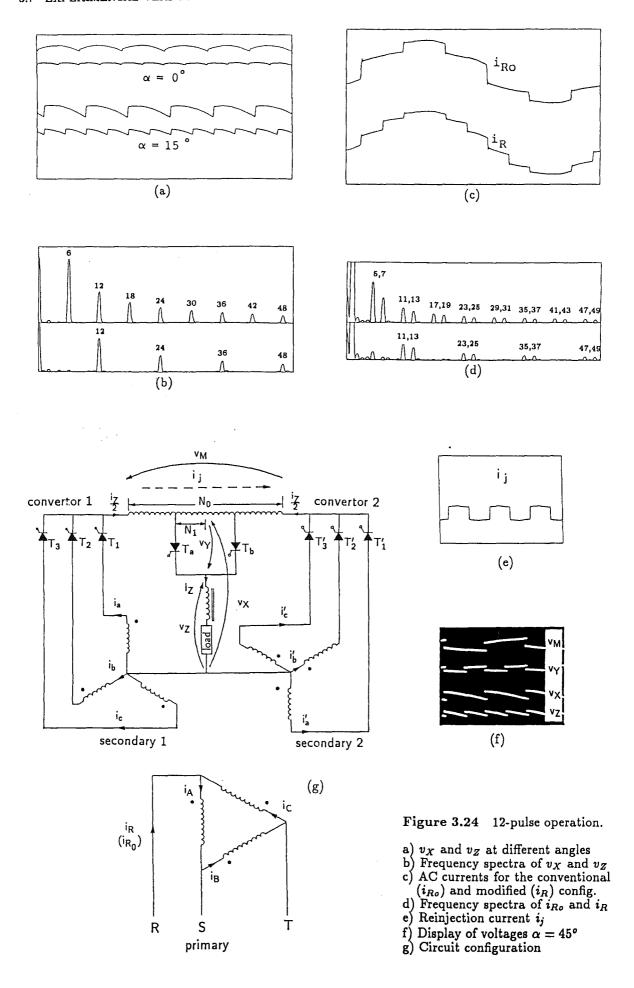

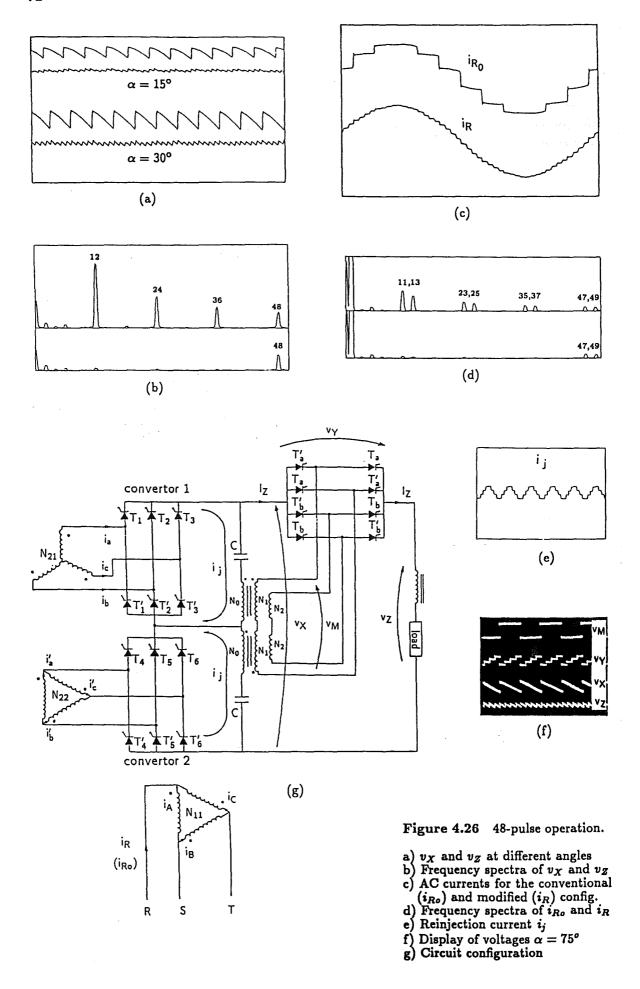

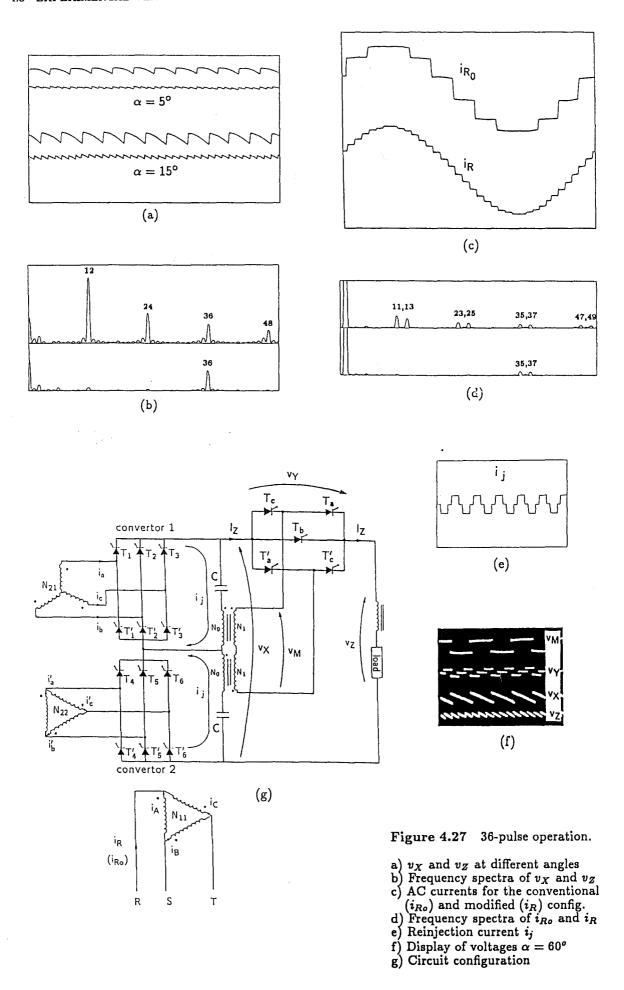

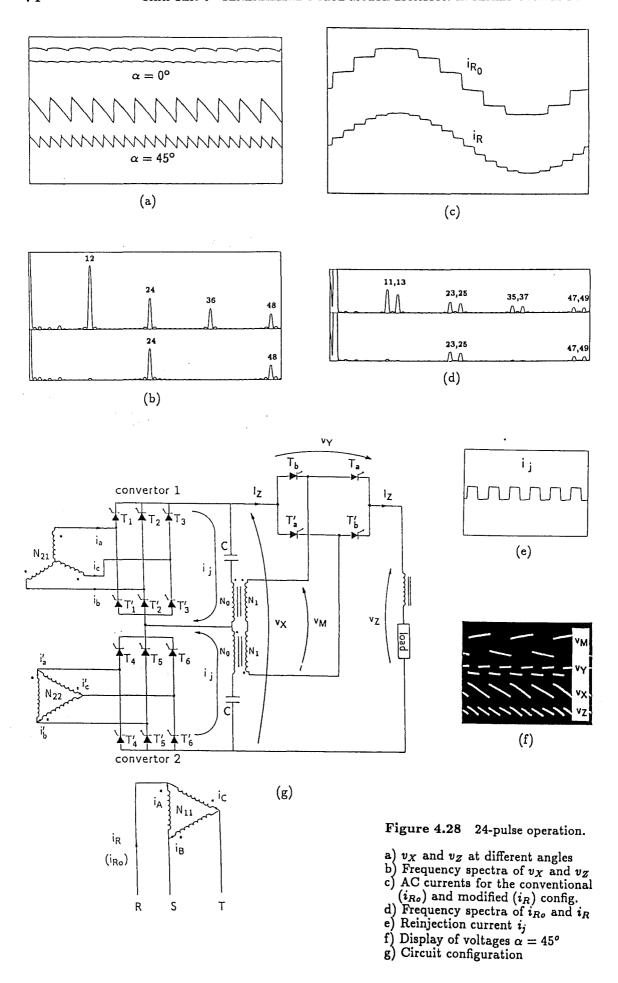

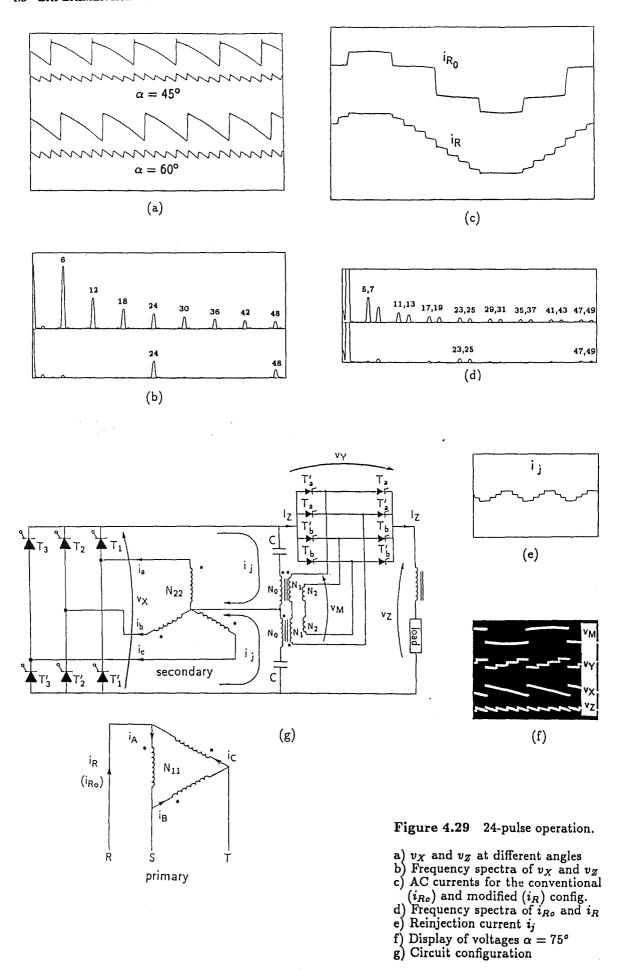

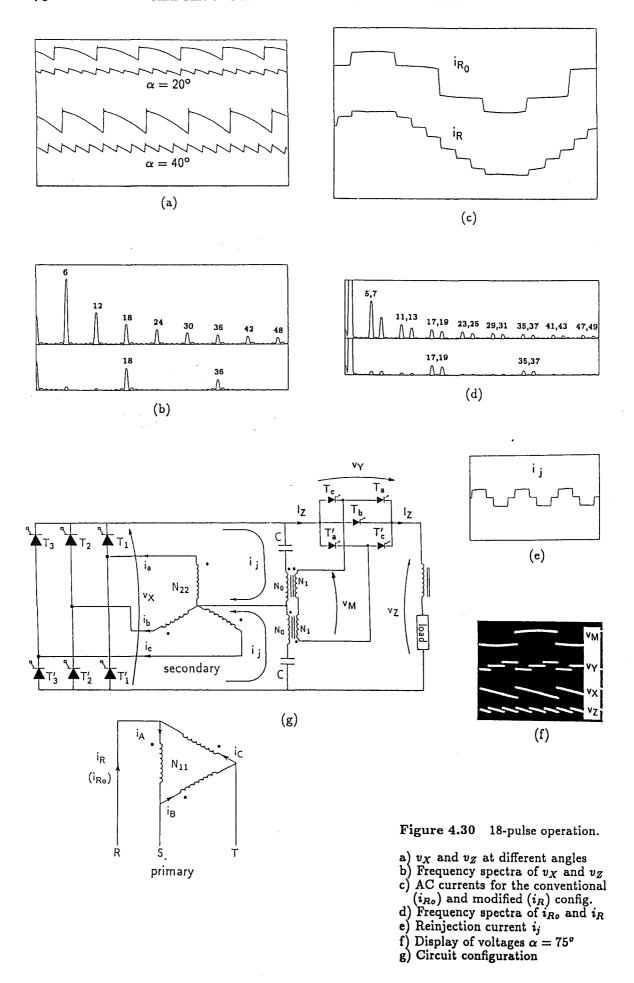

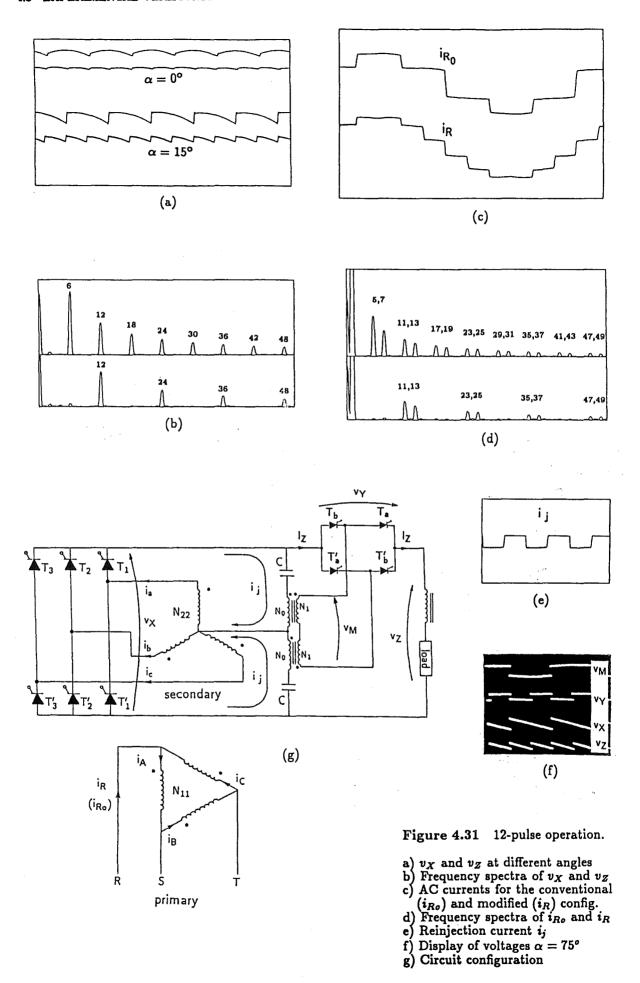

Figures 3.21-3.24 give the experimental verification. Convertors 1 and 2 are conventional configurations giving a pulse number (p) of 6 for Figures 3.21-3.23 and a pulse number of 3 for Figure 3.24.

From equation 3.6 the pulse number of the output voltage  $v_z$  is  $p_Z = 2pn$ , where n is the number of feedback thyristors. Therefore the pulse number  $p_z$  is 48,36,24 and 12 for Figures 3.21-3.24 respectively.

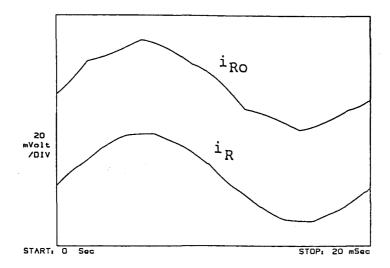

For these Figures, diagrams labelled 'a' show the output voltage waveforms for the conventional  $(v_x)$  and modified  $(v_z)$  configurations and diagrams labelled 'b' their respective frequency spectra. Similarly, diagrams labelled 'c' display the current waveform on the AC side for the conventional  $(i_{Ro})$  and modified  $(i_R)$  configurations and diagrams labelled 'd' their respective frequency spectra. The reinjection current  $i_j$  is shown in diagrams 'g' in Figures 3.21-3.23 and in diagram 'e' in Figure 3.24. These diagrams were taken using a Hewlett Packard dynamic signal analizer 3561A.

The rest of the diagrams include the respective circuit configuration and a display of various DC voltages waveforms using a normal scope.

A comparison between the theoretical waveforms  $i_j$ ,  $i_{Ro}$  and  $i_R$  of Figure 3.15 and the respective practical waveforms of Figure 3.21 fully demonstrates the theoretical treatment developed in previous sections.

## 3.8 Conclusions

By means of a generalized and rigorous theoretical treatment, along with extensive experimental verification, this chapter has shown the capability of the DC ripple reinjection technique to obtain any desired pulse and step multiplication on the AC and DC sides of parallel-connected convertors. The mathematical analysis is straight-forward and without any complication generates formulas and diagrams that permit the design and understanding of these modified schemes.

| <u>.</u>                     |                  | WITHOUT T.T.               | WITH T.T.                  | Δ %                                    |  |

|------------------------------|------------------|----------------------------|----------------------------|----------------------------------------|--|

| MAIN<br>THYRISTORS           | VMAX             | γ,                         | V <sub>1</sub>             | 0 .                                    |  |

|                              | I <sub>MAX</sub> | 0.5 I <sub>Z</sub>         | 0.871 Iz                   | 74.2                                   |  |

|                              | IMEAN            | 0.167 I <sub>Z</sub>       | 0.167 I <sub>Z</sub>       | 0                                      |  |

|                              | IRMS             | 0.289 I <sub>Z</sub>       | 0.33 I <sub>Z</sub>        | 14.19                                  |  |

| V <sub>DC</sub> OUTPUT       |                  | 0.955 V <sub>1</sub> cos α | 0.984 V <sub>1</sub> cos α | 3.04                                   |  |

| IRMS STAR SEC.               |                  | 0.408 I <sub>Z</sub>       | 0.466 Iz                   | 14.22                                  |  |

| IRMS DELTA SEC.              |                  | 0.236 I <sub>Z</sub>       | 0.269 Iz                   | 14.0                                   |  |

| I <sub>RMS</sub> DELTA PRIM. |                  | 0.455 I <sub>Z</sub>       | 0.46 I <sub>Z</sub>        | 1.1                                    |  |

| P <sub>DC</sub> OUTPUT       |                  | Iz V <sub>DC</sub> OUTPUT  | Iz VDC OUTPUT              | 3.04                                   |  |

| FEEDBACK<br>THYRISTORS       | VMAX             | _                          | 0.384 V <sub>1</sub>       | $-(T_a,T_d)$                           |  |

|                              |                  | -                          | 0.255 V <sub>1</sub>       | - (T <sub>b</sub> ,T <sub>c</sub> )    |  |

|                              | I <sub>MAX</sub> | _                          | Iz                         | _                                      |  |

|                              | IMEAN            | -                          | 0.25 Iz                    | _                                      |  |

|                              | IRMS             | -                          | 0.5 I <sub>Z</sub>         | _                                      |  |

|                              | V <sub>RMS</sub> | 0.512 V <sub>1</sub>       | 0.512 V <sub>1</sub>       | 0                                      |  |

| INTERPHASE                   |                  |                            | 0.571 Iz                   | 14.2 (I <sub>o</sub> ,I <sub>d</sub> ) |  |

| REACTOR                      |                  | 0.5 I <sub>Z</sub>         | 0.375 Iz                   | $-25.0 (I_a, I_c)$                     |  |

|                              |                  |                            | 0.282 Iz                   | -43.6 (I <sub>b</sub> )                |  |

Table 3.2 Component ratings for the conventional and modified (48-pulse) configurations

# Generalized Pulse Multiplication in Series Convertors

# 4.1 Introduction

A generalised DC ripple reinjection scheme applicable to series connection of convertors is presented in this chapter. It is capable of achieving, by natural commutation, any desired number of pulses and thus provides a complete alternative to the use of AC and DC filters in HVdc systems. A rigorous analysis of the general configuration shown in Figure 4.1 is included. General formulas and time diagrams are obtained that permit a straight-forward design of high-pulse series-connected convertors, along with a clear understanding of the principles involved. Experimental results at the end of this chapter validate the concept completely.

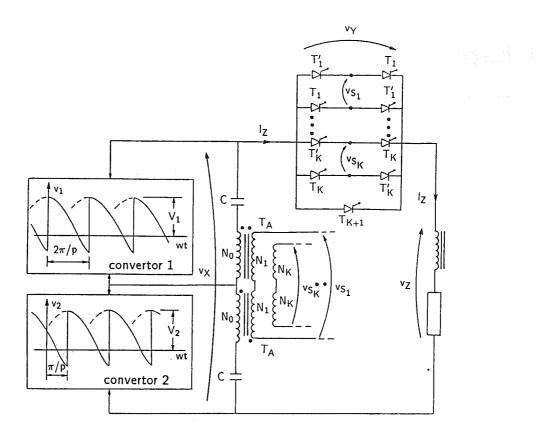

# 4.2 General Conditions and Circuit Configuration

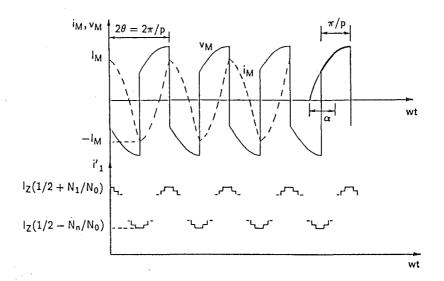

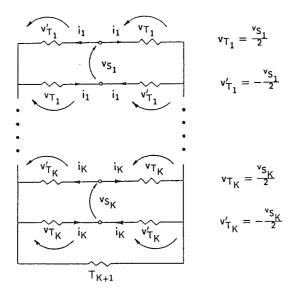

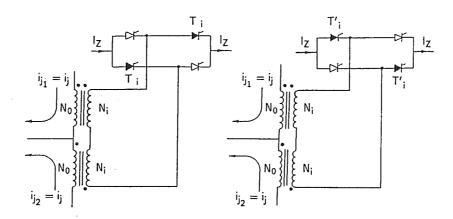

Figure 4.1 shows a modified double convertor configuration with additional components to permit DC ripple reinjection and thus high-pulse operation. The reinjection circuit includes two capacitors C, two transformers  $T_A$  with several secondary windings, K single-phase bridges and a by-pass thyristor  $T_{K+1}$ . Each single-phase bridge is connected to the secondaries of the reinjection transformers as indicated in the general configuration of Figure 4.1.

The average output voltages of the two convertors are the same but their waveforms are displaced by an angle  $\pi/p$ , where p is the pulse number of each convertor. As will be shown, appropriate firing of the additional feedback single-phase bridges and by-pass thyristor, permit the establishment of a variable  $v_Y$ , which if added to the conventional variable  $v_X$ , increases the pulse number of the output variable  $v_Z$ .

Similarly the ripple reinjection bridges inject square-wave currents on the primary side of the transformers  $T_A$ , which modifies all the original current waveforms and as a result, the distortion of the AC side current waveform reduces.

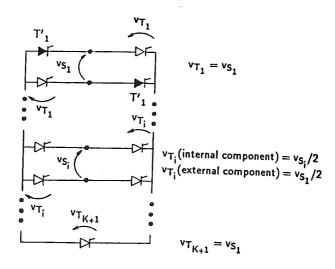

Figure 4.1 Multi-pulse convertor configuration.

Figure 4.2 Derivation of voltage  $v_Y$ .

# 4.3 Voltage Considerations

# 4.3.1 Derivation of the Output Voltage Waveform

In Figure 4.1 the capacitors are required to block the DC component of voltages  $v_1$  and  $v_2$ . As a first approximation let us assume that they are large enough to present a short circuit to the AC components of  $v_1$  and  $v_2$  ( $v_{1AC}$  and  $v_{2AC}$ ) and thus, only this components are present across the primary side of transformers  $T_A$ .

Figure 4.2 considers a generic bridge i and explains the derivation of  $v_Y$  as follows: During  $T_i$  conduction (Figure 4.2a)

$$v_{Si} = \frac{N_i}{N_0}(v_{1AC} - v_{2AC})$$

and

$$v_{Yi} = v_{Si} = \frac{N_i}{N_0} v_M \tag{4.1}$$

where

$$v_M = v_{1AC} - v_{2AC} = v_1 - v_2 (4.2)$$

Similarly, during  $T_i'$  conduction (Figure 4.2b)

$$v_{Yi'} = -v_{Si} = -\frac{N_i}{N_0} v_M \tag{4.3}$$

Finally when thyristor  $T_{K+1}$  conducts  $v_{Y_{K+1}} = 0$

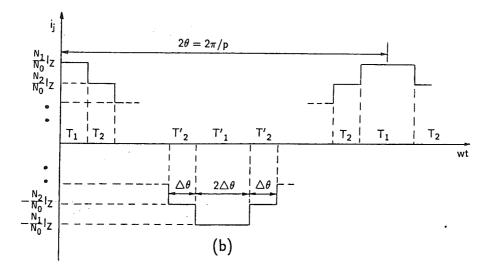

Figure 4.3 shows the successive circuit conditions created by the conducting state of the two convertors. These are repeated every  $2\pi$  radians and the number of different circuit conditions per cycle is  $2\pi/\theta = 2p$ .

Figure 4.3 Successive circuit conditions of convertors 1 and 2.

Figures 4.4a and 4.4b show the phasor diagrams corresponding to circuit conditions I and II respectively. The position of  $\dot{V}_2$  is kept fixed while  $\dot{V}_1$  leads or lags  $\dot{V}_2$  by an angle  $\theta$ . The rest of the circuit conditions can be represented in a similar way. The phasor diagrams of Figure 4.4 also include phasors  $\dot{V}_M$ ,  $\dot{V}_X$ ,  $\dot{V}_Y$ ,  $\dot{V}_Z$ . With reference to equation 4.2 and Figure 4.1 the following relationships can be written:

$$\dot{V}_{M} = \dot{V}_1 - \dot{V}_2 \tag{4.4}$$

$$\dot{V}_X = \dot{V}_1 + \dot{V}_2 \tag{4.5}$$

$$\dot{V}_Z = \dot{V}_X + \dot{V}_Y \tag{4.6}$$

with  $\dot{V}_Y$  defined in equations 4.1 and 4.3.

Figure 4.4 Diagrams with reference to Figure 4.3.

a) Circuit condition I

b) Circuit condition II

The selection of a suitable firing angle for the feedback thyristors, combined with appropriate feedback transformer ratios permits the derivation of a sequence of sine-wave portions for the output voltage  $v_Z$ . These sine-wave portions can be adjusted by normal firing angle control to obtain the required mean value of  $v_Z$ .

For simplicity Figure 4.4 has only displayed the effect of a single reinjection bridge, i.e. the conduction patterns of thyristors  $T_1$  and  $T_1'$ . With reference to Figure 4.4 the duration of each sine-wave portion  $(\triangle \theta)$  and the resulting pulse number of  $v_Z$   $(p_Z)$  for each cycle of the supply system voltage will be as follows:

$$\triangle \theta = \frac{\theta}{2K} = \frac{\pi}{2pK} \tag{4.7}$$

$$p_Z = \frac{2\pi}{\triangle \theta} = 4pK$$

if thyristor  $T_{K+1}$  is omitted and

$$\Delta\theta = \frac{\theta}{2K+1} = \frac{\pi}{p(2K+1)} \tag{4.8}$$

$$p_Z=rac{2\pi}{\triangle heta}=2p(2K+1)$$

if thyristor  $T_{K+1}$  is considered.

The coordination of the feedback thyristors and the main thyristors is illustrated in Figure 4.5 where the following rule can be stated.

Every change of conducting state in convertor 2 must be followed by a sequential turnon of the feedback thyristors from  $T_2$  to  $T_1'$ . With reference to changes in convertor 1 the triggering order sequence should be from  $T_2'$  to  $T_1$  instead. The interval between successive turn-on's is shown to be  $\Delta\theta$ .

Figure 4.5 General triggering coordination.

## 4.3.2 Feedback Transformers Turns Ratio

From equation 4.1 and using peak values for  $V_M$ ,  $V_{Yi}$ ,  $V_X$  and  $V_1$

$$\frac{N_i}{N_0} = \frac{V_{Yi}}{V_M} \tag{4.9}$$

also from Figure 4.4a

$$V_{Yi} = V_X \tan \theta_i \tag{4.10}$$

$$V_X = 2V_1 \cos(\theta/2) \tag{4.11}$$

$$V_M = 2V_1 \sin(\theta/2) \tag{4.12}$$

Combining equations 4.9 to 4.12

$$\frac{N_i}{N_0} = \frac{\tan \theta_i}{\tan(\theta/2)} \quad \text{for} \quad i = 1, \dots, K$$

(4.13)

where:

$$heta_i = rac{ heta}{4K}(2K+1-2i) \quad (if \ thyristor \ T_{K+1} \ is \ omitted)$$

$$\theta_i = \frac{\theta}{2K+1}(K+1-i)$$

(if thyristor  $T_{K+1}$  is considered)

K: Total feedback single-phase convertor bridges

p: Pulse number of main convertors 1 and 2

$\theta : \pi/p$

$N_i/N_0$ : Turns ratio of feedback transformers

## 4.3.3 Turn Ratio Alterations of Feedback Transformers

The exact turns ratios derived from equation 4.13 cannot be implemented in practice and the effect of the deviation from that value will now be examined.

Figure 4.6 Angular effect of turn ratio alterations.

With reference to Figure 4.4a, Figure 4.6 illustrates the angular displacement of phasor  $\dot{V}_{Zi}$  ( $\triangle \theta_i$ ) when its associated turn ratio ( $r_i = N_i/N_0$ ) is altered.

The respective angular displacement  $(\triangle \theta_i)$  is derived as follows:

$$an heta_i' = rac{r_i' V_M}{V_X}$$

$$an heta_i = rac{r_i V_M}{V_X}$$

$$\frac{\tan \theta_i'}{\tan \theta_i} = \frac{r_i'}{r_i}$$

then

$$\Delta \theta_i = \theta_i' - \theta_i = \tan^{-1} \left( \frac{r_i'}{r_i} \tan \theta_i \right) - \theta_i \tag{4.14}$$

With  $\theta_i$  and  $r_i$  defined in equation 4.13.

From Figure 4.4b,  $\triangle \theta_i$  must be compared with  $\triangle \theta$  to appreciate the effect of modifying  $r_i$ .

This effect is illustrated in Table 4.1 with reference to a simple example (24-pulse configuration). The asymmetry is of little significance and in most cases only the second digit in equation 4.13 is important.

| P | K | T <sub>K+1</sub> | $r_1 = \frac{N_1}{N_0}$ | $r_1' = \frac{N_1'}{N_0}$ | Δθ,    | Δθ  | Δ θ 1% |

|---|---|------------------|-------------------------|---------------------------|--------|-----|--------|

| 6 | 1 | NO               | 0.4913                  | 0.5                       | 0.131° | 15° | 0.88   |

Table 4.1 Example of turn ratio deviation.

### 4.3.4 Conditions for Natural Commutation

Consideration is first given to the feedback thyristors which conduct initially and their respective instant of conduction.

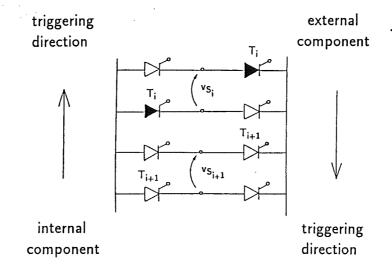

Assuming that initially all the feedback thyristors are in the blocking state and that the current distribution in each single phase bridge is symmetrical, the equivalent circuit of Figure 4.7 applies.

In Figure 4.7 there are K electrically active and independent loops, each of them fed by a voltage  $v_{Si}$  which, considering equation 4.1, is proportional to  $v_M$ .

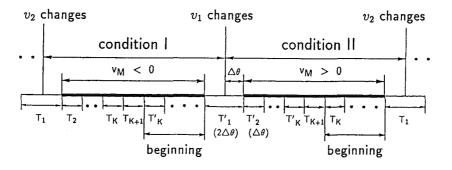

With reference to Figure 4.5 and taking into account the appropriate sign of  $v_M$  the instant of conduction and the thyristors involved are those labelled 'beginning'.

The generic transfer between thyristors for condition I in Figure 4.5 is shown in Figure 4.8.

The bridge i+1 is fed by  $v_{Si}$  (an external component) and  $v_{Si+1}$  (an internal component). Since  $v_{Si} > v_{Si+1}$  only  $v_{Si}$  decides whether the transfer from  $T_i$  to  $T_{i+1}$  can take place by natural commutation and Figure 4.9 illustrates this condition.

Figure 4.7 Initial condition of feedback thyristors circuit.

Figure 4.8 Generic transfer between feedback thyristors.

Figure 4.9 Effect of external component on bridge i + 1.

In Figure 4.9,  $v_{Si}$  (and therefore  $v_M$ ) must be negative for thyristor  $T_{i+1}$  to turn on by natural commutation. In the transfer from  $T_{K+1}$  to  $T_K'$  the external component is zero.

Figure 4.8 shows the component which is relevant depending on the triggering direction and this rule applies equally to conditions I and II of Figure 4.5.

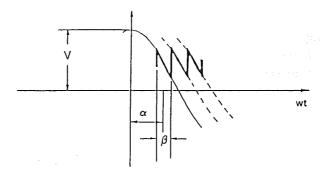

By comparing Figures 4.5 and 4.3, it can be deduced that the conditions for  $v_M$  in Figure 4.5 are satisfied, although there are some restrictions for  $\alpha$  close to zero. This can be explained with reference to Figure 4.10 wich illustrates the behaviour of  $v_M$  and  $v_X$  for the specific condition II illustrated in Figure 4.4b. As indicated in this Figure ,  $v_M$  lags  $v_X$  by  $\pi/2$  radians. Also in Figure 4.10 x defines the location, along the respective sinusoids, of  $v_M$  and  $v_X$ ; furthermore  $x = \alpha$  because waveform  $v_X$  is at a maximum when  $x = 0^\circ$ .

It can be deduced from Figures 4.5 and 4.10 that the minimum angle  $(\alpha_{MIN})$  that satisfies the restriction for  $v_M$  in condition II is

$$\alpha_{MIN} = \frac{\theta}{2} - \Delta\theta \tag{4.15}$$

Equation 4.15 indicates that a fully uncontrolled circuit using the DC ripple reinjection concept is possible, but that alternative is limited to the use of only one reinjection bridge as in that case (using equation 4.7 for K=1)  $\alpha=0^{\circ}$ .

Figure 4.10 Minimum condition for  $\alpha$ .

## 4.3.5 Mean Rectified Voltage

Figure 4.11 shows a general output waveform for any pulse number. The mean rectified voltage  $V_{DC}$  of that waveform is

$$V_{DC} = \frac{1}{\beta} \int_{\alpha - \beta/2}^{\alpha + \beta/2} V \cos wt \, d(wt) = \frac{2V}{\beta} \sin \frac{\beta}{2} \cos \alpha \tag{4.16}$$

Figure 4.11 Output voltage of any convertor.

Applying equation 4.16 to the conventional configuration yields

$$V=V_x$$

$eta= heta$  .  $V_{XDC}=rac{2V_x}{ heta}\sinrac{ heta}{2}\coslpha$  (4.17)

and in the case of the modified configuration

$$V = V_Z$$

$$\beta = \Delta \theta$$

$$V_{ZDC} = \frac{2V_Z}{\Delta \theta} \sin \frac{\Delta \theta}{2} \cos \alpha$$

(4.18)

The increased mean rectified voltage  $\triangle V_{DC}$  is

$$\Delta V_{DC} = \frac{V_{ZDC} - V_{XDC}}{V_{XDC}} = \frac{V_{ZDC}}{V_{XDC}} - 1$$

and substituting equations 4.17 and 4.18

$$rac{V_{ZDC}}{V_{XDC}} = rac{ heta V_Z \sin riangle heta/2}{ riangle heta V_X \sin heta/2}$$

Observing an equal length of phasors  $\dot{V}_Z$  in Figure 4.4

$$V_Z = V_{Z1} = V_{Z1'} = \frac{V_X}{\cos\left(\frac{\theta}{2} - \frac{\triangle\theta}{2}\right)} \tag{4.19}$$

Then

$$\frac{V_Z}{V_X} = \frac{1}{\cos\left(\frac{\theta}{2} - \frac{\triangle\theta}{2}\right)}$$

Finally combining the above equations

$$\Delta V_{DC}\% = \left[ \frac{\theta \sin \Delta \theta / 2}{\Delta \theta \sin \theta / 2 \cos \left( \frac{\theta}{2} - \frac{\Delta \theta}{2} \right)} - 1 \right] 100 \tag{4.20}$$

Where  $\Delta \theta$  is defined in equations 4.7 and 4.8.

# 4.3.6 Asymmetrical Effect on Waveform $v_z$

Although the AC current is well behaved for any increase of current steps, from the point of view of  $v_Z$  only the simplest case, a single feedback bridge in the reinjection circuit, leads to a perfect pulse multiplication as phasors  $\dot{V}_Z$  in Figure 4.4 have the same length and there is no restriction for  $\alpha$  as  $\alpha_{MIN}=0$  in equation 4.15.

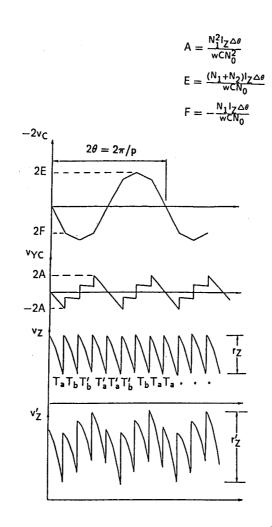

Figure 4.12 shows the increase of ripple due to the asymmetry of  $v_Z$  illustrated in Figure 4.4.

Figure 4.12 Illustration of ripple increase.

Clearly in Figure 4.12 the consideration of the smallest vector  $\dot{V}_X$  of Figure 4.4 leads to a ripple increase  $\triangle r$  which becomes zero as  $\alpha$  approaches 90° and is defined as follows:

$$\Delta r = (V_Z - V_X)\cos(\alpha + \Delta\theta/2) \qquad \text{for } \alpha \le (\pi/2 - \Delta\theta/2)$$

$$\Delta r = 0 \qquad \text{for } (\pi/2 - \Delta\theta/2) \le \alpha \le (\pi/2 + \Delta\theta/2)$$

$$\Delta r = (V_X - V_Z)\cos(\alpha - \Delta\theta/2) \qquad \text{for } \alpha \ge (\pi/2 + \Delta\theta/2)$$

$$(4.21)$$

and

$$r_Z = V_Z[\cos(\alpha - \triangle \theta/2) - \cos(\alpha + \triangle \theta/2)]$$

$$r_Z = 2V_Z \sin \alpha \sin(\Delta \theta/2)$$

for  $\Delta \theta/2 \le \alpha \le (\pi - \Delta \theta/2)$  (4.22)

where  $V_X$  and  $V_Z$  are defined in equations 4.11 and 4.19, respectively.

The ripple increase indicated in equation 4.21 is valid only if  $T_{K+1}$  is considered, as in that case the smallest vector in Figure 4.4 is  $\dot{V}_X$ . Otherwise the smallest vector is not in the middle point but displaced by an angle  $\theta/4K$  ( $\theta_i(i=K)$  in equation 4.13), thus  $V_X$  must be replaced by  $V_X/\cos(\theta/4K)$  in equation 4.21.

Figure 4.13 illustrates two cases with  $T_{K+1}$  omitted and K=2 (24-pulse and 48-pulse configurations).

Figure 4.13 Two examples of ripple increase.

# 4.4 Derivation of Current Waveforms

# 4.4.1 Current Analysis on DC Side

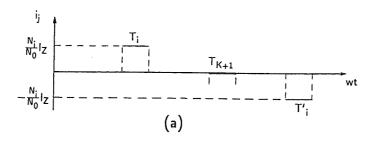

With reference to Figure 4.14 consideration is now given to the behaviour of current  $i_j$  under the assumption that  $I_Z$  is perfectly smooth.

Figure 4.14 Current in feedback transformers.

Figure 4.14 considers a generic bridge i and explains the derivation of current  $i_j$  for the two conducting modes, i.e. when thyristors  $T_i$  or  $T_i'$  conduct.

Equalising ampere-turns in Figure 4.14, when any thyristor  $T_i$  conducts

$$I_Z N_i = i_i N_0$$

and

$$i_j = \frac{N_i}{N_0} I_Z$$

Similarly when any thyristor  $T_i'$  conducts

$$I_Z N_i = -i_i N_0$$

and

$$i_j = -\frac{N_i}{N_0} I_Z$$

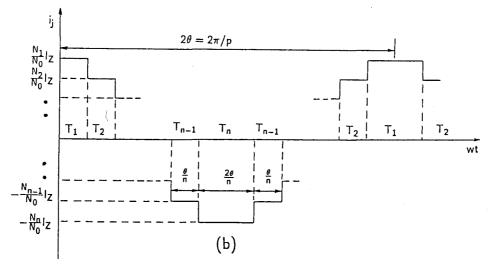

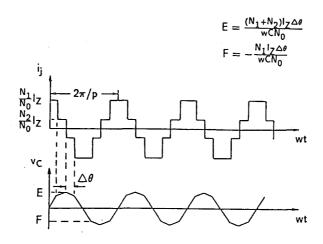

This is represented in Figure 4.15a, which also shows that when thyristor  $T_{K+1}$  conducts  $i_j$  reduces to zero. The general waveform of  $i_j$  is illustrated in Figure 4.15b taking into consideration Figure 4.5.

In figure 4.14 currents  $i_{j1}$  and  $i_{j2}$  with a frequency p times the fundamental, circulate through the appropriate main thyristors and phase windings, the first in the clockwise direction and the second in the anti-clockwise direction. Thus currents  $i_{j1}$  and  $i_{j2}$  modify the waveform of the currents in all the windings including the primary and as a result, the distortion of the AC input current waveform reduces. This effect is self-evident in the waveforms  $i_R$  of Figures 4.18 and 4.19.

Current  $i_j$  composition. a) Construction b) General waveform Figure 4.15

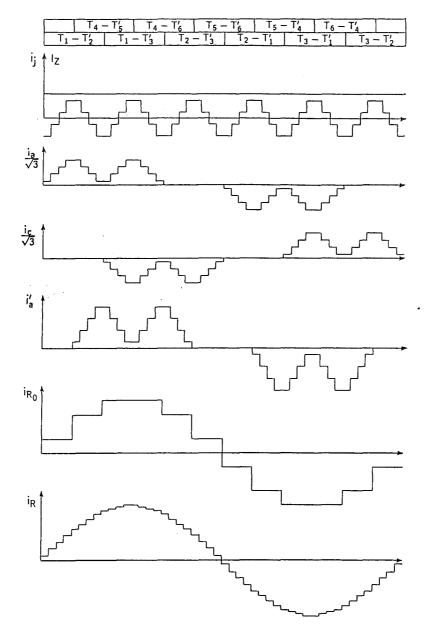

#### 4.4.2 Current Analysis on AC Side

Although the graphical procedure is generally applicable, the theoretical results illustrated relate to the specific circuits shown in Figures 4.16 and 4.17 (i.e. the 24-pulse and 48-pulse configurations respectively).

The following relationships apply to the circuit of Figure 4.16

$$N_{11}=N_{22}$$

(for simplicity)  $i_R=i_A-i_C=i_a-i_c$   $rac{N_1}{N_0}=0.717$   $rac{N_2}{N_0}=0.228$

Similarly for the circuit of Figure 4.17

$$N_{11} = N_{22} = \sqrt{3}N_{21}$$

(for simplicity)  $i_R = \frac{1}{\sqrt{3}}(i_a - i_c) + i_a'$   $rac{N_1}{N_0} = 0.742$   $rac{N_2}{N_0} = 0.245$

The most relevant current waveforms for the circuits of Figures 4.16 and 4.17 are shown in Figures 4.18 and 4.19 respectively. In Figure 4.18 subscript '0' identifies the currents produced by the conventional configuration and '1' the contribution of the reinjection current. For comparison the AC input current produced by the conventional configuration  $(i_{R_0})$  is also included.

Figure 4.16 24-pulse configuration.

Figure 4.17 48-pulse configuration.

Figure 4.18 Theoretical current waveforms of circuit shown in Figure 4.16.

Figure 4.19 Theoretical current waveforms of circuit shown in Figure 4.17.

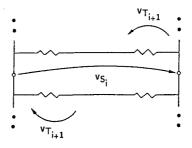

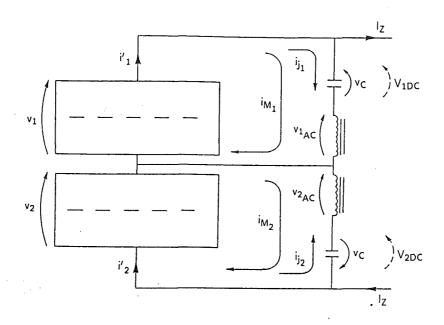

# 4.5 The Feedback Transformers

In Figure 4.20  $i_{M1}$  and  $i_{M2}$  are magnetizing currents so that the AC voltages  $v_{1AC}$  and  $v_{2AC}$  can be developed across the respective transformer primaries.

Figure 4.20 Magnetizing current of feedback transformers.

Even though  $i_{M1}$  and  $i_{M2}$  were not taken into consideration in the previous analysis, they play an important part in the design of the feedback transformers.

## 4.5.1 Minimum Load Current

Let us now analyse the electrical interrelation (voltage and current) between both convertors.

In Figure 4.20  $i'_1$  and  $i'_2$  include the output current  $I_Z$  and the superimposed AC currents  $i_{j1}$  and  $i_{j2}$  respectively, i.e.

$$i_1' = I_Z + i_{j1} = I_Z + i_j$$

$$i_2' = I_Z - i_{j2} = I_Z - i_j$$

Also from Figure 4.15

$$-i_j=i_j(wt-\pi/p)$$

and therefore

$$i_2' = i_1'(wt - \pi/p) \tag{4.23}$$

Finally from Figure 4.3

$$v_2 = v_1(wt - \pi/p) (4.24)$$

Equations 4.23 and 4.24 show that the upper and lower loops are electrically the same, although displaced by an angle  $\pi/p$  and it is therefore sufficient to consider one of them.

In the upper loop  $i'_1$  must be sufficiently positive to compensate for the negative peak of  $i_{M1}$  because of the unidirectional behaviour of the convertors. Below a certain minimum load current  $I_{Zmin}$ , current  $i_{M1}$  cannot circulate freely, the primary no longer continues to provide the voltage  $v_{1AC}$ , the circuit reverts to a more complex intermittent conduction and in the limit  $I_Z = 0$ ,  $i_{M1}$  and  $v_{1AC}$  become zero.

# 4.5.2 Magnetising Current Calculation

Let us assume that the capacitors are large enough to neglect the effect of  $v_C$  and that  $I_Z$  is sufficient to enable the magnetising current  $i_{M1}$  to circulate freely; moreover, let us assume that full symmetry exists, so that transformers  $T_A$  are not saturated and therefore their inductance  $L_B$  remains constant.

Figure 4.21 Current waveforms on the dc side of the convertor.

With reference to Figure 4.21,  $v_{1DC}$  is given by

$$V_{1DC} = \frac{p}{2\pi} \int_{\alpha - \pi/p}^{\alpha + \pi/p} V_1 \cos \theta \, d\theta$$

$$V_{1DC} = \frac{V_1 p}{\pi} \sin(\pi/p) \cos \alpha \tag{4.25}$$

and  $i_{M1}$  must satisfy the following relationship

$$L_B rac{di_{M1}}{dt} = v_{1AC} = V_1 \cos wt - V_{1DC}$$

for  $(\alpha - \pi/p) < wt < (\alpha + \pi/p)$

Therefore