# Power Electronic Control of a Partial Core Transformer

Vijay Bendre

A thesis submitted for the degree of

Master of Engineering

in

Electrical and Electronic Engineering

at the

University of Canterbury

Christchurch, New Zealand.

Submitted: July 2009

Revised updated: July 2010

### **Abstract**

The research programme at the University of Canterbury includes the development and applications of partial core inductors and transformers for high voltage testing of generator insulation. Unlike a conventional full core transformer, a partial core transformer has no limbs and yokes. A partial core transformer is a compromise between a full core and coreless transformer. It is superior to its full core counterpart as far as cost, weight and ease of transportation are concerned.

Partial core transformers have a low magnetising reactance and hence draw a high magnetising current. This characteristic makes them a perfect fit in applications where the load is capacitive in nature, such as a.c. power frequency high voltage testing of generator insulation and cable testing etc.

The work carried out for this thesis focuses on automatically controlling the amount of reactive power on the supply side of a partial core transformer. The considered design includes a third winding around the existing two windings. A power electronic controller is connected to the third winding, which modifies the VAr absorption characteristics of the magnetically coupled supply winding.

Two options are considered to achieve continuous reactive power control in the partial core transformer as explained below.

First, a thyristor controlled reactor (TCR) is proposed as the VAr controller. It is modelled using PSCAD/EMTDC software. Simulations reveal the design criteria, overall performance and the limitations of the suggested proposal. The TCR connected tertiary winding takes the capacitive burden of the supply. The model demonstrates the ability of the automatically controlled TCR to provide a continuous

variation of reactive power without significant under or over compensation. This feature limits the supply current to its real component only, so the supply provides only the losses of the system.

Second, a voltage source converter is considered as the VAr controller. This is modelled in PSCAD/EMTDC and a hardware prototype is designed and built. Based on the analysis, the control algorithm (including a digital PI controller) is implemented using an 8 bit micro-controller, PIC18LF4680. The prototype is tested in the laboratory for both active and inductive load conditions as seen from the supply side. Performance of the hardware prototype is discussed in detail.

The PSCAD/EMTDC model and the hardware prototype successfully demonstrate the feasibility of a STATCOM controlled partial core transformer. The proposed system is capable of compensating a wide range of capacitive loads as compared with its TCR counterpart.

It is proved that the system is very robust and remains dynamically stable for a large system disturbance such as change in load from full capacitive to inductive and vice versa<sup>1</sup>. This confirms that the system is capable of providing continuous VAr control.

\_

<sup>&</sup>lt;sup>1</sup> As seen by the STATCOM

## Acknowledgement

First, I wish to express my deepest gratitude to my supervisors, Prof. Pat Bodger and Dr. Alan Wood. Without their continuing support, encouragement and advice, this work would have never been realised.

I would like to thank Prof. Neville Watson for his assistance and support. I am also thankful to Dr. Wade Enright for his continuous guidance.

I am very grateful to Marshall Clark, Mark Finnigan and Rachel Russ of Transpower New Zealand Ltd. for their very strong support and continuous encouragement for completing my thesis. I would like to extend my thanks to my colleagues at Transpower, Prabodha Paranavithana, Geoff Love, Sarah Probert, Steve Nutt Stephen Leong and Alex Joosten.

I am grateful to all laboratory staff for their support and encouragement. I am deeply thankful to Dudley Berry, Michael Cusdin, Ken Smart, Phillip Hoff, David Healy, Scott Lloyd and Nick Smith.

I acknowledge with thanks the financial support from Electric Power Engineering Centre (EPE Centre), University of Canterbury.

My gratitude extends to my fellow postgraduates who have helped me throughout the project. I would like to thank Lance, Jordan, Simon, Pramod, Bhaba, Fainan, Jeff and to all power system guys.

Finally, I would like to thank my mum, dad, Ajay and other family members for their constant love, support, patience and strong presence throughout the year.

# Technical papers published during Master of Engineering

- Vijay Bendre, Pat Bodger, Alan Wood, "Towards a practical partial core transformer - compensation of reactive power requirements with a VSC," the IASTED International Conference on Power and Energy Systems, Botswana, Africa, September 8-10, 2008.

- Vijay Bendre, Wade Enright, Simon Bell, Pat Bodger, "Field Experiences

Using a Prototype Open Core Resonating Transformer for A.c. High

Potential Testing of Hydro-generator Stators," TechCon 2008, Sydney,

Australia, 1-2 April 2008.

- Pat Bodger, Wade Enright, Simon Bell, Vijay Bendre, "Partial Core Transformers for HV Testing and Power Supplies," TechCon 2008, Sydney, Australia, 1-2 April, 2008.

- Vijay Bendre, Wade Enright, Simon Bell, Pat Bodger, "A.c. High Potential Testing of Large Hydro-generator Stators Using Open Core Transformers,"

15th International High Voltage Symposium, Slovenia, August 27-31, 2007.

- Vijay Bendre, Pat Bodger, Alan Wood, "Thyristor Controlled Three Winding Transformer as a Static VAr Compensator," presented at EEA-2007 conference, Auckland, June 15-16, 2007.

# **Table of Contents**

| ABS                                            | TRACT                                                |  |  |  |

|------------------------------------------------|------------------------------------------------------|--|--|--|

| ACF                                            | KNOWLEDGEMENT                                        |  |  |  |

| TEC                                            | CHNICAL PAPERS PUBLISHED                             |  |  |  |

| TAB                                            | BLE OF CONTENTS                                      |  |  |  |

|                                                |                                                      |  |  |  |

| CHA                                            | APTER 1                                              |  |  |  |

| INT                                            | RODUCTION                                            |  |  |  |

| 1.1                                            | A full core transformer                              |  |  |  |

| 1.2 Introduction to a partial core transformer |                                                      |  |  |  |

|                                                | 1.2.1 High voltage partial core resonant transformer |  |  |  |

| 1.3                                            | Research objectives                                  |  |  |  |

| 1.4                                            | Outline of the thesis                                |  |  |  |

|                                                |                                                      |  |  |  |

| CHA                                            | APTER 2                                              |  |  |  |

| PRE                                            | CVIOUS WORK ON PARTIAL CORE SYSTEMS                  |  |  |  |

| 2.1                                            | Onestina                                             |  |  |  |

| 2.1                                            | Overview                                             |  |  |  |

| 2.2                                            | Research carried out on partial core transformers    |  |  |  |

|                                                | 2.2.1 Generator insulation testing                   |  |  |  |

|                                                | 2.2.1.1 Overview of high potential tests             |  |  |  |

|                                                | 2.2.1.2 Resonant inductor                            |  |  |  |

|                                                | 2.2.1.3 HV partial core resonating transformer       |  |  |  |

|                                                | 2.2.2 High current transformer                       |  |  |  |

|       | 2.2.3 High temperature superconducting (HTS)                                               |  |  |

|-------|--------------------------------------------------------------------------------------------|--|--|

|       | transformer                                                                                |  |  |

|       | 2.2.4 Energization of high voltage arc-signs                                               |  |  |

| 2.3   | Summary                                                                                    |  |  |

|       |                                                                                            |  |  |

| CHA   | APTER 3                                                                                    |  |  |

|       | HYRISTOR CONTROLLED THREE WINDING ANSFORMER AS A STATIC VAR COMPENSATOR                    |  |  |

| IKA   | INSPORVIER AS A STATIC VAR COVII ENSATOR                                                   |  |  |

| 3.1   | Overview                                                                                   |  |  |

| 3.2   | Thyristor controlled reactor (TCR)                                                         |  |  |

| 3.3   | Parameters of a single phase three winding transformer                                     |  |  |

| 3.4   | Concept of thyristor controlled three winding transformer                                  |  |  |

| 3.5   | Design value for series reactor (X <sub>L</sub> )                                          |  |  |

| 3.6   | Modelling in PSCAD/EMTDC.                                                                  |  |  |

| 3.7   | Automatic control.                                                                         |  |  |

|       | 3.7.1 Reactive power                                                                       |  |  |

|       | 3.7.2 Currents.                                                                            |  |  |

|       | 3.7.3 Voltages                                                                             |  |  |

|       | 3.7.4 VA gain                                                                              |  |  |

|       | 3.7.5 Real power                                                                           |  |  |

| 3.8   | Limitations of TCR applications.                                                           |  |  |

| 3.9   | Summary                                                                                    |  |  |

|       |                                                                                            |  |  |

| CHA   | APTER 4                                                                                    |  |  |

|       | DELLING, ANALYSIS AND DESIGN OF A SINGLE PHASE LTAGE SOURCE CONVERTER (VSC) BASED STATCOM. |  |  |

| V 012 | THISE SOCKED CONVERTER (VSC) BRISED STITL CONT                                             |  |  |

| 4.1   | Overview                                                                                   |  |  |

| 4.2   | Introduction                                                                               |  |  |

| 4.3   | Modelling and analysis of a single phase VSC based STATCOM                                 |  |  |

| 4.4   | Concept of STATCOM controlled partial core transformer                                     |  |  |

| 4.5   | Design of the STATCOM.                                                                     |  |  |

|       | 4.5.1 Current rating of the STATCOM                                                        |  |  |

|           | 4.5.2                                            | Determination of series inductance (L <sub>s</sub> ) |  |  |

|-----------|--------------------------------------------------|------------------------------------------------------|--|--|

|           | 4.5.3                                            | Choosing the value of d.c. capacitor $(C_{dc})$      |  |  |

| 4.6       | Transfer functi                                  | on for a single phase STATCOM                        |  |  |

| 4.7       | Determining p                                    | arameters for PI controller                          |  |  |

|           | 4.7.1                                            | Case1: A full capacitive load                        |  |  |

|           | 4.7.2                                            | Case2: A full inductive load                         |  |  |

| 4.8       | Control system                                   | structure                                            |  |  |

| 4.9       | Dynamic perfo                                    | ormance of the VSC based STATCOM                     |  |  |

|           | 4.9.1                                            | Voltage quality                                      |  |  |

| .10       | Summary                                          |                                                      |  |  |

|           |                                                  |                                                      |  |  |

| <b>HA</b> | APTER 5                                          |                                                      |  |  |

| RO        | POSED SINGI                                      | LE PHASE VSC BASED STATCOM                           |  |  |

| 5.1       | Overview                                         |                                                      |  |  |

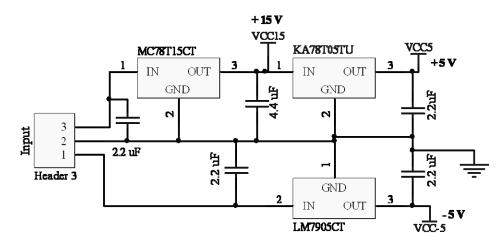

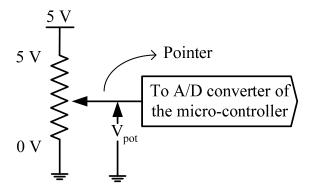

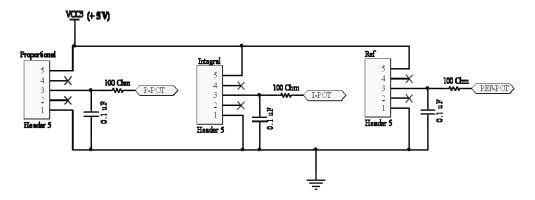

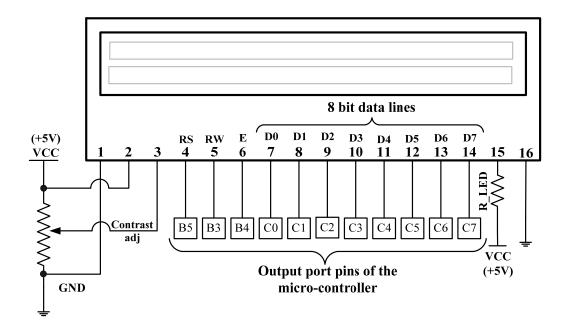

| 5.2       | Regulated dual power supply                      |                                                      |  |  |

| 5.3       | Micro-controller PIC18LF4680                     |                                                      |  |  |

| 5.4       | Sensing the control system parameters            |                                                      |  |  |

| 5.5       | Sensing reactive component of the supply current |                                                      |  |  |

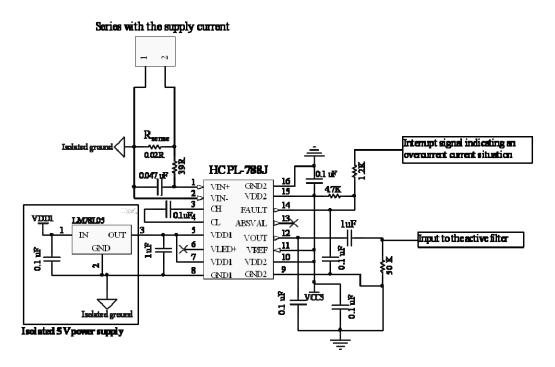

|           | 5.5.1                                            | Measurement of the supply current, I <sub>s</sub>    |  |  |

|           |                                                  | 5.5.1.1 Selecting a value for R <sub>sense</sub>     |  |  |

|           | 5.5.2                                            | Nature of the harmonic distortion problem            |  |  |

|           | 5.5.3                                            | Dual channel active filter design.                   |  |  |

|           | 5.5.4                                            | True r.m.s to d.c. converter, AD536A                 |  |  |

|           | 5.5.5                                            | Determination of the phase angle, $\theta$           |  |  |

|           |                                                  | 5.5.5.1 Detection and measurement of a phase         |  |  |

|           |                                                  | angle, $\theta$ , when it is lagging                 |  |  |

|           |                                                  | 5.5.5.2 Detection and measurement of a phase         |  |  |

|           |                                                  | angle, $\theta$ , when it is leading                 |  |  |

|           |                                                  | 5.5.5.3 Unity power factor situation                 |  |  |

|           | 5.5.6                                            | Computing the magnitude of I <sub>q</sub>            |  |  |

|           |                                                  |                                                      |  |  |

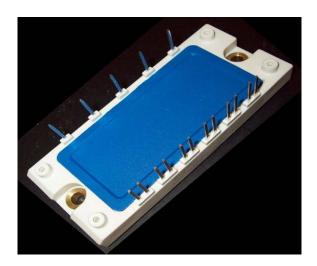

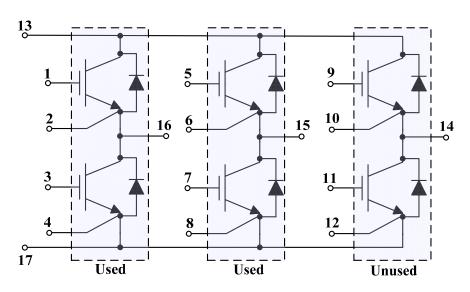

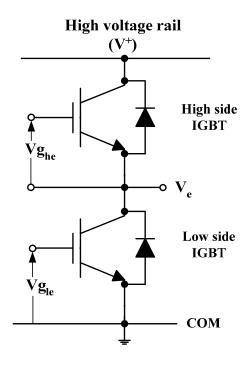

| OM<br>verview           | Selection Driver res                            | of IGBTs for the 'H' bridge inverter quirements for the high and low side IGBTs of the IGBT driver IC ing parameters for the bootstrap circuit Selecting a bootstrap diode    |

|-------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2.1<br>6.2.2<br>6.2.3 | Selection Driver res Selection Determin 6.2.4.1 | of IGBTs for the 'H' bridge inverter quirements for the high and low side IGBTs of the IGBT driver IC ing parameters for the bootstrap circuit Selecting a bootstrap diode    |

| 6.2.1<br>6.2.2<br>6.2.3 | Selection Driver res Selection Determin 6.2.4.1 | of IGBTs for the 'H' bridge inverter quirements for the high and low side IGBTs of the IGBT driver IC ing parameters for the bootstrap circuit Selecting a bootstrap diode    |

| 6.2.1<br>6.2.2<br>6.2.3 | Selection Driver res Selection Determin 6.2.4.1 | of IGBTs for the 'H' bridge inverter  quirements for the high and low side IGBTs of the IGBT driver IC  ing parameters for the bootstrap circuit  Selecting a bootstrap diode |

| 6.2.2<br>6.2.3          | Driver red<br>Selection<br>Determin<br>6.2.4.1  | quirements for the high and low side IGBTs of the IGBT driver ICing parameters for the bootstrap circuit  Selecting a bootstrap diode                                         |

| 6.2.3                   | Selection<br>Determin<br>6.2.4.1                | of the IGBT driver IC ing parameters for the bootstrap circuit Selecting a bootstrap diode                                                                                    |

|                         | Determin 6.2.4.1                                | ing parameters for the bootstrap circuit  Selecting a bootstrap diode                                                                                                         |

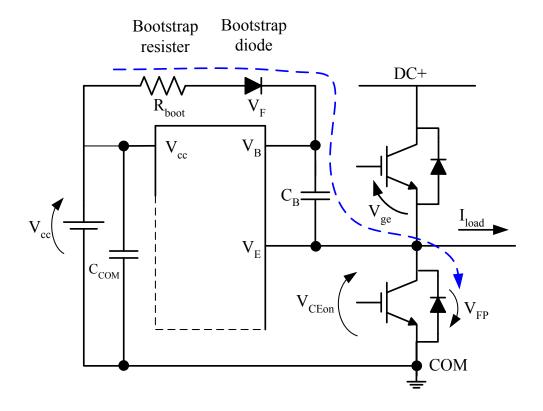

| 6.2.4                   | 6.2.4.1                                         | Selecting a bootstrap diode                                                                                                                                                   |

|                         |                                                 |                                                                                                                                                                               |

|                         | 6.2.4.2                                         | Selecting a bootstrap capacitor, C <sub>B</sub>                                                                                                                               |

|                         |                                                 |                                                                                                                                                                               |

|                         | 6.2.4.3                                         | Selecting the size of the capacitor, $C_{COM}$ ,                                                                                                                              |

|                         |                                                 | from V <sub>CC</sub> to COM                                                                                                                                                   |

|                         | 6.2.4.4                                         | Boot strap resistor                                                                                                                                                           |

| 6.2.5                   |                                                 | stance, R <sub>G</sub>                                                                                                                                                        |

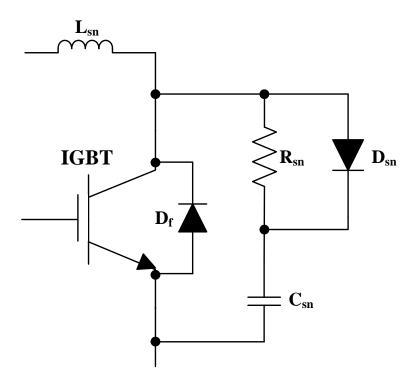

| 6.2.6                   |                                                 | circuit considerations for the IGBT                                                                                                                                           |

|                         | 6.2.6.1                                         | Choosing snubber component values                                                                                                                                             |

|                         | 6.2.6.2                                         | Design of the snubber circuit                                                                                                                                                 |

| 6.2.7                   | D.C. link                                       |                                                                                                                                                                               |

| 6.2.8                   |                                                 | on of the snubber design                                                                                                                                                      |

| 6.2.9                   | Current 1                                       | imiting reactor, L <sub>s</sub>                                                                                                                                               |

| 6.2.10                  | Capacito                                        | on the d.c. side                                                                                                                                                              |

| mmary                   |                                                 |                                                                                                                                                                               |

|                         | 6.2.7<br>6.2.8<br>6.2.9<br>6.2.10               | inverter 6.2.6.1 6.2.6.2 6.2.7 D.C. link 6.2.8 Verification 6.2.9 Current line 6.2.10 Capaciton                                                                               |

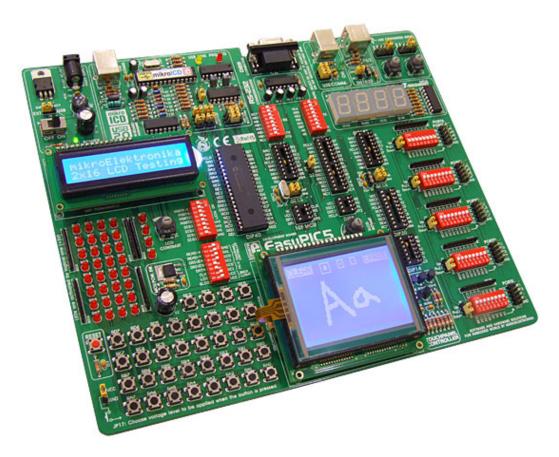

|   |               | MikroICD                                            |

|---|---------------|-----------------------------------------------------|

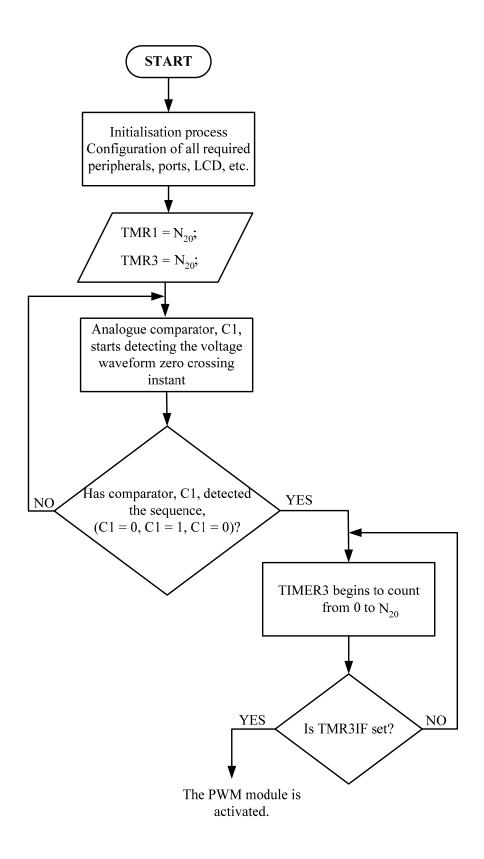

|   | 7.2.2         | Initialization process                              |

|   | 7.2.3         | Synthesis of SPWM in PSCAD/EMTDC                    |

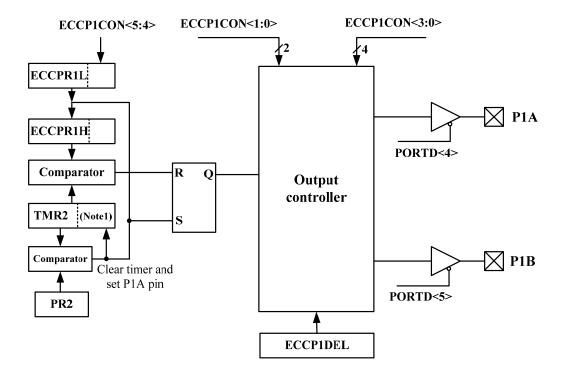

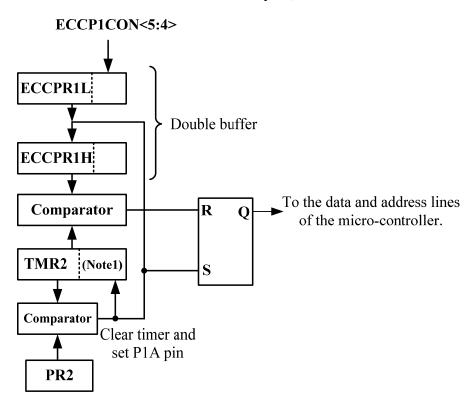

|   | 7.2.4         | Structure of the enhanced PWM module embedded       |

|   |               | inside the micro-controller                         |

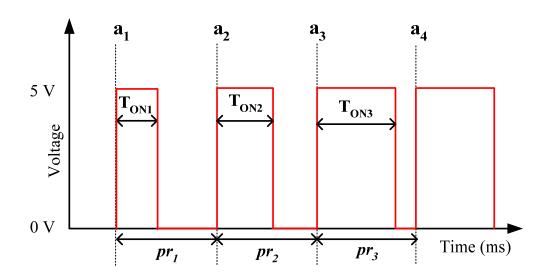

|   |               | 7.2.4.1 Specifying PWM period                       |

|   |               | 7.2.4.2 Specifying ON time for each pulse           |

|   |               | 7.2.4.3 Setting dead band delay time                |

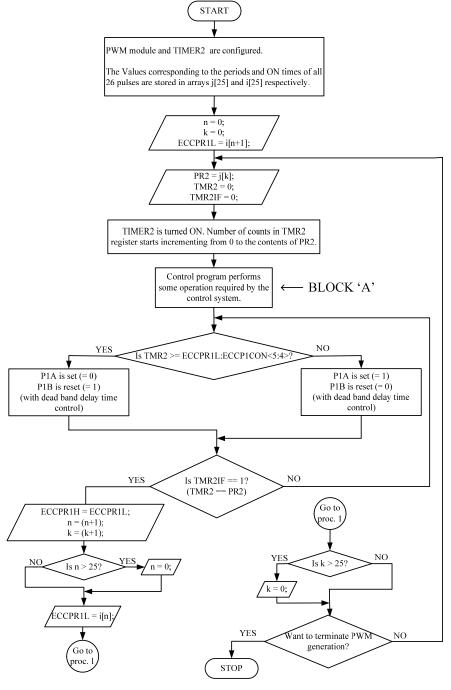

|   | 7.2.5         | SPWM generation by the micro-controller             |

|   | 7.2.6         | Mathematical calculations and implementing the      |

|   |               | control system                                      |

|   |               | 7.2.6.1 Operations performed during first of six    |

|   |               | cycles (0 to 20 ms)                                 |

|   |               | 7.2.6.2 Operations performed during third cycle     |

|   |               | (20 ms to 40 ms)                                    |

|   |               | 7.2.6.3 Operations performed during fourth          |

|   |               | cycle (40 ms to 60 ms)                              |

|   |               | 7.2.6.4 Operations performed during fifth cycle     |

|   |               | (60 ms to 80 ms)                                    |

|   |               | 7.2.6.5 Operations performed during sixth cycle     |

|   |               | (80 ms to 100 ms)                                   |

|   |               | 7.2.6.6 Operations performed during second          |

|   |               | cycle (100 ms to 120 ms)                            |

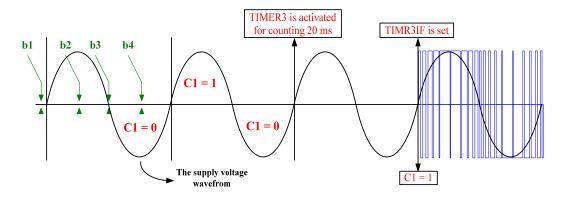

| 3 | Shifting SPWN | M waveform with respect to the supply voltage       |

| J | waveform      |                                                     |

|   | 7.3.1         | The waveform is shifted earlier with respect to the |

|   |               | supply voltage by the delay angle, $\delta$         |

|   | 7.3.2         | The waveform is synchronized with the zero          |

|   |               | crossing of the supply voltage.                     |

|   | 7.2.2         | The waveform is shifted later with respect to the   |

|   | 7.3.3         | The waveform is shifted later with respect to the   |

|            | ULTS AND DI      |                                                       |

|------------|------------------|-------------------------------------------------------|

| 8.1        | Overview         |                                                       |

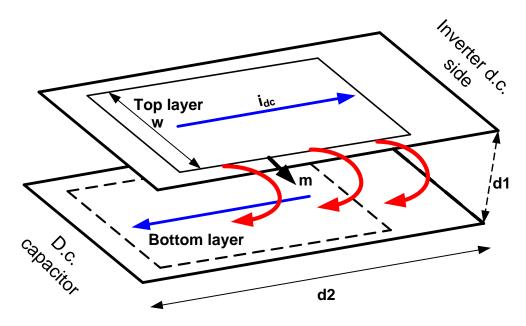

| 8.2        | Experimental s   | set up                                                |

| 8.3        | Electric param   | eters of the system.                                  |

|            | 8.3.1            | Supply current                                        |

|            |                  | 8.3.1.1 When a load seen from the supply side         |

|            |                  | inductive in nature                                   |

|            |                  | 8.3.1.2 When a load seen from the supply side         |

|            |                  | capacitive in nature                                  |

|            | 8.3.2            | Total harmonic distortion in currents flowing         |

|            |                  | through the three windings                            |

|            | 8.3.3            | VA gain for the supply winding                        |

|            | 8.3.4            | Real power losses                                     |

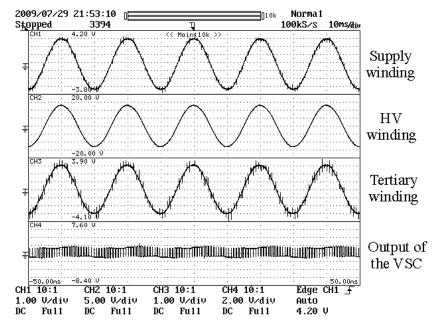

|            | 8.3.5            | Voltage waveforms across the terminals of all the     |

|            |                  | three windings under different load conditions        |

| 8.4        | Summary          |                                                       |

|            |                  |                                                       |

| СНА        | PTER 9           |                                                       |

| CON<br>WOI |                  | ND RECOMMENDATIONS FOR FUTURE                         |

| 9.1        | Introduction     |                                                       |

| 9.2        | Applying a thy   | ristor controlled static VAr compensator to a partial |

|            | core transform   | er                                                    |

|            | 9.2.1            | Limitations of the TCR application                    |

|            | 9.2.2            | Suggestions for overcoming the limitations            |

| 9.3        | Applying a vo    | ltage source converter (VSC) to the third winding of  |

|            | a partial core t | ransformer                                            |

|            | 0.2.1            | Software part of the project                          |

|            | 9.3.1            | Software part of the project                          |

|            | 9.3.1            | Hardware part of the project                          |

| 9.4.1      | Implementing the TCR control in partial core  |     |

|------------|-----------------------------------------------|-----|

|            | transformers                                  | 127 |

| 9.4.2      | Implementing the VSC based STATCOM in partial |     |

|            | core transformers.                            | 127 |

| REFERENCES |                                               | 129 |

# Chapter 1

### Introduction

#### 1.1 A full core transformer

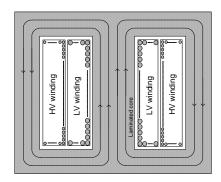

A transformer is a stationary apparatus which transforms electric power in one circuit into electric power of the same frequency in another circuit at a different voltage [1]. A conventional single phase power transformer has two windings separated electrically but linked magnetically by a path of low reluctance i.e. through a closed or full core of ferromagnetic material, as shown in Figure 1.1. Generation of a high core flux density using a relatively low magnetising current is possible because of the high permeability of the ferromagnetic core. Transformer designs with high voltages per turn for the windings are possible due to the ferromagnetic core, which minimises the lengths of the winding material used and hence lowers the copper losses [2]. These features cannot be accomplished in a cost effective, light weight, coreless transformer. The percentage magnetising current in a coreless transformer is a much higher percentage of its total current rating.

Figure 1.1: A full core transformer

#### 1.2 Introduction to a partial core transformer

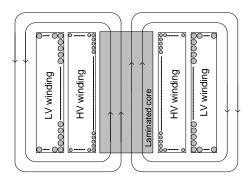

A compromise between a full core and coreless transformer is a partial core transformer. It consists of a laminated ferromagnetic central core around which the primary and the secondary windings are wound. The outer limbs and the yokes are absent as shown in figure 1.2.

Figure 1.2: A partial core transformer

Partial core transformers have different characteristics from full core transformers as the flux path is a combination of steel and air. Keeping all other parameters constant such as supply voltage, cross sectional area and number of turns on the excitation, the theoretical flux density is the same for both a full core and a partial core transformer. In the case of a partial core transformer, the flux path reluctance is much higher, leading to a lower magnetising reactance and higher magnetising current. However, it has better magnetisation than a coreless transformer and maintains the leakage flux at an acceptable level. This also means that the overall weight and volume of the partial core units can be significantly reduced. They are also easy to manufacture [3, 4].

#### 1.2.1 High voltage partial core resonant transformer

Partial core transformers are better suited to applications such as supplying capacitive loads, and/or where factors such as cost, size and ease of transportation are critical. Since 2002, the University of Canterbury has designed, built and

developed partial core transformers [5-8]. One of the most significant results is the development of a high voltage (HV) partial core resonating transformer for a.c. power frequency testing of a hydro-generator.

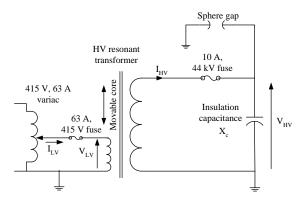

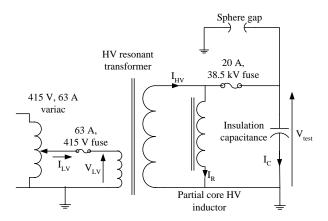

Figure 1.3: Circuit diagram for performing HV power frequency test with only a HV partial core resonating transformer

Figure 1.3, shows the circuit diagram for performing an a.c. high potential test at power frequency by a high voltage partial core resonant transformer. In order to limit the supply current to its real component only, the generator insulation capacitance ( $X_c$ ) is resonated with the magnetizing reactance ( $X_m$ ) of the partial core transformer by manually adjusting its central core. Figure 1.4 shows a light utility vehicle transporting the HV partial core resonating transformer. Many of the hydrogenerators in the South Island of New Zealand have been tested by using this transformer [9, 10].

Figure 1.4: A light utility vehicle transporting the dry type partial core resonating HV transformer

#### 1.3 Research objectives

Manual position adjustment of the core has some limitations due to the involvement of large magnetic forces, necessary proximity of the operator to the high voltage and the possibility of under or over compensation. In order to overcome these problems, there is a need for a means of continuous control of reactive power.

With this objective, a third winding is proposed around the already existing two windings, along the direction of the main field flux. Due to magnetic coupling, an e.m.f. will be generated in the third winding. A controller can be put on the third winding which is responsible for modifying the VAr absorption characteristics of that winding for compensating the capacitive VArs required by the HV winding [11]. This will limit the supply current. Two independent strategies have been proposed for limiting the magnitude of current drawn from the supply side, namely

- 1. Applying a thyristor controlled static VAr compensator to the third transformer winding.

- 2. Applying a single phase voltage source converter (VSC) based static compensator (STATCOM) to the third transformer winding.

The first proposed scheme works only if a load seen by the supply side is capacitive in nature. Application of a switched capacitor bank may need a.c. capacitors with a large energy storage capacity, which are expensive and bulky. This option does not offer continuous VAr control. A VSC based STATCOM overcomes limitations of both the VAr compensating schemes. These converters are able to use electrolytic capacitors, this is a much cheaper and cost effective option rather than going for a.c. capacitors. A VSC based STATCOM provides both capacitive and inductive VArs. This enables a range of loads to be compensated by the system. A partial core transformer can be used like a full core transformer with the employment of the

second strategy, although significant current will be required to flow in the third transformer winding.

#### 1.4 Outline of the thesis

The performance of a TCR application to a three winding partial core transformer is evaluated by simulating the proposed scheme using PSCAD/EMTDC software. Hardware prototype of a single phase VSC based STATCOM is designed, built and tested in the laboratory for evaluating its performance.

Chapter 2 describes previous work carried out on partial core machinery in the University of Canterbury. The partial core machines designed, developed and built for applications such as high voltage resonant inductor and transformer for a.c. power frequency high voltage testing of a generator insulation, high current transformer for testing current transformers, high temperature superconducting transformer etc.

Chapter 3 introduces the thyristor controlled three winding transformer. Parameters of the selected single phase three winding transformer are determined by performing open and short circuit tests on it. The system is modelled and simulated using PSCAD/EMTDC software for evaluating its performance and limitations.

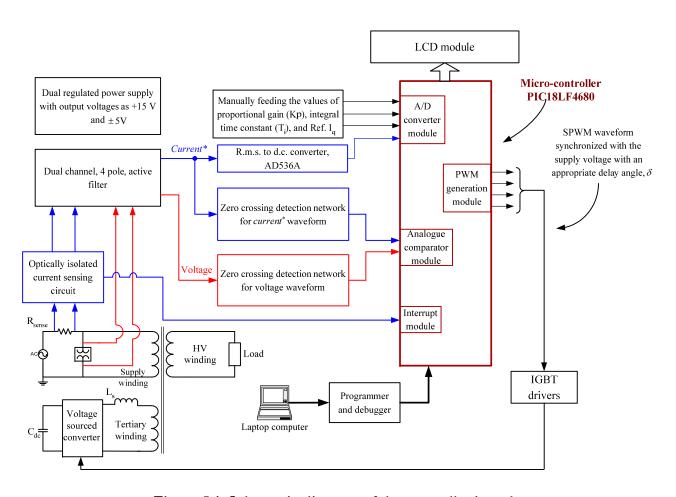

Chapter 4 covers the theory, modelling, analysis and design of a single phase VSC based STATCOM. The chapter also illustrates the design criteria for implementing a proportional- integral (PI) based closed loop automatic control system. The scheme is modelled in PSCAD/EMTDC software for verifying dynamic as well as steady state performance of the system.

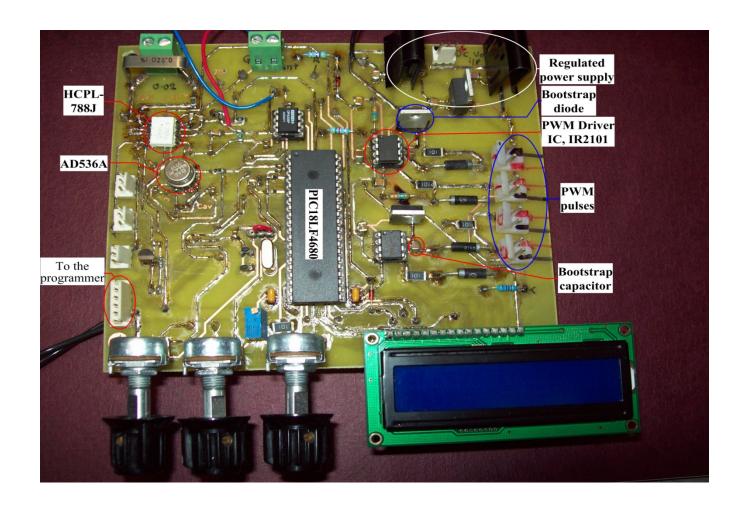

Chapter 5 describes the development of the controller board built to implement the proposed automatic control system. The hardware and methodology used for the accurate measurement of the reactive component of the supply current is presented.

Chapter 6 explains the design and development of the power circuit. The power circuit consists of an IGBT based 'H' bridge inverter, driver circuits, snubber circuit, a current limiting series inductor to be inserted in the tertiary winding, a capacitor on the d.c. side of the VSC etc.

Chapter 7 explains the control algorithm developed for programming the micro-controller, PIC18LF4680. The micro-controller is responsible for generation of a sinusoidal pulse width modulated waveform (SPWM) and synchronising it with the supply voltage waveform, data acquisition, A/D conversion, performing the mathematical operations, and shifting the SPWM waveform earlier or later with respect to the supply voltage waveform to achieve the required VAr compensation on the supply side.

Chapter 8 demonstrates the performance of the prototype built for a range of load conditions.

Chapter 9 presents conclusions drawn from the research effort and discusses possible future work related to both the schemes proposed.

## Chapter 2

## Previous work on partial core systems

#### 2.1 Overview

In the previous chapter, the partial core transformer was introduced. This chapter describes the previous work carried out at the University of Canterbury in the area of partial core machinery.

#### 2.2 Research carried out on partial core transformers

#### 2.2.1 Generator Insulation Testing

#### 2.2.1.1 Overview of high potential tests

When generator stators are rewound or undergo major repairs, there is often a desire to perform a high potential test. These tests can be completed using d.c., very low frequency or power frequency a.c. test voltages. A.c. high potential tests are becoming more popular due to their superiority in many aspects over the alternatives. A.c. high-potential testing stresses the components of generator insulation in a manner more similar to normal service, except at higher a.c. voltages and in a non-induced or non-graded manner. Under a.c. conditions the amount of current drawn by the insulation capacitance depends in part on the physical dimensions of the stator winding.

As shown in Table 2.1, some of the hydro-generators in New Zealand have large values of stator insulation capacitance.

Table 2.1: Hydro-generators tested in New Zealand with their insulation capacitances

| Generator rating | Test<br>voltage<br>kV | Insulation<br>capacitance<br>µF | Calculated<br>kVAr | Calculated charging current at 230 V <sup>1</sup> |

|------------------|-----------------------|---------------------------------|--------------------|---------------------------------------------------|

| 2.35 MVA, 6.6 kV | 14.2                  | 0.084                           | 5.32               | 23                                                |

| 8.82 MVA, 6.6 kV | 14.2                  | 0.217                           | 13.8               | 60                                                |

| 55.55 MVA, 11 kV | 13.8                  | 0.234                           | 14                 | 61                                                |

| 88.9 MVA, 11 kV  | 23                    | 0.422                           | 70.1               | 305                                               |

| 120 MVA, 15.4 kV | 20                    | 0.75                            | 94.2               | 409                                               |

| 40 MVA, 11 kV    | 23                    | 0.57                            | 94.7               | 412                                               |

| 135 MVA, 13.8 kV | 32                    | 1.05                            | 338                | 1468                                              |

In most of the cases, the charging current required cannot be supplied by the power station local services without compensation. To overcome this problem, resonant systems are most popular among companies offering HV test equipment. Series and parallel resonant test systems are common for a.c. high-potential tests on generator insulation, so that under resonant conditions the energy absorbed at any instant by one reactive element is exactly equal to that released by another reactive element within the system. This self sustaining resonant system requires much less current from the power station distribution board.

Most of the expensive and heavy resonant testing systems employ full core electromagnetic machinery such as double shielded isolation transformers, voltage regulators, excitation transformers and high voltage reactors. Such machines can reach multiple tons in mass. Transportation of this heavy equipment is also expensive, especially when a hydro-generator is located remotely. These difficulties can discourage generator owners and force them to undertake a d.c. test. Some of the companies try to optimize size and weight considerations by increasing the frequency of the supply from d.c. to Very Low Frequency (V.L.F.), but this technique suffers from many of the criticisms already noted for the d.c. test [10].

8

<sup>&</sup>lt;sup>1</sup> Charging current without considering any losses and assuming an ideal HV transformer ratio

#### 2.2.1.2 Resonant Inductor

In 2002, a partial core HV inductor was designed and built in order to perform an a.c. high-potential test on a 40 MVA, 11 kV North Island hydro-electric power station generator. As shown in figure 2.1, the partial core inductor was connected in parallel with the generator insulation. The generator insulation capacitance can be resonated with the inductive reactance of the partial core inductor by using taps provided [9]. The final high potential test of the generator was conducted at 23 kV for one minute. The test set up is shown in figure 2.2.

Figure 2.1: Circuit diagram for performing HV power frequency test with a partial core resonating inductor

The generator stator insulation was measured at  $0.56~\mu F$  which corresponds to  $5700~\Omega$ . Under test, the stator insulation drew 4.1 A at 23 kV. The partial core resonant inductor actually over compensated the stator capacitance.

The supply current was reduced to 0.75 A, considerably below that which would have been necessary without the inductor in circuit. Thus a VA gain of 5.5 from the supply to the load was obtained. VA gain can be defined as the ratio of apparent power (VA) available on the output side of a transformer to the input VA supplied.

This permitted the use of a lower VA rating HV test supply transformer and variac, with smaller supply station and protection concerns [3].

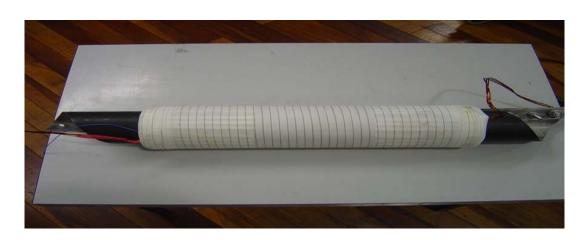

Figure 2.2: Test location for the partial core resonant inductor

#### 2.2.1.3 HV Partial core resonating transformer

In the case of a conventional transformer, the LV winding is wound on the inside next to the core, to reduce its length and hence the copper losses due to its relatively high current. A partial core resonant transformer has the LV wound around the HV winding. The LV winding acts a shield and prevents the HV winding from electric field coupling to grounds external to the transformer and thus the probability of corona from the windings is significantly reduced [3].

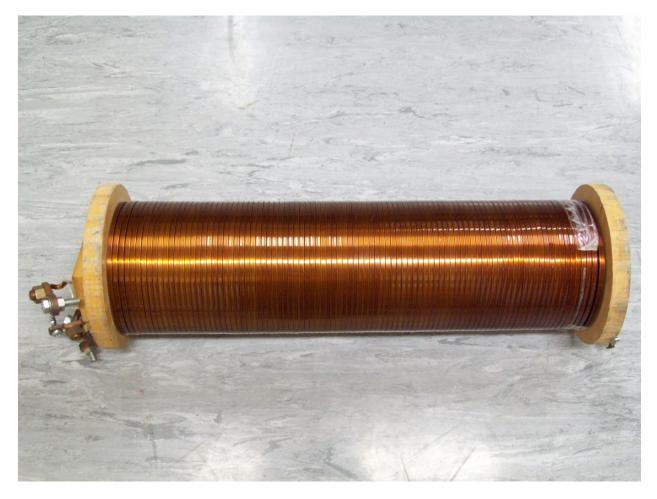

A HV partial core resonating transformer was first applied to test a 135 MVA, 13.8 kV hydro electric power station in the South Island of New Zealand. It was designed for a 334 kVAr capacitor load to perform the power frequency high voltage test at 31.5 kV. In practice, the resonant transformer used was to supply 36.5 kV to an initial batch of installed stator bars at 0.49  $\mu$ F, which is equal to a capacitive load of 205 kVAr. Under flashover situations, the transformer proved its electrical and mechanical integrity.

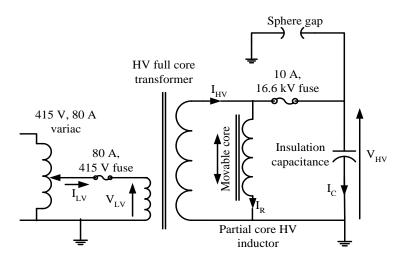

In a follow up test, it is required to test each complete phase of the generator stator of  $1.06~\mu F$  at 32~kV for one minute. The resonant inductor described in 2.1.2~was inserted in parallel with the resonant transformer. This high voltage testing assembly, as shown in figure 2.3, achieved a resonance of 340~kVA while drawing only 70~A from a single phase 415~V supply. The output to supply VA ratio was 11~[3].

Figure 2.3: Complete stator phase test with HV resonant transformer and inductor, both designed using partial core technology

Many of the hydro-generators in New Zealand were successfully tested with this compact HV resonant testing kit which weighs approximately 300 kg [3-5]. This has replaced a full core HV resonant testing kit weighing around 6 tonnes as shown in Figure 2.4.

Figure 2.4: Partial core HV resonant transformer in front of conventional full core high voltage testing kit (full core excitation transformer and inductors)

#### 2.2.2 High Current Transformer

Primary current injection is employed for testing current transformers and related equipment on power transmission and distribution metering and protection systems. Traditional high current transformers are bulky and heavy, hence they have limitations on the locations they can be placed in. This results in extra secondary cable lengths. With the low voltage, high current output characteristic of these transformers, the voltage drop in the cable is usually the limiting factor of the output current. A compact, lighter transformer can be placed close to the equipment under test, decreasing the effect of cable voltage drop, which results in the availability of higher current.

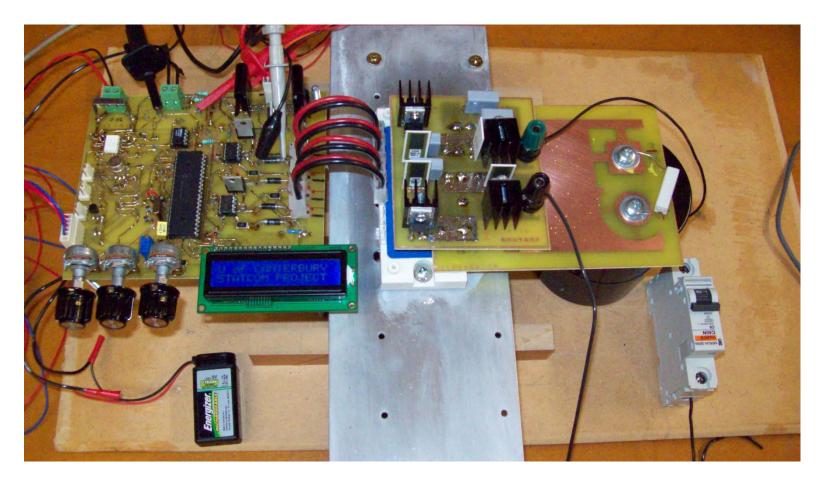

As shown in figure 2.5, a partial core high current transformer was designed and built for the purpose [8]. It weighted 39 kg. It is suitable for 4000 A continuously or 11000 A peak. Although the continuous rating met the specifications of a conventional transformer used for the purpose (weighing 147 kg), the peak current was limited due to excessive eddy current heating at the terminals of the secondary winding. The heating problem may be solved by laminating these terminations [3].

Figure 2.5: High current test transformer

#### 2.2.3 High Temperature Superconducting (HTS) Transformer

A prototype of a single phase, 15 kVA, 230/115 V, partial core HTS transformer was designed and built. The rated primary current for the transformer is 65.22 A.

The typical first generation HTS tape from American Superconductors has cross sectional dimensions of 4.1 mm by 0.305 mm. This means the effective tape area is 1.25 mm<sup>2</sup>. This gives the current density of 52.15 A/mm<sup>2</sup>. It has a minimum bend radius of 70mm.

The construction of the transformer was such that the core operates at normal temperatures while the windings were immersed in liquid nitrogen. The complete assembly was placed inside a double skinned/vacuum or permulite composite tank that provided insulation to the outside. The ends of the three windings made were accessible to allow variable location of the primary and secondary windings, and also to allow alternative two winding and autotransformer configurations.

The winding terminals were connected to the copper leads and brought out to terminals through a gaseous nitrogen headspace which cooled the leads. This reduced the conduction of heat from the outside into the liquid nitrogen [3]. The transformer is shown in figure 2.6.

Figure 2.6: A prototype of a partial core high temperature superconducting transformer

#### 2.2.4 Energization of high voltage arc-signs

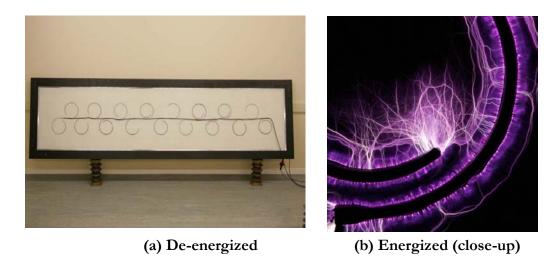

A collaborative study between the Departments' of Electrical and Computer Engineering and Fine Arts at the University of Canterbury has developed lightning arc drawings or "arc signs". These arc-signs require a high voltage to obtain their arcing effect. Figure 2.7(a), shows the basic arrangement of an arc-sign [12].

The configuration consists of a top electrode which forms the design, a sheet of insulating film (NMN 5-10-5), and a thin sheet of conductor which forms the bottom electrode. The arc sign is a parallel plate capacitor of very small value.

At rated voltage, power arcs appear on the surface of the sign. The power supply gets short circuited, although when the power arcs are being formed on the sign's surface, very little real power is dissipated.

Figure 2.7: The arc sign showing the top electrode and insulation layer

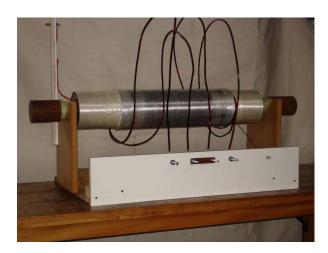

The partial core transformer designed for this purpose consists of two separate LV windings wound onto the outside of the HV winding. The two windings are connected in series by an external link to give the very high turns ratio required for an output voltage of 80 kV from a 230 V supply. The completed transformer along with the core weighs 69 kg. Figure 2.8 shows a photo of the transformer and its mounting arrangement.

Figure 2.8: 80 kV Transformer

Figure 2.7(b), shows one of the arc signs loaded by the transformer. The arc sign has a de-energized capacitance of 7 nF, corresponding to 450  $\Omega$  of capacitive load reactance, or 3.32  $\Omega$  when referred to the primary winding of the transformer.

The transformer can also be employed for flashing sphere gaps used for high voltage testing protection.

#### 2.3 Summary

A partial core transformer is a compromise between a full core and coreless transformer. It is superior to its full core counterpart as far as cost, weight and ease of manufacturing and transportation are concerned. A number of partial core inductors and transformers have been designed, developed and built. The lower magnetising reactance of a partial core transformer, with a capability of adjusting its magnitude, makes the partial core transformer a perfect fit for applications where loads are capacitive, such as a.c. power frequency high voltage testing of generator insulation. The generator stator insulation capacitance is resonated with the transformer magnetising reactance by adjusting the position of transformer's central core. This effectively eliminates the reactive power demand from the main power supply. Only the real power losses of the transformer, and any mismatch between the magnetisation current and the stator capacitance, are provided from the supply. A number of hydro-generators in New Zealand have been tested successfully with the partial core high voltage testing kit.

A high current partial core transformer was designed which can be used for testing current transformers. It can provide a continuous current of 4000 A.

The performance of a partial core high temperature superconducting transformer immersed in liquid nitrogen was evaluated. The superconducting transformer shows a very high magnetic flux coupling between the windings and a reduced percentage of leakage flux. This supports the possibility of real power transfer using partial core technology.

For displaying power arc-signs, a single phase, 80 kV partial core transformer was designed and built. This transformer operates near to an open circuit condition. It can be used to flash spheres for HV testing protection.

# Chapter 3

# A thyristor controlled three winding transformer as a static VAr compensator

#### 3.1 Overview

In chapter 2, a number of partial core transformers and their applications were discussed. This chapter describes a thyristor controlled three winding partial core transformer for controlling the amount of reactive power in the supply winding.

#### 3.2 Thyristor-Controlled Reactor (TCR)

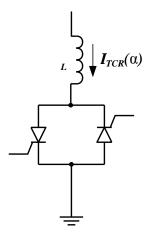

A basic single-phase thyristor-controlled reactor (TCR) is shown in Figure 3.1. It consists of a bi-directional thyristor valve and a fixed inductance L of reactance  $X_L$ . The fine tuning is achieved by varying the TCR firing delay angle ( $\alpha$ ). The controllable range of  $\alpha$  extends from 90° to 180°. A firing angle of 90° results in full thyristor conduction with a continuous sinusoidal current (i<sub>TCR</sub>) flowing through the TCR. As the firing angle is varied towards 180°, the current flows through the reactor ( $X_L$ ) in the form of discontinuous pulses symmetrically located in the positive and negative half cycles [13].

Figure 3.1: Thyristor controlled reactor

The firing angle is derived from the conduction angle equation in [14]. A relationship between the firing delay angle and the TCR reactance ( $X_{TCR}$ ) is given in equation 3.1.

$$X_{TCR} = \left(\frac{2[(\pi - \alpha)] + \sin 2\alpha}{\pi \omega L}\right)^{-1}$$

(3.1)

Equation 3.2, gives the range of reactance values which can be obtained from the TCR.

$$X_L \le X_{TCR} \le \infty \tag{3.2}$$

#### 3.3 Parameters of a single phase three winding transformer

An available partial core, three winding transformer was chosen on which to perform experiments, and simulations using the PSCAD/EMTDC software package. The transformer has ratings of 2.52 kVA, 90/345/90 V, and 50 Hz. In order to determine its parameters, short circuit and open circuit tests were performed on all the three windings. These parameters are presented in Table 3.1. Mathematical modelling of a three winding transformer can be found in [15].

Table 3.1 Electrical characteristics of the chosen partial core three winding transformer

| Parameter                               | Value                               | Unit |

|-----------------------------------------|-------------------------------------|------|

| Rated winding currents                  | 28/7.30/28                          | A    |

| Short circuit impedances                | $Z_{ps} = 0.296 + 0.308 j$          | Ω    |

| (All values are referred to the         | $Z_{\rm st} = 0.317 + 0.271  \rm j$ | Ω    |

| primary/supply winding )                | $Z_{pt} = 0.508 + 0.024 j$          | Ω    |

| Magnetising reactance (X <sub>m</sub> ) | 16.2                                | mН   |

| No load loss component                  | 73                                  | Ω    |

Where, p, s and t denote the primary (supply), secondary (high voltage), and tertiary (control) windings respectively.

- Z<sub>ps</sub> is the winding resistance and leakage inductance measured in the primary winding when the secondary winding is short circuited and the tertiary winding is kept open.

- Z<sub>st</sub> is the winding resistance and leakage inductance measured in the secondary winding when the tertiary winding is short circuited and the primary winding is kept open.

- Z<sub>pt</sub> is the winding resistance and leakage inductance measured in the tertiary winding when the primary winding is short circuited and the secondary winding is kept open.

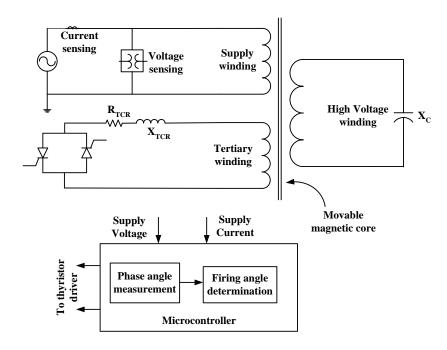

#### 3.4 Concept of thyristor controlled three winding transformer

As shown in Figure. 3.2, the tertiary winding of the three winding transformer is closed through an anti-parallel connected pair of thyristor valves. If the leakage reactance ( $X_{leakage}$ ) of this transformer is not high enough, an additional current limiting reactor ( $X_L$ ) in the tertiary winding is essential. In Fig. 3.2,  $X_{TCR}$  represents ( $X_{leakage} + X_L$ )\*.

Figure 3.2: Proposed thyristor controlled scheme for partial core three winding resonant transformer

-

<sup>\*</sup> In actual case, the value of  $X_{leakage}$  in the tertiary winding was very low as stated in equation 3.6.

$X_L$  is also essential for reducing the magnitude of harmonics that are not only detrimental to the test object and the transformer itself, but also an a.c. high potential test with polluted supply, may not be accepted as per standards.

Firing angle control of these thyristor valves provides a continuous variation of reactive power.  $R_{TCR}$  represents the internal resistance of the TCR when one of the thyristors is conducting.  $X_C$  denotes a capacitive load, e.g. generator insulation capacitance.

Automatic control of the TCR controlled three winding transformer can be achieved by using a compatible micro-controller [16]. Inputs to the micro-controller are the supply voltage and current waveforms.

#### 3.5 Design value for series reactor (X<sub>L</sub>)

The current rating of the tertiary winding is 28 A, while the voltage rating, V, is 90 V. The value of the series reactor,  $X_L$ , is calculated using equation 3.3 as 3.2  $\Omega$ . It was decided to operate the TCR at 85% of the full load current. This corresponds to an inductance value, L, of 12 mH.

$$X_L = -j \frac{V}{I_{TCR}} \tag{3.3}$$

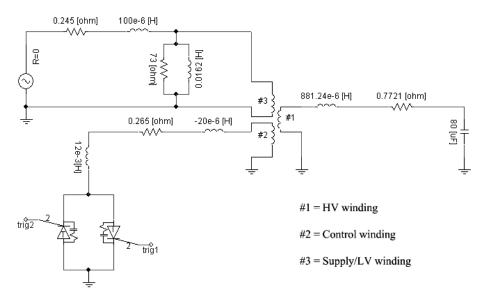

#### 3.6 Modelling in PSCAD/EMTDC

A basic model of a thyristor controlled three winding transformer as a SVC is shown in Figure 3.3. It implemented in PSCAD/EMTDC software. Equations for determining the values of the winding resistance and leakage reactance of the individual windings are derived in [15]. These equations are given as,

$$Z_p = \frac{1}{2} \left[ Z_{ps} + Z_{pt} - Z_{st} \right] = (0.245 + 0.0305i) \Omega$$

(3.4)

$$Z_{s} = \frac{1}{2} \left[ Z_{ps} + Z_{st} - Z_{pt} \right] = (0.7721 + 0.277i) \Omega^{\dagger}$$

(3.5)

$$Z_{t} = \frac{1}{2} \left[ Z_{pt} + Z_{st} - Z_{ps} \right] = (0.265 - 0.00628i) \Omega$$

(3.6)

It can be observed that the tertiary winding short circuit reactance has a negative value. This characteristic is discussed in [17]. The three winding transformer model block set available in the PSCAD/EMTDC library, is treated as an ideal one with no saturation.

Values of resistance and self inductance for each winding can be calculated by using equations 3.4 to 3.6. Both open and short circuit parameters are connected externally to the terminals of the ideal three winding transformer model as shown in Figure 3.3.

Figure 3.3: A model of the thyristor controlled three winding transformer in PSCAD/EMTDC

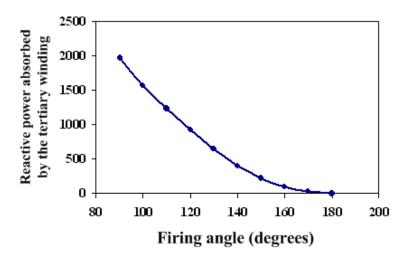

In order to identify the main characteristics of the TCR controlled three winding transformer, at first the amount of reactive power in the tertiary winding as a function of  $\alpha$  is determined, as shown in Figure 3.4. The firing signals for the thyristor valves are derived from a voltage controlled oscillator (VCO). It generates a 0 to 360 degree ramp function waveform, repeating at a frequency of

-

<sup>†</sup> Calculated corresponding to the high voltage winding

50 Hz. This waveform is used as a reference for determining the firing delay angle,  $\alpha$ . At  $\alpha = 180^{\circ}$ , the tertiary winding behaves like an open circuit.

Figure 3.4: Behaviour of reactive power (in VAr) in the tertiary winding with respect to firing angle,  $\alpha$

As  $\alpha$  is reduced gradually, more and more inductive reactive power is absorbed by the tertiary winding. When  $\alpha = 90^{\circ}$ , i.e. the thyristor valves are completely closed, the reactive power absorbed by the tertiary winding is 1968 VAr. The core supplies 1590 VArs (lagging) at 90 V. This indicates that theoretically the system in total is capable of absorbing 3558 VAr without drawing any VArs from the supply side.

#### 3.7 Automatic control

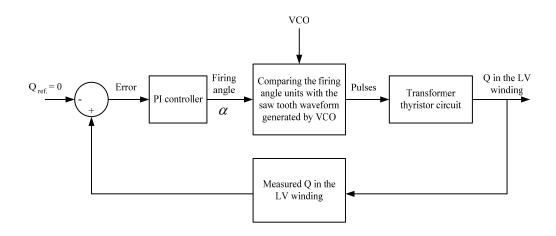

The actual application requires the TCR to be controlled in a closed loop fashion. As shown in Figure 3.5, the reactive power is measured in the LV winding and is compared with the reference. The error signal is then processed by a PI controller that generates the appropriate firing angle levels. Before firing signals are sent to the interpolated signal generators, the output of the PI controller is converted to angle units and properly conditioned to keep the angle within the limits, i.e.  $90^{\circ} \le \alpha \le 180^{\circ}$ . These angle units are then compared against the saw tooth waveforms generated by the VCO and firing signals to be fed to the thyristor valves are generated.

Figure 3.5: Automatic control strategy implemented in PSCAD/EMTDC

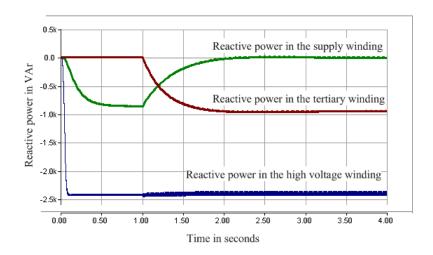

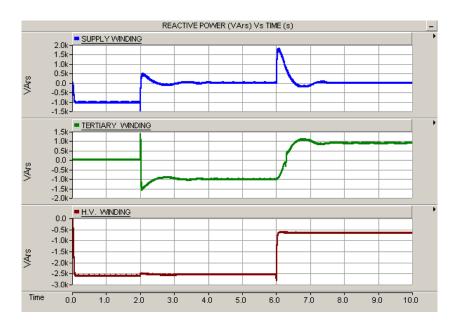

#### 3.7.1 Behaviour of reactive power in all the three windings

A capacitive load of 2470 VAr is connected to the terminals of the high voltage winding. The transformer is supplied with a rated voltage i.e. 90 V. In order to demonstrate the effectiveness and accuracy offered by the proposed system, initially, the circuit breaker in the tertiary winding is kept open and the total reactive power required by a capacitive load on the high voltage side is supplied by the core and the supply. At 1 sec, the circuit breaker is closed and the TCR starts operating. The initial value of the firing angle is 180°.

The TCR firing angle starts reducing and increasing its conductivity. Initially, 952 VArs are drawn from the supply while remaining VArs are supplied by the core. As more and more reactive power is absorbed by the tertiary winding, the requirement of reactive power from the supply gets dropped. At a steady state condition at which  $\alpha = 113.6^{\circ}$ , negligible reactive power is drawn from the supply. Figure 3.6 demonstrates the behaviour of reactive power in the three windings.

Figure 3.6: Behaviour of reactive power in all the three windings

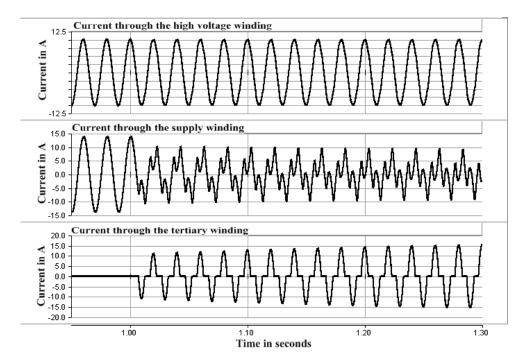

#### 3.7.2 Behaviour of currents in the three windings

After application of the TCR, the current in the supply winding dropped from 9.8 A to 4.3 A, of which the fundamental component accounts for 2.54 A. Total reactive current is provided by the tertiary winding. As shown in Figure 3.7, in addition to fundamental components, the TCR generates harmonics. The total harmonic distortion is dominant in the middle range of firing angle. As positive and negative current cycles are identical, only odd ordered harmonics are generated. As shown in equation 3.7, the amplitudes of these harmonics are a function of firing angle,  $\alpha$ .

$$I_{TCR}(\alpha) = \frac{4}{\pi} \frac{V}{\omega L} \left\{ \frac{\sin\alpha \cos(n\alpha) - n\cos\alpha \sin(n\alpha)}{n(n^2 - 1)} \right\}$$

(3.7)

where, n = 2k + 1, k = 1, 2, 3, ...

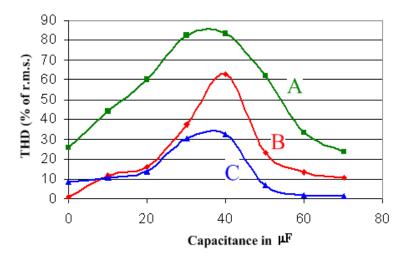

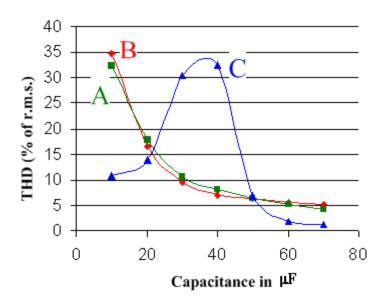

As the supply winding is magnetically coupled with the TCR controlled tertiary winding, the supply current also gets injected with harmonics. Total harmonic distortion (THD) in the currents in the supply, tertiary and high voltage windings is 138 %, 32% and 4% respectively. The current in the high voltage winding remains considerably unaffected by harmonics due to its higher inherent self inductance. Unlike three phase systems where harmonics can be reduced by

circuit arrangements, harmonics in the single phase system must be reduced by employing filters [18].

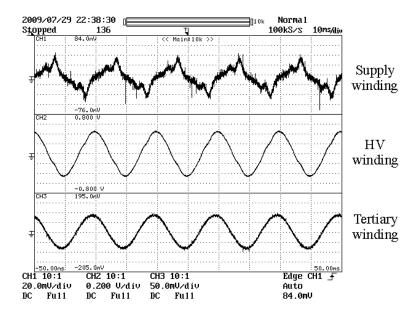

Figure 3.7: Current waveforms in all the three windings

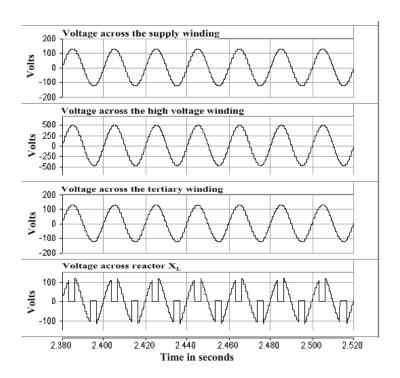

#### 3.7.3 Behaviour of voltage in all three windings

Figure 3.8, shows the voltage waveforms across the terminals of all windings and series reactor  $X_L$  at  $\alpha = 113.6^{\circ}$ . Considering the voltage supply is an ideal one, the higher value of series reactor in the tertiary winding prevents pollution of voltage waveforms in the remaining two windings.

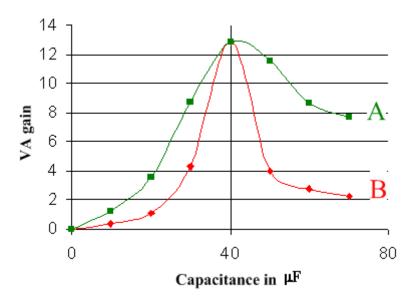

#### 3.7.4 VA gain

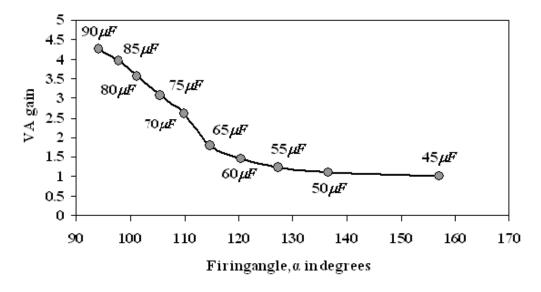

After application of the TCR, VA gain from the supply to load is 2.27. As the load increases, TCR branch absorbs more and more reactive power and hence VA gain increases. VA gains for other capacitive loads with respect to the firing angle,  $\alpha$ , are demonstrated in Figure 3.9.

Figure 3.8: Voltage waveforms in all the three windings

Figure 3.9: VA gain from the supply to load with respect to firing angle, α

# 3.7.5 Real power

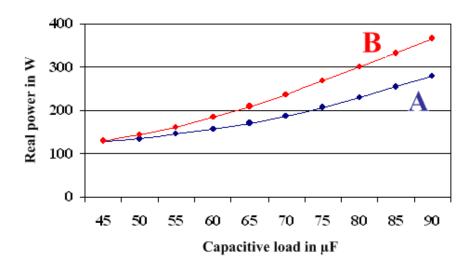

There is an increase in amount of real power losses from 170 W to 215 W due to the resistance in the tertiary winding and the TCR branch. Harmonics generated by the TCR branch also cause significant real power losses. For other capacitive

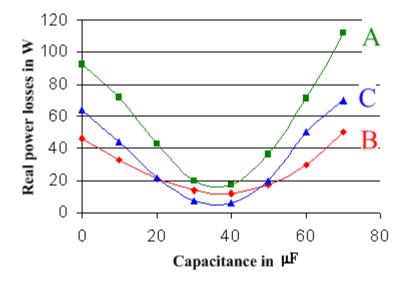

loads, as show in Figure 3.10, after application of the TCR, the system draws more real power from the supply side.

Figure 3.10: Real power losses at various capacitive loads, before (curve A) and after (curve B) application of the TCR

Simulation results for other sizes of capacitive loads are given in table 3.2.

# 3.8 Limitations of TCR application

- 1. This method is only applicable for the capacitive loads which generate VArs more than the minimum that the partial core transformer can absorb, in this case,  $1591 \le X_C \le 3330 \mu F$ , otherwise the system would either under or overcompensate.

- 2. In order to operate such a system in a more inductive environment, i.e.  $X_C \le 1591$ , another branch with either a fixed or variable capacitance value is needed, which would add cost and complexity to the system.

- 3. The major problem with this kind of system is that the TCR injects lower order harmonics. They are especially dominant when the value of the firing angle, α, approaches 125°. In a single phase system, it is difficult to eliminate these harmonics without a proper filter. A filter would add additional cost and complexity to the system. Filters for eliminating lower

order harmonics become bulky and expensive. Increasing the value of series reactance can reduce the total harmonic distortion but it also derates the system.

One of the solutions to overcome the above limitations, fully or partially, is to consider a voltage source converter (VSC) based STATCOM. The theory, modelling and analysis of the VSC based STATCOM is discussed in Chapter 4.

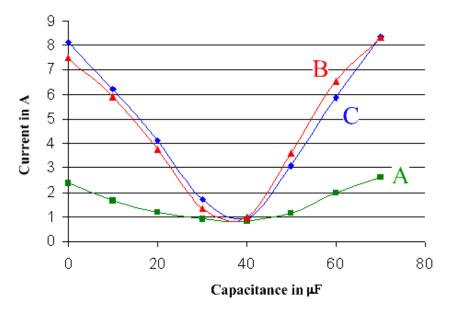

Table 3.2: Summary of the performance of the thyristor controlled three winding transformer as a static VAr compensator.

| Load VAr |           | $\alpha^3$ | VA    |       |      | Real power |       | Supply current in A |       |

|----------|-----------|------------|-------|-------|------|------------|-------|---------------------|-------|

| (μF)     | (leading) | (degrees)  | A     | В     | Gain | A          | В     | A                   | В     |

| 45       | 1647      | 157.0      | 153   | 150   | 1.02 | 130        | 130   | 1.71                | 1.67  |

| 50       | 1832      | 136.5      | 300   | 267   | 1.12 | 134.5      | 144   | 3.33                | 2.9   |

| 55       | 2019      | 127.3      | 476   | 330   | 1.23 | 144.5      | 162   | 5.29                | 3.68  |

| 60       | 2212      | 120.4      | 657.5 | 366.5 | 1.44 | 156.4      | 185   | 7.32                | 4.1   |

| 65       | 2397      | 114.7      | 844   | 385   | 1.79 | 171        | 210   | 9.37                | 4.34  |

| 70       | 2583      | 109.8      | 1029  | 392   | 2.62 | 187.5      | 236.5 | 11.44               | 4.37  |

| 75       | 2772      | 105.3      | 1216  | 394   | 3.08 | 207.0      | 268   | 13.51               | 4.4   |

| 80       | 2961      | 101.2      | 1403  | 395   | 3.56 | 229.0      | 300   | 15.6                | 4.4   |

| 85       | 3150      | 97.8       | 1591  | 400   | 3.97 | 254        | 332.6 | 17.68               | 4.404 |

| 90       | 3340      | 94.0       | 1780  | 416   | 4.27 | 280        | 367   | 19.77               | 4.64  |

$<sup>^3</sup>$  Firing angle,  $\alpha$  at which only the real power is drawn from the supply. A: without application of the TCR.

B: with application of the TCR.

# 3.9 Summary

Partial core transformers are used to perform high voltage testing of generator insulation (a capacitive load) at a.c. power frequencies. Manual position adjustment of the transformer's central core imposes challenges such as involvement of higher magnetic forces, proximity of the operator to high voltage and the possibility of under or over compensation.

In this chapter, a concept of a thyristor controlled three winding transformer is proposed. The theory, modelling and simulations have revealed the performance of the proposed scheme. Application of the TCR to a three winding transformer offers continuous variation of the reactive power. When the system is compensated, there is no reactive power demand from the main power supply. This makes it possible to use a supply of a lower VA rating. Performance of the TCR controlled three winding transformer is demonstrated for the range of load conditions in table 3.2

After application of the TCR, real power losses are increased. The TCR also injects harmonics in the currents in the three windings. This adds more real power losses and reduces the VA gain of the system. The higher self inductance of the high voltage winding reduces the current harmonic distortion in that winding.

# Chapter 4

# Modelling, analysis and design of a single phase voltage source converter (VSC) based STATCOM

#### 4.1 Overview

In chapter 3, the TCR controlled three winding partial core transformer is modelled, analysed and simulated using the PSCAD/EMTDC software. In order to compensate the system, continuous variation of reactive power is achieved by adjusting the shunt impedance of the TCR. Though the application of the TCR is simple, this technique has limitations as discussed in section 8. The amount of reactive power absorbed is directly dependent on the rating of the energy storage devices. For certain applications, the system may become bulky and complicated.

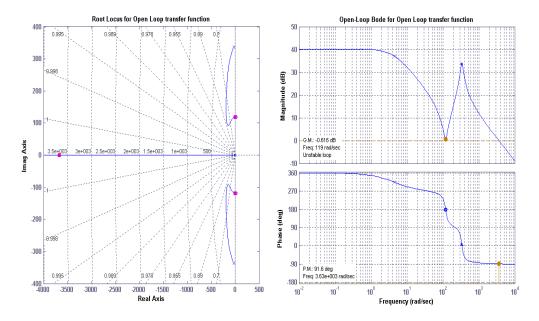

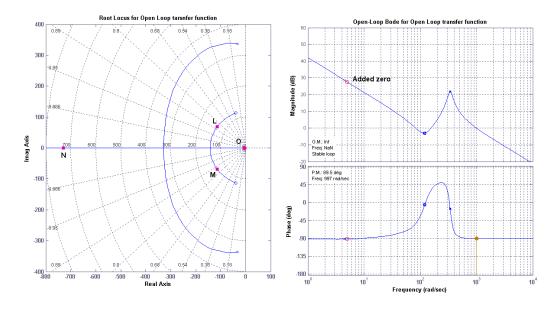

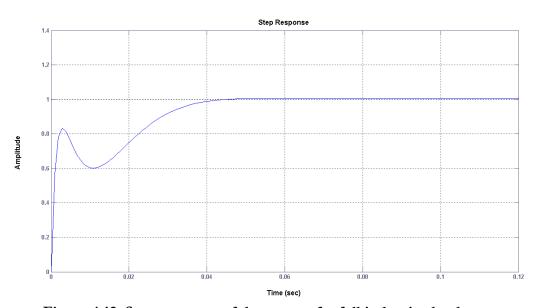

This chapter discusses a STATCOM controlled partial core transformer. A detailed mathematical design of the voltage source converter (VSC) based STATCOM along with its transfer function is demonstrated. A proportional – integral (PI) controller is designed using MATLAB. Stability of the designed control system is evaluated for *capacitive* and *inductive* loads. The proposed system is modelled in PSCAD/EMTDC software. The model verifies the capability of the system to offer a continuous reactive power control in the partial core transformer, and to limit the supply current magnitude to its real component.

#### 4.2 Introduction

In 1976 Gyugyi disclosed switching power converters that generate controllable reactive power directly, without the use of a.c. capacitors or reactors. For multiphase systems, the ability to generate or absorb reactive power without the presence of large reactive energy storage elements makes them very useful in power applications. In a three phase STATCOM this is accomplished by making

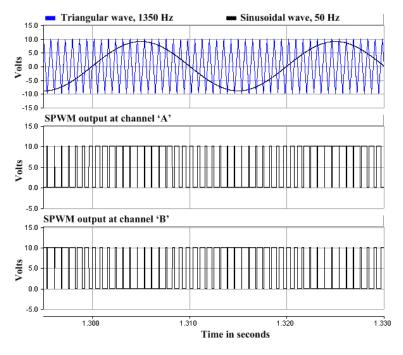

the currents circulate through the phases of the a.c. system with the aid of power switching devices [19]. From the point of view of reactive power generation, their operation mirrors an ideal synchronous machine that uses excitation for controlling the reactive power output. They are also capable of exchanging real power with the a.c. system, if they are provided with a d.c. energy source at the d.c. terminals of the converter. Because of these similarities, they are also called Static Synchronous Generators (SSGs). When a SSG is used as a shunt connected reactive compensator with no energy source, it is termed a Static Synchronous Compensator or STATCOM. Although current source converters are possible, voltage sourced converters are preferred. Justification for this is well documented in [18]. Unlike the TCR, the VSC based STATCOM generates an a.c. output waveform using a sinusoidal pulse width modulation (SPWM) technique; this significantly reduces lower order harmonics without the need of any additional filters.

# 4.3 Modelling and analysis of a single phase VSI based STATCOM

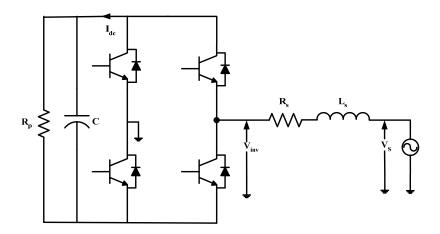

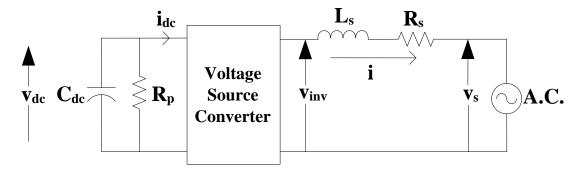

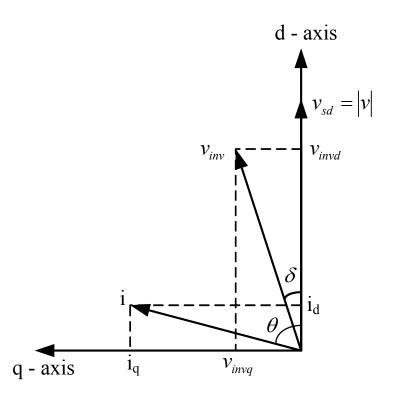

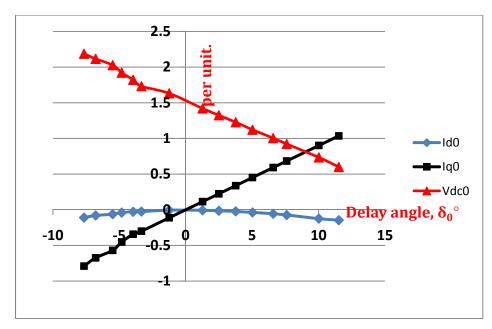

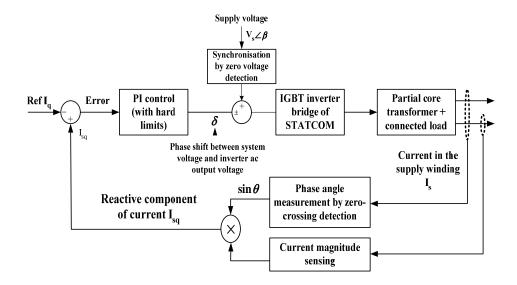

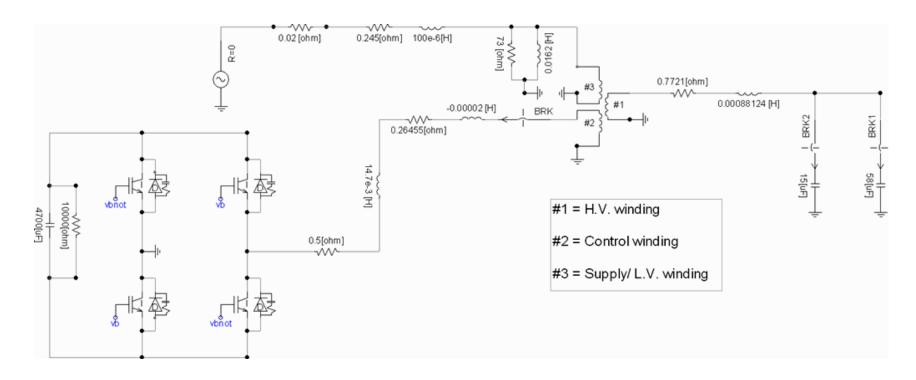

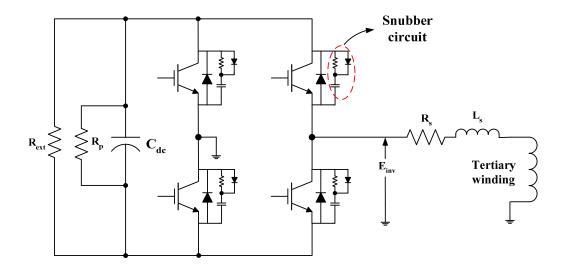

Figure 4.1 shows a simplified circuit diagram of a single phase VSI based STATCOM. In this circuit,  $V_s$  signifies the supply voltage, and the series inductance  $L_s$  represents the leakage inductance of the transformer.  $R_s$  accounts for the conduction losses of the converter.

Figure 4.1: A single phase voltage source converter based STATCOM

The charged capacitor, C acts as a d. c. voltage source for the converter. The converter consists of four IGBTs in a single phase 'H' bridge configuration

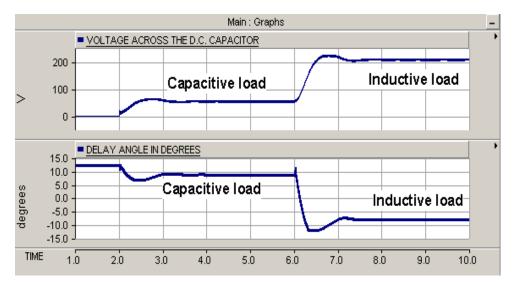

which produces a controllable single-phase SPWM output voltage,  $V_{inv}$ , with a frequency of that of the a.c. power system. The output voltage waveform of the converter is never a pure sine wave. It contains a fluctuating (ripple) component of instantaneous output power (VA). The voltage will fluctuate at low frequency as the converter is required to store the 'reactive energy'.  $R_p$  represents the switching losses in the converter.

The d.c. storage capacitor is required for maintaining the net instantaneous power at the d.c. input terminals (ignoring the switching losses of the semiconductor devices) equal to the net instantaneous power at the a.c. output terminals. Thus, the d.c. capacitor maintains a balance between the input and output during the dynamic change in the VAr output [18]. This can require a significant capacitance.

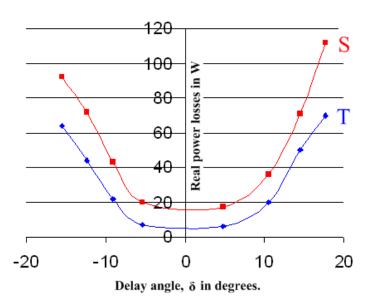

In a practical situation, semiconductor switches incur active power losses. These internal losses are supplied by the a.c. supply, and the voltage level drops down lower than expected. In order to prevent this, the switching losses are supplied by the a.c. system by making the converter a.c. output voltage lag behind the a.c. system voltage by a small angle,  $\delta$ . Equation 4.1 gives the relationship between the real power, P absorbed by the STATCOM and the phase angle  $\delta$ .  $X_L$  accounts for the reactance between  $V_s$  and  $V_{inv}$ .  $R_s$  is neglected.

$$P = \frac{V_{inv}V_s}{X_I}\sin\delta\tag{4.1}$$

The phase angle can be used to control the capacitor voltage and hence the converter output voltage,  $V_{inv}$ . As shown in equation 4.2, the magnitude and nature (inductive or capacitive) of reactive power, Q, exchanged between the STATCOM and the system, can be adjusted by controlling the voltage drop across the equivalent series impedance,  $X_L$ , between the a.c. side of the STATCOM and the system voltage.

$$Q = \frac{V_{inv} - V_s}{X_L} V_s \tag{4.2}$$

If Q is positive, the STATCOM delivers reactive power to the system. Otherwise the STATCOM absorbs reactive power from the system [20]. The voltage,  $V_{inv}$ , can be controlled either by adjusting the modulation index, m, of the PWM waveform, or by changing the phase angle,  $\delta$ , between  $V_{inv}$  and  $V_s$  which charges or discharges the capacitor d.c. voltage. Both systems are explained in detail in [18]. Work carried out for this research employs the latter scheme.

## 4.4 Concept of STATCOM controlled partial core transformer

In the case of a partial core transformer, the lack of a closed core reduces the magnetising reactance ( $X_m$ ) significantly and increases the reactive power requirement. Thus it draws a higher magnitude of lagging current from the supply as compared to its full core counterpart. If this demand is supplied by a compensator which can eliminate the reactive power demand on the main supply, the partial core transformer can be used like a full core transformer [4]. Its applications can be found where weight, size and ease of transportation are the major priorities, e.g. relocatable compensating systems [21].

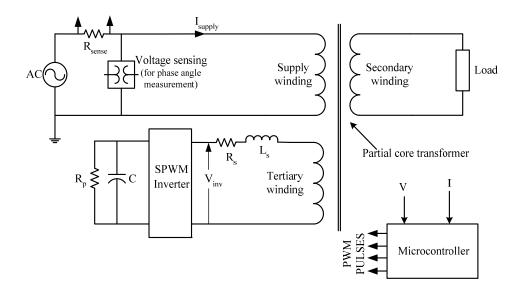

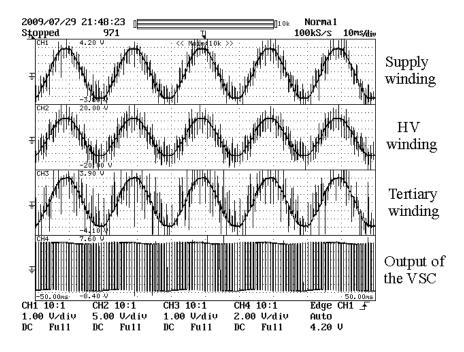

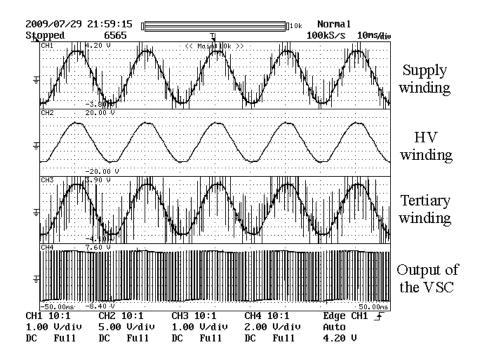

As shown in figure 4.2, a single phase, VSI-based STATCOM is connected to the tertiary winding of a partial core three winding transformer. In order to minimise the total harmonic distortion and ripple content in the supply current, the a.c. terminals of the converter are connected to the mains supply through an external inductor,  $L_{\rm s}$ .

The magnitude of the supply current is sensed by measuring a voltage drop across a low value resistance,  $R_{sense}$ . The phase angle,  $\theta$ , the angle between the supply voltage and current, is measured by detecting the time difference between the zero crossings of the supply voltage and current waveforms.

Figure 4.2: Proposed STATCOM controlled scheme for a partial core transformer

An 8 bit micro-controller is used to generate SPWM waveforms as well as to accomplish automatic control of the STATCOM. The actual hardware developed is described in chapter 5.

# 4.5. Design of the STATCOM

The STATCOM design is considered for compensating the reactive power required by the lower  $X_m$  of the partial core transformer. As a prototype, the proposed STATCOM is designed for  $\pm 1 \text{ kVAr}$ .

#### 4.5.1 Current rating of the STATCOM

The current rating of the STATCOM is related to the total reactive power delivered to the load and partial core transformer for compensating  $X_m$ .

$$Q_{total} = V_s \times I_s \tag{4.3}$$

where  $V_s$  is the a.c. mains voltage (i.e. 90 V r.m.s.) and  $I_s$  is the STATCOM line current. After substituting the values of  $V_s$  and  $Q_{total}$  (i.e. 1 kVAr), the current rating of the STATCOM is 11.11 A. [22].

#### 4.5.2 Determination of series inductance (L<sub>s</sub>)

The equation for determining the series inductance, L<sub>s</sub> for a single phase STATCOM is derived from [23],

$$L_{s} = \frac{V_{dc} \times m}{4 \times f_{s} \times I_{rinnle(n-n)}} \tag{4.4}$$

where  $V_{dc}$  is the DC voltage across the electrolytic capacitor. The modulation index, m is considered as 1. The switching frequency,  $f_s$ , of the PWM synthesised, is chosen as 1350 Hz.  $I_{ripple(p-p)}$  is the peak-peak ripple current, which is designed to be 8% of the total current. Thus the peak-peak ripple current is given by,

$$I_{ripple(peak-peak)} = 2\sqrt{2} \times 0.08 \times 11.11 = 2.5 \text{ A}$$

(4.5)

For calculating  $L_s$ , the maximum magnitude of  $V_{dc}\left(>\sqrt{2}\ V_{inv}^{max}\right)$  is taken into account. From equation 4.2, it can be seen that the magnitude of the STATCOM output voltage controls the reactive power exchange between the STATCOM and the system, assuming that the system voltage and the series impedance are kept constant. Re-writing equation 4.2 for the maximum rated reactive power,  $Q_{max}$ , the STATCOM can deliver

$$Q_{\text{max}} = \left(\frac{\frac{V_{dc}}{\sqrt{2}} - V_s^{\text{max}}}{\omega L_s}\right) \times V_s^{\text{max}}$$

(4.6)

In this case,  $Q_{max}$  is 1000 VAr and maximum system voltage,  $V_s^{max}$ , is 90 V. Substituting these values into equation 4.6 yeilds

$$1000 = \left(\frac{\frac{V_{dc}}{\sqrt{2}} - 90}{\omega L_s}\right) \times 90 \tag{4.7}$$

Substituting the value of  $I_{ripple(peak-peak)}$  in equation 4.4 and simultaneously solving the equations 4.4 and 4.7, magnitudes of  $V_{dc} = 200 \text{ V}$  and  $L_s = 14.8 \text{ mH}$  are obtained. The approximate voltage drop across the pair of power switches is

assumed to be 6 V and is added to  $V_{dc}$ . Hence  $V_{dc}$  becomes 206 V. The resistance in series,  $R_s$ , representing the active losses, is assumed to be 0.5  $\Omega$ .

#### 4.5.3 Choosing the value of d.c. capacitor (C)

The equations for proper sizing of the d.c. capacitor for one converter system are detailed in [20]. The d.c. capacitor peak to peak voltage ripple is given by,

$$\Delta V_c = \frac{m I}{2\omega C} \tag{4.8}$$

The selected value of d.c. voltage ripple is 4 V, which is 2% of the selected  $V_{dc}$  (= 206 V). From equation 4.8, the value of C can be derived as

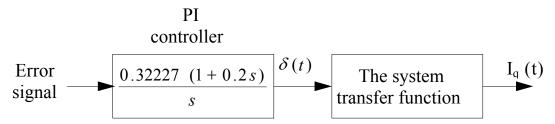

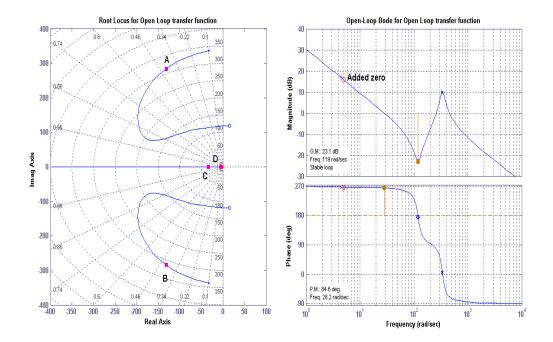

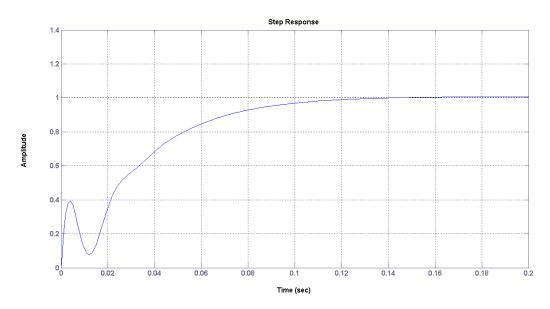

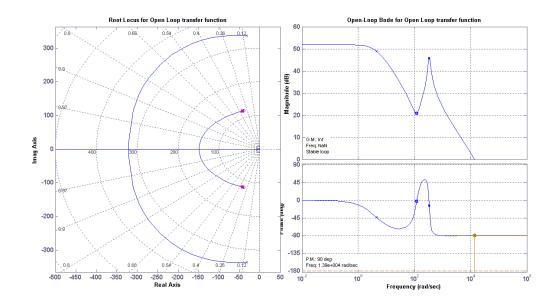

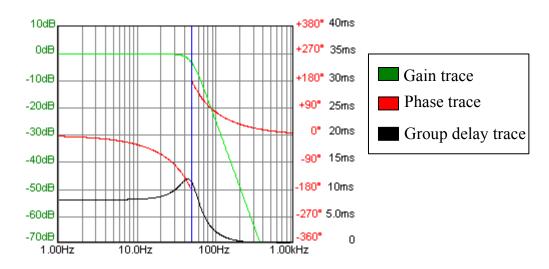

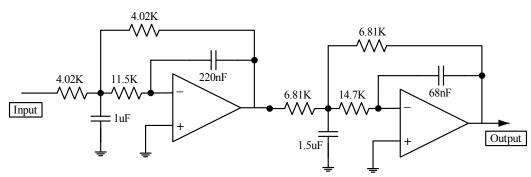

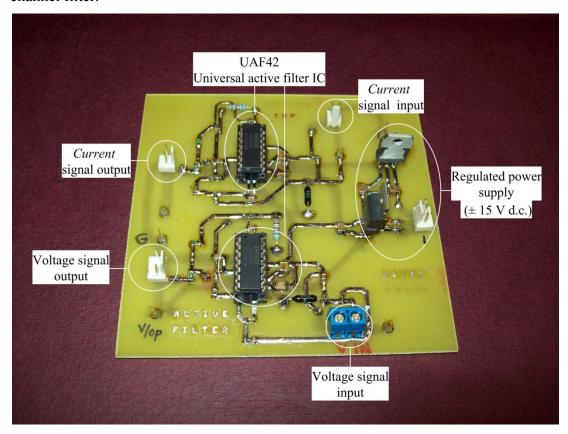

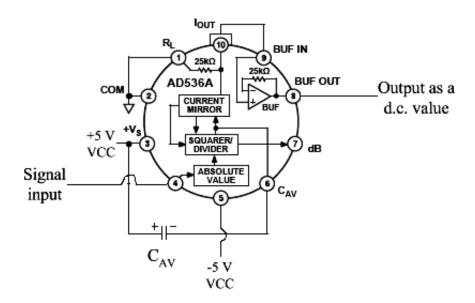

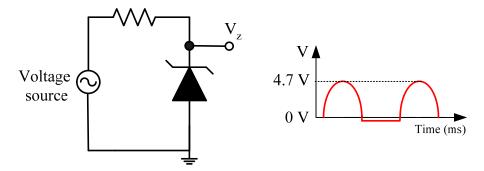

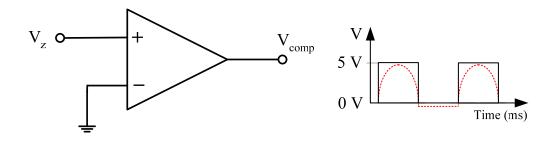

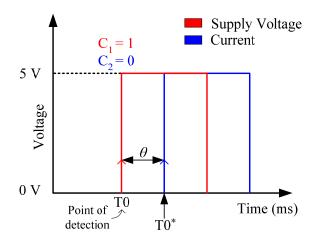

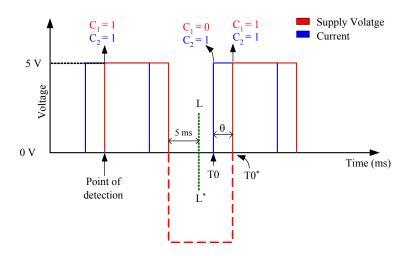

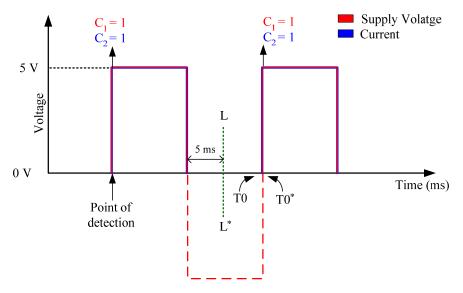

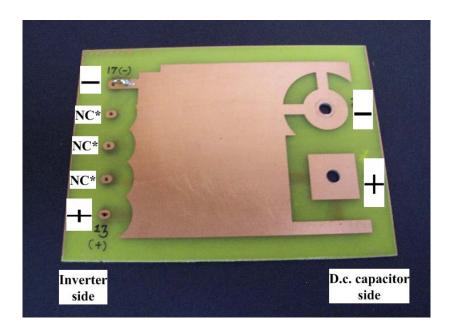

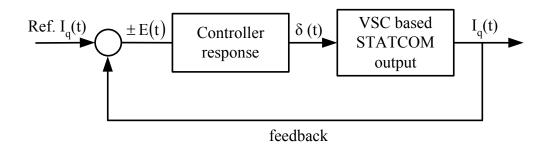

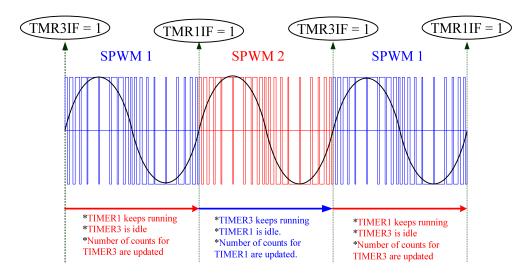

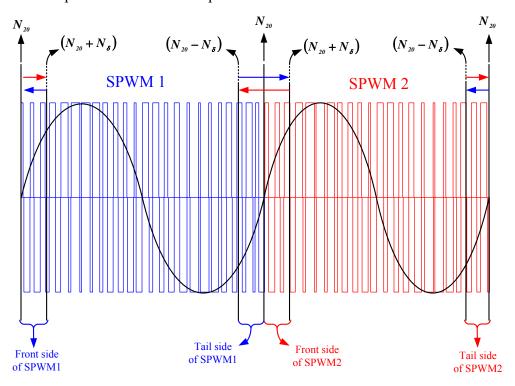

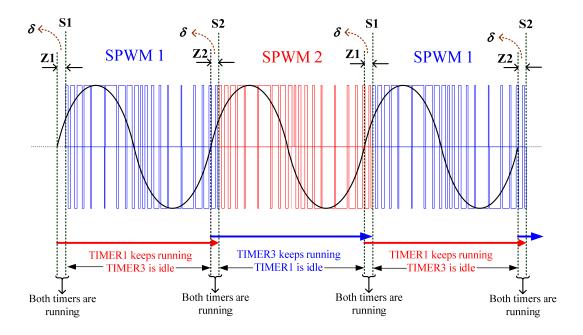

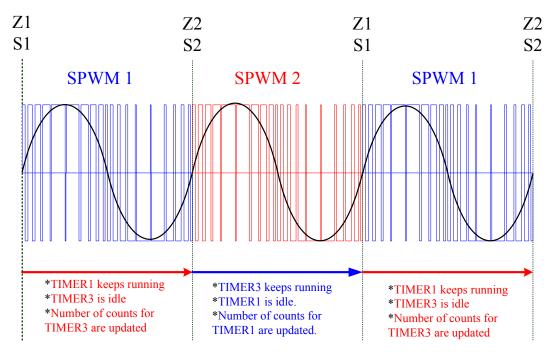

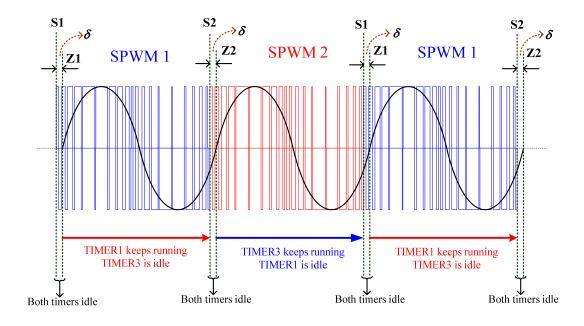

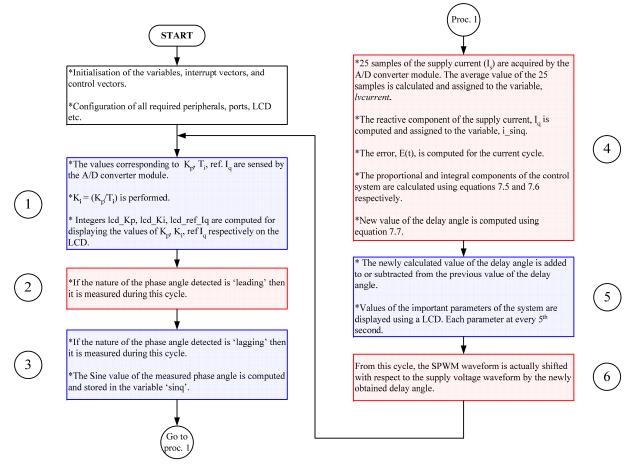

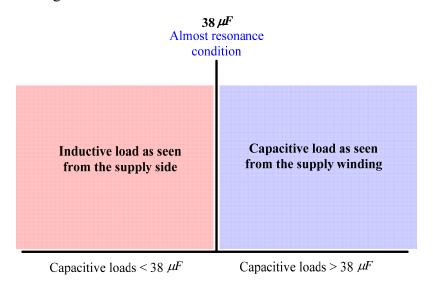

$$C = \frac{m I}{2\omega \Delta V_c} \tag{4.9}$$