# Model Checking Time Triggered CAN Protocols

Daniel Keating

A thesis submitted in partial fulfilment of the requirements for the degree of Master of Engineering in Electrical and Computer Engineering at the University of Canterbury, Christchurch, New Zealand.

25 January 2011

#### **ABSTRACT**

Model checking is used to aid in the design and verification of complex concurrent systems. An abstracted finite state model of a system and a set of mathematically based correctness properties based on the design specifications are defined. The model checker then performs an exhaustive state space search of the model, checking that the correctness properties hold at each step. This thesis describes how the SPIN model checker has been used to find and correct problems in the software design of a distributed marine vessel control system currently under development at a control systems specialist in New Zealand. The system under development is a mission critical control system used on large marine vessels. Hence, the requirement to study its architecture and verify the implementation of the system. The model checking work reported here focused on analysing the implementation of the Time-Triggered Controller-Area-Network (TTCAN) protocol, as this is used as the backbone for communications between devices and thus is a crucial part of their control system.

A model of the ISO TTCAN protocol has been created using the SPIN model checker. This was based on work previously done by Leen and Heffernan modelling the protocol with the UPPAAL model checker [Leen and Heffernan 2002a]. In the process of building the ISO TTCAN model, a set of general techniques were developed for model checking TTCAN-like protocols. The techniques developed include modelling the progression of time efficiently in SPIN, TTCAN message transmission, TTCAN error handling, and CAN bus arbitration. These techniques then form the basis of a set of models developed to check the sponsoring organisation's implementation of TTCAN as well as the fault tolerance schemes added to the system. Descriptions of the models and properties developed to check the correctness of the TTCAN implementation are given, and verification results are presented and discussed. This application of model checking to an industrial design problem has been successful in identifying a number of potential issues early in the design phase. In cases where problems are identified, the sequences of events leading to the problems are described, and potential solutions are suggested and modelled to check their effect of the system.

### CONTENTS

| CHAPTER 1 | INTRODUCTION |                               |                                                      |    |  |  |

|-----------|--------------|-------------------------------|------------------------------------------------------|----|--|--|

|           | 1.1          | Overv                         | iew of TTCAN                                         | 1  |  |  |

|           | 1.2          | Overv                         | iew of model checking                                | 2  |  |  |

|           | 1.3          | Main                          | phases of the project                                | 2  |  |  |

|           | 1.4          | Thesis                        | structure                                            | 3  |  |  |

| CHAPTER 2 | NE           | NETWORK PROTOCOLS BACKGROUND  |                                                      |    |  |  |

|           | 2.1          | CAN                           | protocol                                             | 5  |  |  |

|           |              | 2.1.1                         | CAN protocol background                              | 5  |  |  |

|           | 2.2          | TTCA                          | aN protocol                                          | 7  |  |  |

|           |              | 2.2.1                         | TTCAN protocol background                            | 7  |  |  |

|           |              | 2.2.2                         | TTCAN message schedule                               | 8  |  |  |

|           |              | 2.2.3                         | Timing in TTCAN                                      | Ć  |  |  |

|           |              | 2.2.4                         | Error-handling in TTCAN                              | Ć  |  |  |

|           |              | 2.2.5                         | Startup and reintegration of potential time-masters  | S  |  |  |

|           | 2.3          | l-triggered network protocols | 11                                                   |    |  |  |

|           | 2.4          | The sp                        | consoring organisation's implementation of TTCAN     | 12 |  |  |

|           |              | 2.4.1                         | System architecture                                  | 12 |  |  |

|           |              | 2.4.2                         | Implementation of TTCAN message schedules            | 14 |  |  |

|           |              | 2.4.3                         | Modifications to TTCAN synchronisation reference     |    |  |  |

|           |              |                               | message                                              | 14 |  |  |

| CHAPTER 3 | MO           | DEL (                         | CHECKING BACKGROUND                                  | 17 |  |  |

|           | 3.1          | Introd                        | uction to formal methods and model checking          | 17 |  |  |

|           |              | 3.1.1                         | Specification and verification of systems using for- |    |  |  |

|           |              |                               | mal methods                                          | 18 |  |  |

|           |              | 3.1.2                         | Model checking overview                              | 18 |  |  |

|           |              | 3.1.3                         | Overview of model checking tools                     | 18 |  |  |

|           | 3.2          | Overv                         | iew of the SPIN model checker                        | 19 |  |  |

|           |              | 3.2.1                         | Overview of the structure of the SPIN model checker  | 20 |  |  |

|           | 3.3          | Specif                        | ication of model and correctness properties          | 21 |  |  |

|           |              | 3.3.1                         | Overview of the PROMELA specification language       | 21 |  |  |

|           |              | 3.3.2                         | Specification of correctness properties with LTL     | 21 |  |  |

vi

|           |     | 3.3.3                 | _          | ation of a model and correctness properties |    |

|-----------|-----|-----------------------|------------|---------------------------------------------|----|

|           |     |                       |            | ffee shop                                   | 22 |

|           | 3.4 | Overv                 | iew of te  | chniques for modelling the progression of   |    |

|           |     | time i                | n a syster | n                                           | 26 |

|           | 3.5 | ion in model checking | 28         |                                             |    |

| CHAPTER 4 | MC  | DEL (                 | CHECK      | ING ISO TTCAN                               | 29 |

|           | 4.1 | Model                 | ling the p | progression of time                         | 29 |

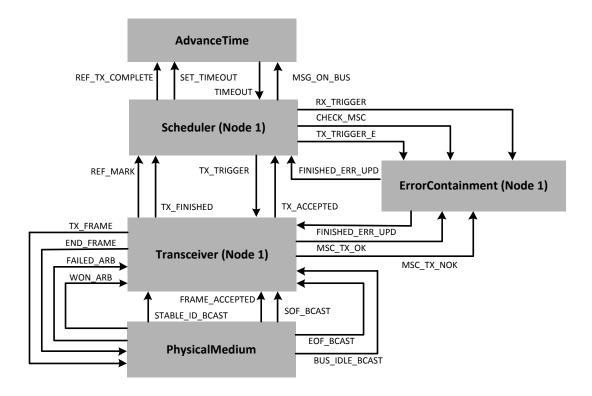

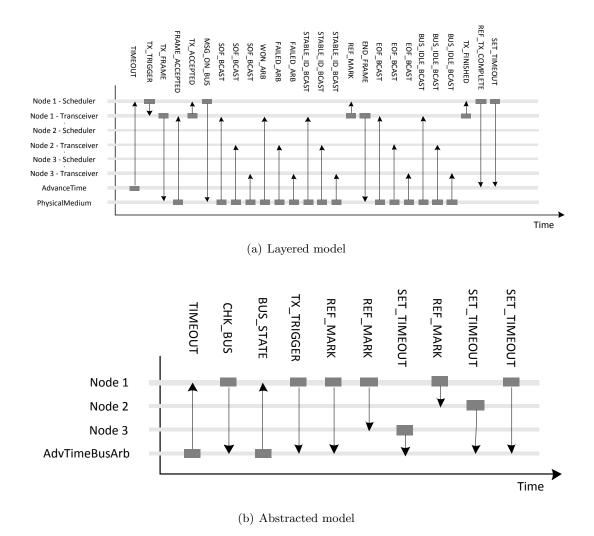

|           | 4.2 | Overv                 | iew of lay | rered model                                 | 31 |

|           |     | 4.2.1                 | Structur   | re of model                                 | 31 |

|           |     | 4.2.2                 | Handlin    | g CAN message transmissions                 | 33 |

|           |     | 4.2.3                 | Handlin    | g of timing                                 | 36 |

|           |     |                       | 4.2.3.1    | Implementation details for modelling tim-   |    |

|           |     |                       |            | ing                                         | 36 |

|           |     | 4.2.4                 | Schedule   | er node model                               | 40 |

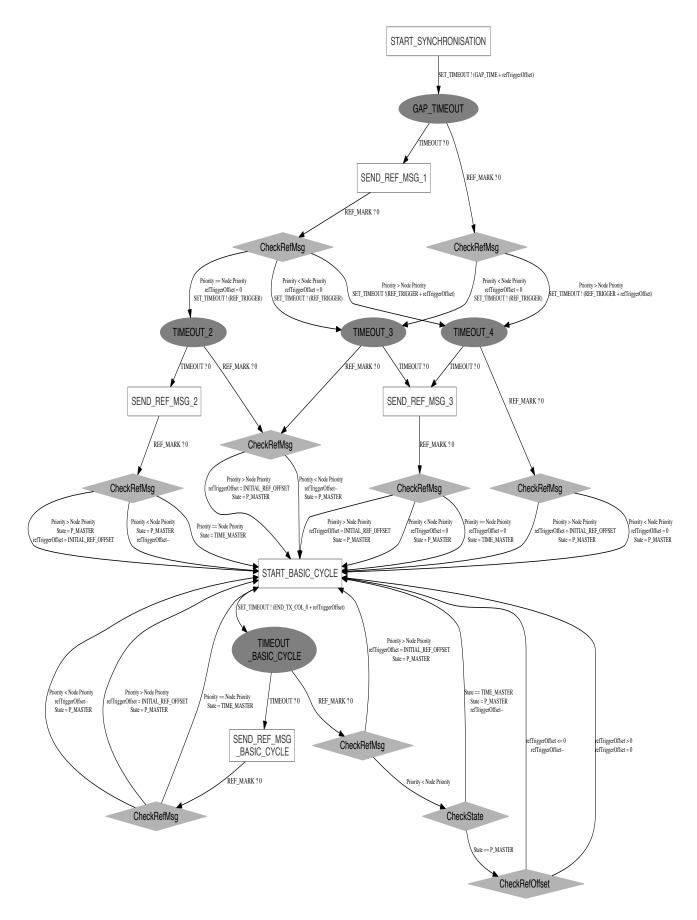

|           |     |                       | 4.2.4.1    | Startup synchronisation                     | 40 |

|           |     |                       | 4.2.4.2    | Basic-cycle model                           | 43 |

|           |     | 4.2.5                 | ISO TT     | CAN error-handler model                     | 43 |

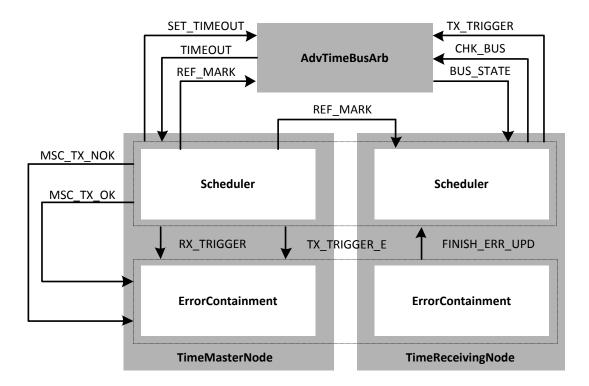

|           | 4.3 | Overv                 | iew of ab  | stracted model                              | 45 |

|           |     | 4.3.1                 | Structur   | re of model                                 | 45 |

|           |     | 4.3.2                 | Handlin    | g of timing                                 | 47 |

|           |     |                       | 4.3.2.1    | Overview of implementation                  | 49 |

|           |     |                       | 4.3.2.2    | Handling CAN bus arbitration                | 50 |

|           |     |                       | 4.3.2.3    | Handling TTCAN reference message            | 52 |

|           |     |                       | 4.3.2.4    | Example of modified timing scheme           | 54 |

|           |     | 4.3.3                 | Modifica   | ations to scheduler processes               | 55 |

|           | 4.4 | Verific               | ation of 1 | models                                      | 57 |

|           |     | 4.4.1                 | Verified   | properties                                  | 57 |

|           |     | 4.4.2                 | Verificat  | tion results                                | 60 |

|           |     |                       | 4.4.2.1    | Initial layered model                       | 60 |

|           |     |                       | 4.4.2.2    | Abstracted model                            | 61 |

|           |     | 4.4.3                 | Discussi   | on of results                               | 61 |

|           | 4.5 | Summ                  | ary of mo  | odelling ISO TTCAN                          | 62 |

| CHAPTER 5 | MC  | DEL (                 | CHECK      | ING THE TTCAN                               |    |

|           | IM  | PLEM                  | ENTAT      | ION                                         | 63 |

|           | 5.1 | TTCA                  | N protoc   | eol model                                   | 64 |

|           |     | 5.1.1                 | Overvie    | W                                           | 64 |

|           |     |                       | 5.1.1.1    | Structure of model                          | 65 |

|           |     |                       | 5.1.1.2    | Scheduling of events at a node              | 66 |

|           |     |                       | 5.1.1.3    | Modelling TTCAN message transmission        | 69 |

|           |     | 5.1.2                 | Correcti   | ness properties and failure scenarios used  |    |

|           |     |                       | in verific |                                             | 73 |

|           |     |                       | 5.1.2.1    | Assumptions made for verification of model  | 74 |

|           |     |                       |            | Failure scenarios                           | 74 |

CONTENTS

|            |              |        | 5.1.2.3   | Correctness properties                        | 77  |

|------------|--------------|--------|-----------|-----------------------------------------------|-----|

|            |              | 5.1.3  | Verificat | ion results                                   | 78  |

|            |              |        | 5.1.3.1   | Verification results for "base" configuration | 78  |

|            |              |        | 5.1.3.2   | Verification results for most common and      |     |

|            |              |        |           | worst case configurations                     | 80  |

|            |              |        | 5.1.3.3   | Verification of model with incorrectly con-   |     |

|            |              |        |           | figured module                                | 81  |

|            |              | 5.1.4  |           | l solutions                                   | 82  |

|            | 5.2          | Voter  |           |                                               | 83  |

|            |              | 5.2.1  | Structur  | e of model                                    | 84  |

|            |              | 5.2.2  | Correctn  | less properties                               | 86  |

|            |              | 5.2.3  | Verificat | ion results                                   | 87  |

|            |              | 5.2.4  | Potentia  | l solutions                                   | 89  |

|            | 5.3          | Signal | picker me | odel                                          | 89  |

|            |              | 5.3.1  | Structur  | e of model                                    | 89  |

|            |              | 5.3.2  | Correctn  | less properties                               | 93  |

|            |              | 5.3.3  | Verificat | ion results                                   | 94  |

|            | 5.4          | Redun  | dant TTO  | CAN protocol model                            | 94  |

|            |              | 5.4.1  | Structur  | e of model                                    | 94  |

|            |              | 5.4.2  | Failure s | cenarios                                      | 97  |

|            |              | 5.4.3  | Correctn  | less properties                               | 98  |

|            |              | 5.4.4  | Verificat | ion results                                   | 99  |

|            |              | 5.4.5  | Potentia  | l solutions                                   | 101 |

|            | 5.5          | Summ   | ary of po | tential problems found                        | 101 |

| CHAPTER 6  | CO           | NCLU   | SION      | I                                             | 103 |

| APPENDIX A | LIS          | TINGS  | S COMN    | MON TO ALL MODELS                             | 107 |

| APPENDIX B | LIS'         | TING   | FOR LA    | AYERED MODEL OF ISO TTCAN                     | 121 |

| APPENDIX C | LIS          | TING   | FOR AI    | BSTRACTED MODEL OF ISO                        |     |

|            | TTO          | CAN    |           | 1                                             | 139 |

| APPENDIX D | LIS'         | TINGS  | FOR T     | THE MODEL OF THE TTCAN                        |     |

|            | IMI          | PLEMI  | ENTATI    | ON                                            | 153 |

| APPENDIX E | VEI          | RIFIC  | ATION '   | TOOL SPECIFICATIONS                           | 187 |

| REFERENCE  | $\mathbf{S}$ |        |           | ]                                             | 189 |

|            |              |        |           |                                               |     |

#### ACKNOWLEDGEMENTS

I would like to thank my supervisors Dr Allan McInnes and Dr Michael Hayes for their help and guidance throughout the course of this project. Allan has given me great advice and encouragement and during the project, and I would like to thank him for setting-up what has been such an interesting and rewarding project. I would also like to thank him for the many hours he has spent proofreading and providing feedback on my thesis chapter drafts and papers. Michael has also given me a lot of encouragement and some excellent advice during the course of the project, and I would also like to thank him for the time he has spent proofreading my reports and thesis drafts and especially for the excellent advice to improve my writing.

I would also like to thank my parents and family for all their support and encouragement.

### Chapter 1

#### INTRODUCTION

A New Zealand based control systems specialist is currently developing a mission critical control system to be used on large marine vessels. The control system uses the Time-Triggered Controller-Area-Network (TTCAN) protocol for communication between modules on the system. In distributed systems such as this, where there is communication between concurrently executing processes, the complicated nature of the system often leads to design errors difficult to detect using conventional testing methods. The aim of the research described in this thesis was to apply model checking techniques to assist in verifying the correct operation of the implementation of the TTCAN protocol in the control system.

#### 1.1 OVERVIEW OF TTCAN

Currently, the Controller-Area-Network (CAN) protocol is one of the most widely used protocols for modern vehicle communications networks [Leen and Heffernan 2002b]. Although the bit-timing of CAN nodes is synchronised, in terms of the timing of message transmissions, CAN is an asynchronous protocol; triggering of message transmissions from nodes is not synchronised to a global clock. Messages are transmitted across a bus in response to the occurrence of corresponding events at a node. Consequently, conflicts occur on the CAN bus when multiple messages are sent simultaneously. In this case, a priority-based arbitration scheme determines the message transmitted on the bus. This arbitration scheme introduces non-deterministic delay or jitter into the system, complicating the design of systems with tight timing constraints such as vehicle drive-by-wire systems [Fuhrer et al 2000].

TTCAN (ISO 11898-4) [ISO 11898-4 2004] adds a session layer to the existing data-link and physical layers of the CAN protocol to offer more deterministic timing [Leen and Heffernan 2002b]. It is a synchronous (time-triggered) protocol, where the transmission of messages is based on the progression of a globally synchronised time-base. Each node has a pre-defined schedule of messages to transmit in pre-allocated time-slots. This way conflicts on the bus are eliminated and message latencies are

guaranteed. This predictability makes system design simpler and the design of more complicated systems possible.

#### 1.2 OVERVIEW OF MODEL CHECKING

Concurrent systems are found in a number of applications. This may be a distributed network of sensors and actuators in a control system or multiple threads executing in an individual program. Due to the complexity of these types of systems, subtle errors in the system design may not always be detected by conventional simulation and testing techniques [Merz 2000]. In such situations model checking can be used as a system design aid to verify correctness of concurrently executing asynchronous processes.

The initial step in the model checking process is to develop a model that specifies a finite state representation of a concurrent system, and captures the interactions between different threads or processes in the system. Following this, a set of correctness properties are created to verify against the model [Merz 2000]. Running the model checker exhaustively searches the state-space of the model for possible deadlocks or violations of the specified correctness properties. If an error is detected during model checking then a counter-example trace is produced. This shows the sequence of events leading to the undesired condition, and this can be used to aid in debugging the implementation [Holzmann 2004].

Leen and Heffernan applied model checking techniques when developing the ISO TTCAN specification, using the UPPAAL model checker. The goal of their work was to check the error handling scheme worked as intended and to ensure the protocol was free of deadlocks [Leen and Heffernan 2002a]. Saha and Roy used the SAL model checker to ensure that the TTCAN startup scheme behaves as expected. Checks were made to ensure nodes synchronise to the network correctly, a time-master is elected correctly, and possible errors are handled correctly, during the initialisation period [Saha et al 2007]. They also used a variant of the SPIN model checker capable of modelling fixed discrete time intervals called Discrete Time SPIN (DT-SPIN) to ensure that the TTCAN protocol behaves as expected [Saha and Roy 2007].

#### 1.3 MAIN PHASES OF THE PROJECT

The initial objectives of the project were to create a model of the ISO TTCAN protocol, and to develop a specification of correctness properties to verify against the model. Developing the initial model of the ISO TTCAN protocol involved recreating previous work done by Leen and Heffernan model checking TTCAN using the UPPAAL model checker [Leen and Heffernan 2002a]. Following this, the ISO TTCAN model was modified to reflect the sponsoring organisation's implementation of the protocol and model checking techniques applied to verify that this implementation of TTCAN was correct.

This involved analysing the source code and documentation of the sponsoring organisation's TTCAN driver implementation to develop an abstracted finite state model of the system, and a set of correctness properties to check against the model. The model was then extended to check the interaction between the sponsoring organisation's fault-tolerance mechanisms and the ISO TTCAN protocol. Next, the injection of faults was modelled to check the implementation of the fault protection system. Finally, potential solutions to the problems found in the implementation were modelled to show how they perform when integrated into the system.

#### 1.4 THESIS STRUCTURE

Chapter 2 gives background for the CAN field-bus protocol and the TTCAN variant of the protocol, as this protocol is central to the BlueArrowAvx system and is the focus of the majority of this model checking work. Chapter 3 contains background on the process of model checking. Chapter 4 describes a layered model developed using SPIN to model check the ISO TTCAN protocol. This model is based on work previously done by Leen and Heffernan model checking ISO TTCAN using the UPPAAL model checker. A simplified abstracted model is also described, and comparisons of the resources required for verification are made between the models and with Leen and Heffernan's model. Chapter 5 describe the models and correctness specifications developed for the sponsoring organisation's implementation of the TTCAN protocol. The results of verification of the models are shown and potential problems detected during the verifications are illustrated. Potential solutions to problems identified are also modelled. Finally, Chapter 6 summarises the results of the model checking and gives ideas for future work.

### Chapter 2

#### NETWORK PROTOCOLS BACKGROUND

Sections 2.1 and 2.2 give an overview of the CAN protocol and the TTCAN protocol. These are the protocols used by the sponsoring organisation in their next generation distributed marine vessel control system. These protocols form the backbone of the distributed system, and were the main focus of the model checking work done on this system. Section 2.4 contains details of the sponsoring organisation's implementation of the TTCAN protocol. Some background on next generation time-triggered protocols including FlexRay and the TTP/C protocol is also included in Section 2.3.

#### 2.1 CAN PROTOCOL

Controller Area Network (CAN) is a networking protocol commonly used in the automotive industry. It provides a means to interface multiple sensors, actuators, and microcontrollers, to a single serial bus. This decreases the complexity and cost of wiring required in large systems. CAN supports real-time control applications, such as a vehicle's Anti-lock Braking System (ABS) system. It is also used in less time constrained systems, for example, electric windows and lighting clusters, to decrease the cost of wiring [Bosch 1991].

#### 2.1.1 CAN protocol background

CAN provides a serial communications channel allowing message passing between multiple nodes. CAN is a multi-master protocol; any node may transmit a message if the transmission medium is idle. Carrier Sense Multiple Access with Collision Detection and Arbitration on Message Priority (CSMA/CD + AMP) is used to resolve contention if multiple nodes transmit simultaneously [Lawrenz 1997]. In the protocol, this is known as Non-Destructive Bit-wise Arbitration (NDBA). The transmitter of a message monitors the bit-value on the bus as it is sending. If the bit-value sent during the message's identifier field differs from that read off the bus then the sender has lost arbitration and will immediately end transmission. This allows any other higher priority messages to continue to be sent without any interruption. The message identifier

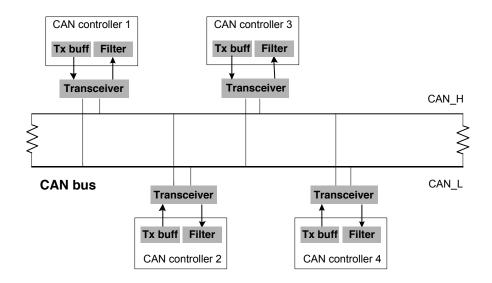

Figure 2.1 Multiple CAN nodes communicating over a two wire differential bus.

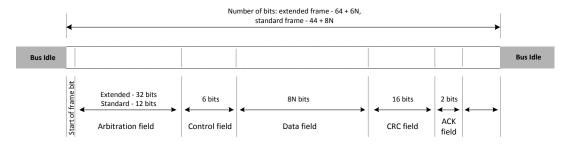

Figure 2.2 CAN 2.0A data frame, showing the formats for standard and extended frame messages.

field of the CAN message frame (Figure 2.2 [Bosch 1991]) is used for arbitration. In CAN, a logic '0' is dominant; this means the message with the lowest identifier will win arbitration. Any messages that lose arbitration must be re-queued and transmitted later when the transmission medium becomes idle again.

The CAN protocol guarantees consistency of data throughout the system. Messages are simultaneously broadcast to all network nodes, and nodes use the message identifier field to filter messages they are interested in. If a message is interrupted during transmission due to an error the transmission stops immediately and an error frame is transmitted to all nodes on the network notifying them of the error condition. The erroneous message is discarded by all receiving nodes and they will wait for the message to be retransmitted. Error detection is achieved by: monitoring the bit-level transmitted on a bus; Cyclic Redundancy Checks (CRC) of a message's data; checking bit-stuffing; and message frame checks. Fault confinement allows a persistently faulty node's transmitter to be switched off isolating it from the network [Bosch 1991].

Implementation of the physical channel is not fixed. The most common is a twowire balanced signaling scheme defined by ISO 11898-2, known as "high-speed CAN" [ISO 11898-2 2003]. The transmission medium usually uses a twisted pair of wires 2.2 TTCAN PROTOCOL 7

for greater noise immunity (labeled 'CAN\_H (CAN High)' and 'CAN\_L (CAN Low)') and are terminated with 120 ohm end of line resistors. CAN uses Non-Return to Zero signalling (NRZ) with bit-stuffing. A CAN node can signal 'recessive' and 'dominant' states. The CAN transceiver is wired so that a logic '0' bit value driven on the bus is 'dominant'. A logic '0' will override the 'recessive' logic '1' bit value if multiple nodes are trying to simultaneously access the bus. The physical medium performs a wired-and logical function [Lawrenz 1997].

#### 2.2 TTCAN PROTOCOL

Modern vehicles contain complicated distributed control systems of sensors and actuators. Currently, the CAN protocol is one of the most predominant communications protocols used in these types of networks [Leen and Heffernan 2002b]. It is an asynchronous event-triggered protocol, events are sent around the network as they occur. Due to the event-triggered nature, conflicts can occur on the bus when multiple messages are sent simultaneously. A priority based arbitration scheme is used to determine which message is transmitted on the bus. This introduces non-deterministic latency to message transmissions, complicating the design of systems with tight timing constraints, such as a closed loop distributed control system like those used in vehicle's brake or steer by-wire systems [Fuhrer et al 2000].

The increasing size and complexity of these types of systems has introduced a need for a variant of the protocol that provides deterministic timing across the system. This makes system design simpler and the design of more complicated systems possible. Time-Triggered CAN (TTCAN) is a variant of the CAN protocol that offers more precise timing. The TTCAN protocol is the addition of a session layer (layer 5 of the OSI model), defined by ISO 11898-4 [ISO 11898-4 2004], to the existing data link (OSI layer 2) and physical (OSI layer 1) layers of the existing CAN protocol [ISO 11898-1 2003].

TTCAN is a synchronous (time-triggered) protocol, where the transmission of messages is based on the progression of a globally synchronised time base. Each node has a pre-defined schedule of messages to transmit in pre-allocated time-slots. This way conflicts on the bus are eliminated and message latencies can be guaranteed [Fuhrer et al 2000].

#### 2.2.1 TTCAN protocol background

In TTCAN the transmission of messages is triggered by the progression of a shared global time base. Access to the CAN bus is controlled in a similar manner to a Time Division Multiple Access (TDMA) protocol, by pre-allocating time-slots for nodes so they can have exclusive access to the bus to transmit messages. Time synchronisation

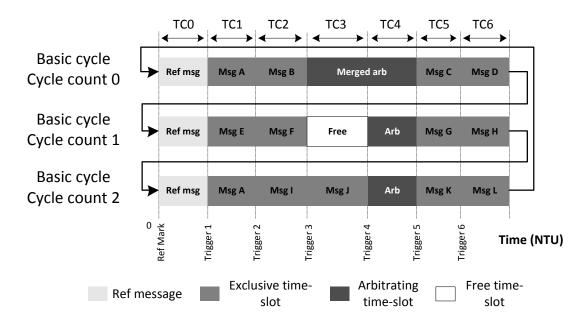

Figure 2.3 TTCAN matrix-cycle.

is achieved by the periodic transmission of a specific message known as a 'reference message' from a designated time-master node. On receiving the Start of Frame (SOF) bit of the reference message, the pre-defined transmission cycles of all nodes are restarted. Messages will be sent when their scheduled time-slot becomes active [Leen and Heffernan 2002b].

Using a time-triggered protocol allows deterministic timing of transmissions and a higher portion of the overall bandwidth of the system to be utilised. However, the latency of transmissions may be greater than when using an event-triggered protocol.

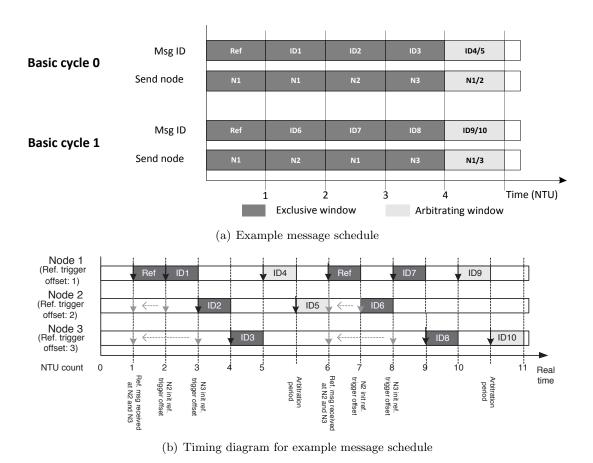

#### 2.2.2 TTCAN message schedule

The period elapsed between two consecutive reference messages is known as a basic-cycle. It is composed of a number of timing windows where messages are scheduled for transmission or reception [Fuhrer et al 2000]. TTCAN nodes are synchronised by a periodic sending of a reference message from a time-master node. On receiving a reference message, a node restarts and begins sending the pre-configured messages scheduled in its basic-cycle. More complex systems require greater flexibility in how messages can be sent and received; this can be achieved using a matrix-cycle, as illustrated in Figure 2.3. This allows a set of basic-cycles, each with different combinations of messages, to be repeated. The columns of the matrix-cycle are called transmission columns. At the start of each transmission column a sub-time window (called the transmission enable window) is defined; messages must be sent within this window otherwise they will run into the next time-slot, corrupting the next message.

There are three types of windows: free windows, arbitrating windows, and exclusive

2.2 TTCAN PROTOCOL 9

windows. Free windows are left for future expansion, nothing is transmitted in these slots. Arbitrating windows allow nodes to compete for access to the bus using CAN's NDBA to resolve conflicts. Exclusive windows are used to send scheduled time-triggered messages from a node without contention [Leen and Heffernan 2002b].

#### 2.2.3 Timing in TTCAN

Time in TTCAN is represented in terms of Network Time Units NTUs. The event trigger times for messages and network time reference marks are measured in terms of NTUs. TTCAN supports two different levels of timing resolution, Level 1 and Level 2. Level 1 timing is more coarse; the NTU period is the same duration as one CAN bit-time interval. In Level 2, the NTU period is a fraction of a physical second. It is calculated with a higher time resolution, increasing timing accuracy. Level 2 also allows drift compensation and synchronisation to another network or time source such as a GPS signal [Hartwich et al 2003].

#### 2.2.4 Error-handling in TTCAN

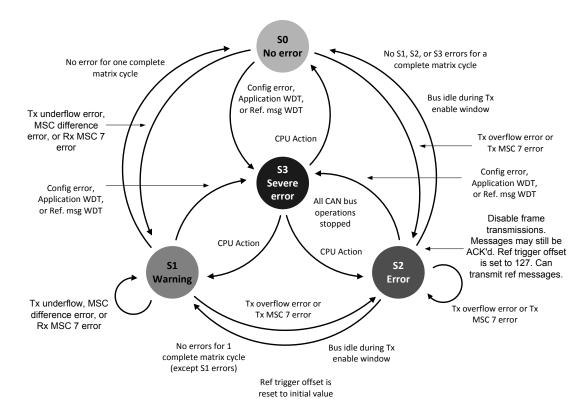

Figure 2.4 shows the ISO TTCAN error-handling state-machine [Leen and Heffernan 2002b]. Message Status Counter (MSC) registers are assigned to each exclusive time-slot message. They keep a record of any communication errors on the network. If there is a communications error when transmitting a message, the message's MSC count is incremented. If successful the count is decremented. If the count for any message's MSC reaches 7, or if the difference between any two MSCs is greater than 2, an error is reported [Leen and Heffernan 2002b]. Also, the number of scheduled transmissions from a node during a basic-cycle period is compared to the actual number of messages transmitted. If the number of messages sent is greater than expected a transmit overflow error is reported; if the number sent is less than expected a transmit underflow error is reported.

When there is no fault at a node the state-machine will be in the S0 state, as shown in Figure 2.4. If there is an MSC difference, MSC receive error, or transmit underflow error the node will enter the S1 warning state. If there is an MSC transmit, or transmit overflow error, the node will enter the S2 error state. Here, all transmissions from the node are disabled excluding reference messages and acknowledgements. A configuration error, application watch-dog timeout, or reference message watch-dog timeout will cause the node to enter the S3 state, indicating a severe error. Here, all transmissions on the bus are stopped.

Figure 2.4 TTCAN error handling state-machine.

#### 2.2.5 Startup and reintegration of potential time-masters

Due to the importance of keeping nodes in synchronisation, TTCAN provides redundant time-master nodes to provide a backup if the current time-master fails. Up to eight nodes on the network can be configured to be potential time-masters. In the case where multiple nodes are competing to become time-master, the node with the highest priority will become the time-master. When a potential time-master node is reset, or powers on, it will check for existing traffic on the bus and whether a reference message has been sent by another time-master. If no reference message is received after a timeout period, the potential time-master will send its own reference message and become the network time-master. If a reference message with higher priority is received, the potential time-master will stop sending its reference message and synchronise to this time-master. If a lower priority reference message is received, the potential time-master first synchronises to this time-master's basic-cycle. Then at the beginning of the next cycle it sends its own reference message. CAN NDBA will allow the higher priority reference message to win arbitration and the lower priority time-master will be over-ridden. A timeout period is used to detect if a reference message is missed by a potential time-master. After a timeout, potential time-masters will start sending their reference message, and arbitration will decide the new time-master [Fuhrer et al 2000].

Potential time-master nodes have a pre-defined initial reference message trigger

offset value. This value is used in the startup procedure to stagger the timeouts for triggering of the initial transmission of a reference message from time-master nodes. This initial reference message trigger offset value is pre-configured; nodes with a higher priority have a smaller offset. The staggering of timeouts allows the potential time-master with the highest priority to transmit first after system power-on or reset. This avoids unnecessary conflicts and arbitration on the bus that results from nodes transmitting simultaneously [Fuhrer et al 2000].

To enable greater flexibility, the TTCAN protocol allows transmission cycles to be triggered either periodically, or in response to an event. This is achieved by allowing a period of no activity between consecutive basic-cycles, known as a gap-period. A gap-period is initialised following the completion of the current basic-cycle before the next basic-cycle begins if the 'Next is gap' bit is set in the time-master's reference message. The gap-period finishes and the next basic-cycle begins when a reference message is transmitted from the time-master node in response to a corresponding event. This allows the system to be more responsive to certain events as the basic-cycle will be immediately restarted in response to the event. If the expected reference message is not detected during the gap-time a timeout will occur and the basic-cycle will restart. The initial gap-time timeout during synchronisation is required so that if a potential time-master, that is not the active time-master, is reset during a gap period, a reference message will not immediately be sent by the node causing it to incorrectly takeover as the active time-master.

#### 2.3 TIMED-TRIGGERED NETWORK PROTOCOLS

Time-triggered protocols are preferred to event-triggered protocols for use in safety critical systems such as steer and brake by-wire systems in the next generation of vehicles [Maier et al 2002]. Using a time-triggered protocol allows predictable and deterministic trigger times for communication between components on the system. The TTCAN protocol has been added as an extension to the existing CAN physical and data-link layers to allow time-triggered communication over existing CAN installations. Currently, CAN is the one of the most popular automotive control networks [Maier et al 2002]. This addition to the protocol allows existing networks to use deterministic timing and more efficient use of the available bandwidth [Fuhrer et al 2000]. A disadvantage of extending the existing CAN protocol is that the bandwidth is limited to the standard CAN bandwidth of 1 Mbit/s [Maier et al 2002].

The next generation of protocols must support higher bandwidths, determinism, fault-tolerance, and support for distributed control by offering a distributed global time-base [Kopetz 2001]. FlexRay and TTP/C are two next generation protocols designed to meet these requirements. Both FlexRay and TTP/C support redundancy as part of the protocol by specifying redundant buses, unlike TTCAN. They also support higher

data-rates than TTCAN; TTP/C runs at 25 Mbit/s and FlexRay runs at 10 Mbit/s. Flexray uses differential signalling over a two wire bus similar to CAN. The high data-rate is achieved by not allowing collisions as part of the protocol [FlexRay EPS 2006]. This means the bus can be actively driven high or low by the bus drivers. TTP/C uses IEEE standard 802.3 (Ethernet CSMA/CD) as the physical layer to achieve these high data-rates [TTChip 2005]. Another advantage over TTCAN is the clock synchronisation algorithms used in FlexRay and TTP/C are fully distributed so the protocol is tolerant of an arbitrary failure of any network node. TTCAN uses a master-slave clock synchronisation algorithm and only supports a single bus so it cannot support a single arbitrary fault of a network node [Maier et al 2002].

Currently, FlexRay is being developed by BMW and DaimlerChrysler and is used in the BMW X5, X6, 7 series, and in the Audi A8 [Lukasiewycz et al 2009]. TTP/C has been developed at the Technical University of Vienna and is used for engine control in the Lockheed Martin F16 and Aermacchi M-346; for the cabin pressure control system in the Airbus A380; and in the environment control system of the Boeing 787 Dreamliner [Lu and Lei 2010].

## 2.4 THE SPONSORING ORGANISATION'S IMPLEMENTATION OF TTCAN

The sponsoring organisation are using the TTCAN protocol as the backbone for communication between components in their next generation distributed marine vessel control system. Using a time-triggered architecture allows messages responsible for real-time control of the vessel to be allocated time-slots at the beginning of each basic-cycle. This way the control and feedback messages are deterministic making the response of the distributed control system more predictable and the design simpler. Diagnostic, status, heart-beat and other lower priority messages are sent in an arbitrating window at the end of each message cycle, so they do not interfere with the real-time control messages.

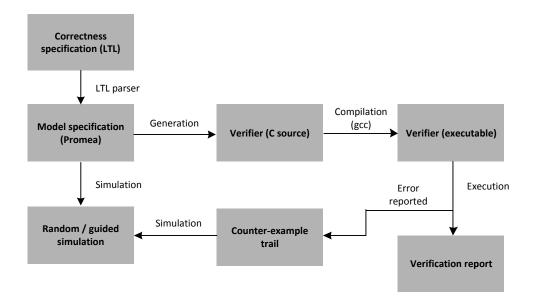

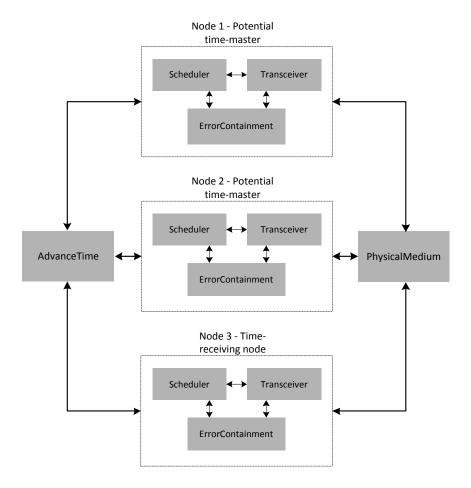

#### 2.4.1 System architecture

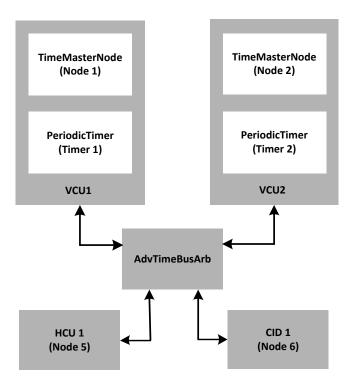

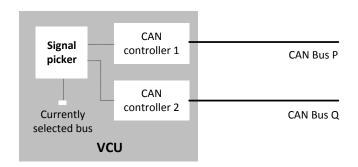

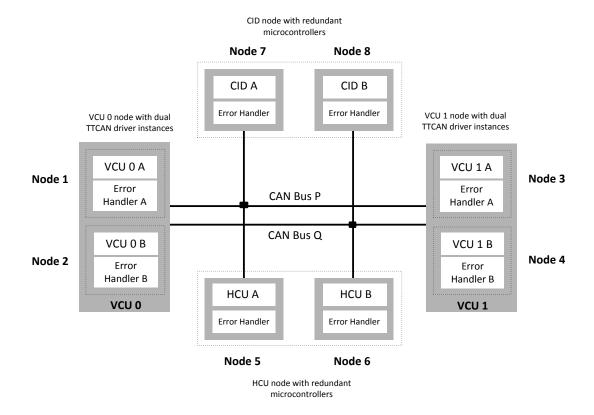

The system is a dual redundant distributed marine vessel control system based on the TTCAN protocol. The redundant CAN buses are labelled P and Q in Figure 2.5. The vessel is usually wired with a bus running down each side of the vessel. The system consists of three main types of modules: Control Input Devices (CID), Vessel Control Units (VCU), and Hydraulic Control Units (HCU). Each module is connected to both of the redundant CAN busses.

CIDs take input actions from the operator, such as adjusting the throttle levers or steering angle of the helm, and translate these to input commands that are sent to the VCU. Each CID has redundant STM32 Cortex M3 microcontrollers. Each microcontroller is connected to one of the redundant CAN busses. A system is able to be configured with multiple control stations or a single control station depending on the size of the vessel. On larger vessels, this allows an operator control of the vessel from different locations. Each station on a vessel may have a different configuration of CIDs.

The VCU processes control input commands from the CIDs and feedback messages from the HCUs. It uses response curves to translate the commands and feedback into output demands that are sent to the HCU to control the vessel's steering, thrust direction, and engine throttle. The VCU uses an NXP LPC2xxx microcontroller. This has two CAN controller modules, one connected to the P bus, and the other to the Q bus, as shown in Figure 2.5. When the currently active time-master VCU transmits messages, they are sent on both CAN buses. The VCU only accepts messages from one of these buses; the currently active bus being determined by the 'signal picker' module in the VCU. The VCU is the time-master of the system; it is responsible for synchronising the message schedules of the other network nodes. This is achieved by the active VCU periodically sending a TTCAN sync reference message.

The HCU is the interface to the vessel's thrust and direction control. Sensors on the hydraulic control units monitor a number of parameters including the temperature, r.p.m, and steering angle. This information is used for feedback control and diagnostics of the hydraulic units. The HCU controls hydraulic actuators to adjust the steering, thrust direction and vessel's trim, as well as control the engine throttle. Each HCU has a separate STM32 microcontroller connected to each CAN bus. There is also a separate STM32 microcontroller used for the independent backup system. Another STM32, known as the house keeper, is used to switch control between the redundant TTCAN busses and the backup system. A fault on either bus will cause the HCU to switch to the other bus. The system will switch to backup if this is selected by the operator. The backup system gives limited control of the vessel and is designed to be used if the primary system fails.

#### 2.4.2 Implementation of TTCAN message schedules

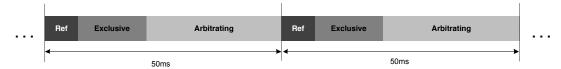

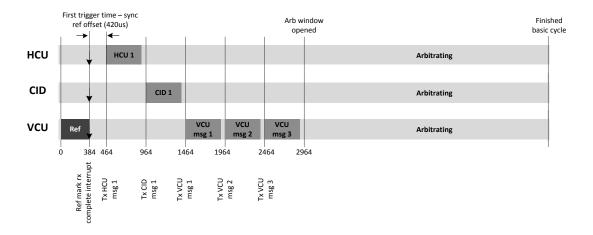

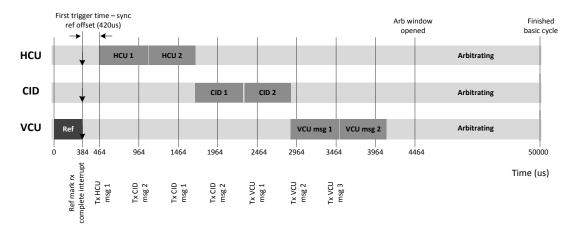

The currently active time-master VCU node sends a sync reference with a 50 ms period, as shown in Figure 2.6(a). Receiving the reference message restarts message transmission cycles at the other nodes on the system. The time-master is referred to as the 'sync master' in this implementation, as the 'time-master' is already used in the implementation to synchronise nodes to a real-time clock. The implementation currently differs from ISO TTCAN in that the schedules are only used for message transmissions. The nodes are not aware of messages that are scheduled to be received.

Figure 2.6(b) shows the format of a basic-cycle used in the sponsoring organisation's

Figure 2.5 Block diagram of the sponsoring organisation's redundant control system.

TTCAN implementation. The initial gap after the first reference message is due to the method used to trigger scheduled message transmissions. The schedule stored in each node contains the time until the next message is to be triggered, this is used to set a general purpose timer with the next scheduled message transmission time during the timer ISR triggered to send the currently scheduled message. However, the first scheduled messages timeout is loaded in the reference message receive complete interrupt. A fixed offset value of 420  $\mu$ s is subtracted from the first message trigger time to reduce the time delay before sending this initial message. Following this initial gap period, the schedule is divided into exclusive time-slots each with a duration of 500  $\mu$ s.

Following the initial reference message, there is an exclusive time-slot for each HCU to transmit. This is followed by exclusive time-slots for each CID on the currently active station to transmit. The number of CID slots is fixed to provide enough transmit slots for the station on the system with the greatest number of CIDs. In stations with fewer devices these become free slots with no transmission. There are three slots for transmissions from the currently active VCU. These are used to transmit throttle, steering, and reverse demand messages to the HCU to control the hydraulic units in response to control inputs. Following this, an arbitrating window is opened to allow transmission of periodic messages, such as heart-beat, diagnostic, fault, and button-state messages.

(a) Diagram showing the repeated 50 ms message transmission schedule.

(b) Timing diagram of a basic-cycle in the implementation.

Figure 2.6 Details of the message schedule used in the sponsoring organisation's TTCAN implementation.

#### 2.4.3 Modifications to TTCAN synchronisation reference message

A modified version of the ISO standard L2 synchronisation reference message frame is used in the implementation. Figure 2.7 shows a comparison of the ISO standard Level 2 (L2) synchronisation message with the version used in this implementation. The bits in the message fields with darker shading are not used in the implementation. A key difference is that the Master Reference Mark (MRM) fields, usually used in a L2 implementation to broadcast the sync master's MRM time-stamp to correct for clock drift in remote nodes, are not used in this implementation.

Even though a L2 synchronisation message is used, the implementation effectively uses a Level 1 timing scheme. The reception of the reference message at a node effectively resets a local general-purpose timer to restart a transmission schedule. The hardware does not allow a complete implementation of L1 timing. There does not appear to be any way to synchronise the Start of Frame (SOF) bit of the reference message to the system clock used to trigger message transmissions as is done in ISO TTCAN. In ISO TTCAN with L1 timing, a 16 bit free-running counter called Local\_Time, clocked by the system clock passed through the Time Unit Ration (TUR) prescaler, is used to keep track of the node's time. When the SOF bit of a reference message is received a time stamp is recorded, known in ISO TTCAN as a Ref\_Mark. The time stamp is subtracted from the current value of Local\_time, giving a value known as the Cycle\_Time. The Cycle\_Time value is used to trigger scheduled events in the current message cycle [Hartwich et al 2003]. The STM32 microcontroller used in the implementation contains a 16 bit free-running counter, but this is only able to store the time stamp of a received message in a register. The current timer value can not be accessed, so it can not be used to calculate the Cycle\_Time value by subtracting the last reference message time stamp from it.

Another difference in this implementation is that the Cycle\_Count field in the L2 message is used to select the current schedule to start, as shown by the field labelled Schd\_Sel in Figure 2.7(b). This value corresponds to the currently active station. The cycle count fields are optional in the ISO standard and are usually used to trigger a specific basic-cycle from a transmission matrix. The count is incremented after each basic-cycle until all cycles of the transmission matrix are completed. The network time resolution NTU\_Res bits 0-3, which are also optional in ISO TTCAN, contain a value that is used by nodes to select which of the periodic messages to transmit during their arbitrating windows. This also differs from the ISO standard; these bits are usually used to show the current state of the fractional part of a node's NTU time. The field holds a number between 0-19, and nodes will send a periodic command or control message whenever the number matches the node's assigned value. This value is pre-assigned when the node's schedules are configured.

| First<br>byte  | Next_is_Gap    | Reserved       | Cycle_Count<br>(5) | Cycle_Count<br>(4) | Cycle_Count<br>(3) | Cycle_Count<br>(2) | Cycle_Count (1) | Cycle_Count (0) |

|----------------|----------------|----------------|--------------------|--------------------|--------------------|--------------------|-----------------|-----------------|

| -              |                |                |                    |                    |                    |                    |                 |                 |

| Second<br>byte | NTU_Res<br>(6) | NTU_Res<br>(5) | NTU_Res<br>(4)     | NTU_Res<br>(3)     | NTU_Res<br>(2)     | NTU_Res<br>(1)     | NTU_Res<br>(0)  | Disc_Bit        |

| •              |                |                |                    |                    |                    |                    |                 |                 |

| Third<br>byte  | MRM (7)        | MRM (6)        | MRM (5)            | MRM (4)            | MRM (3)            | MRM (2)            | MRM (1)         | MRM (0)         |

| ,              |                |                |                    |                    |                    |                    |                 |                 |

| Fourth<br>byte | MRM (15)       | MRM (14)       | MRM (13)           | MRM (12)           | MRM (11)           | MRM (10)           | MRM (9)         | MRM (8)         |

| -              |                |                |                    |                    |                    |                    |                 |                 |

|                | MSB            |                |                    | ı                  | ı                  |                    | ı               | LSB             |

(a) ISO TTCAN L2 reference message format.

| Final         |             |             |              |                |                |                |                |              |

|---------------|-------------|-------------|--------------|----------------|----------------|----------------|----------------|--------------|

| First<br>byte | Next_is_Gap | Reserved    | Schd_Sel (5) | Schd_Sel (4)   | Schd_Sel (3)   | Schd_Sel (2)   | Schd_Sel (1)   | Schd_Sel (0) |

|               |             |             |              |                |                |                |                |              |

| Second byte   | NTU_Res (6) | NTU_Res (5) | NTU_Res (4)  | Arb_Msg<br>(3) | Arb_Msg<br>(2) | Arb_Msg<br>(1) | Arb_Msg<br>(0) | Disc_Bit     |

| •             |             |             |              |                |                |                |                |              |

| Third<br>byte | MRM (7)     | MRM (6)     | MRM (5)      | MRM (4)        | MRM (3)        | MRM (2)        | MRM (1)        | MRM (0)      |

| •             |             |             |              |                |                |                |                |              |

| Fourth byte   | MRM (15)    | MRM (14)    | MRM (13)     | MRM (12)       | MRM (11)       | MRM (10)       | MRM (9)        | MRM (8)      |

| -             | MSB         |             |              |                |                |                |                | LSB          |

(b) Reference message format used in the sponsoring organisation's implementation.

Figure 2.7 Comparison of ISO TTCAN L2 reference message format against the sponsoring organisation's implementation.

### Chapter 3

#### MODEL CHECKING BACKGROUND

Concurrent systems can be found in many applications. For example, networks of sensors and actuators in a car, or concurrently executing threads in an individual program. Due to the concurrent nature and ever increasing complexity of these types of systems, subtle errors in the system design may not always be picked up by conventional simulation and testing techniques [Merz 2000].

Model checking can be used as a system design aid to verify correctness of concurrently executing asynchronous processes. The inputs to a model checker are an abstracted model of a distributed system and a set of properties that must hold for the system. The model checker verifies the model by traversing every possible path through the model's state-space, checking correctness properties at each step. If a property does not hold, a counter-example trace is produced to show the sequence of events leading to violation of the property [Merz 2000].

Section 3.1 gives background on the use of formal methods and the model checking process in general. Section 3.2 gives an overview of the SPIN model checker, as this is the model checker that has been used in this research. Section 3.3 shows how a model and correctness properties are developed for a system, and the example of a coffee shop is used to illustrate these ideas. Section 3.4 explains why it may be necessary to model the timing of a system, and gives background on how this has been achieved by other authors. Finally, Section 3.5 describes how abstraction is used in model checking and why it is important.

## 3.1 INTRODUCTION TO FORMAL METHODS AND MODEL CHECKING

This section explains the link between model checking and other formal methods, such as formal specification and theorem proving. It gives a brief overview of model checking and includes details of some commonly used model checking tools.

#### 3.1.1 Specification and verification of systems using formal methods

Formal methods are a set of mathematical techniques and tools that allow developers to formally specify and verify systems. The techniques are used to help gain insight into a design and to help identify potential problems early in the development process [Clarke and Wing 1996]. Formal methods are usually applied to safety critical systems or systems where failure may lead to a large loss of revenue.

Formal specification of a system may be made using languages such as Z notation. Z is mathematical language used to formally specify a sequential system and its properties [Spivey 1988]. A more powerful technique is formal verification; two common techniques are theorem proving and model checking. These techniques allow developers to prove specified properties hold against a mathematical specification of a system [Clarke and Wing 1996]. Theorem proving involves developing a set of mathematical rules to represent a system and using these to prove that properties hold against the system. Model checking is a process that involves developing a finite state model to represent a system and checking that correctness properties hold in a exhaustive state-space search of the model of a system [Clarke and Wing 1996].

#### 3.1.2 Model checking overview

Model checking is a technique used to automatically verify correctness properties against a finite state model of a system. If a property is disproved a counter-example is generated showing the sequence of events leading to the violation of the property. The counter-example is a valuable aid in debugging a system [Merz 2000].

One of the limitations of model checking is the state-space explosion problem that occurs when models grow in size. This limits the size and complexity of systems that can be checked effectively [Clarke and Wing 1996]. Another limitation is that it cannot be guaranteed how accurately the model specified represents the implementation. An abstract representation of the implementation must be developed to reduce the state-space of the model. This reduces the time and memory required for verification. Simulated runs of the model and verification of properties that are expected to hold in the system are compared with the behavior of the implementation to help gain confidence in the model [Merz 2000]. This process is analogous to testing a mathematical model used to represent a control system. Here, comparing the simulated output with the observed behaviour of the system is also done to gain confidence in the model.

#### 3.1.3 Overview of model checking tools

There are a number of model checking tools available. Some of the more widely used ones are:

- **SPIN** The SPIN model checker checks a model specified in the PROMELA language against an Linear Temporal Logic (LTL) formula representing correctness properties to be verified against the system. SPIN is an explicit-state model checker; it adds new states to a representation of the state-space as it performs an exhaustive search of the model [Holzmann 2004].

- **SAL** The Symbolic Analysis Library (SAL) is a set of tools used for formal verification of transition systems. It includes a model checker that uses a symbolic representation of the state-space of a system [de Moura et al 2003].

- **SMV** The Symbolic Model Verifier (SMV) system is used to verify systems against correctness properties expressed using Computation Tree Logic (CTL). SMV also uses a symbolic representation of the state-space of the system [McMillan 1993].

- **FDR** The Failures-Divergence Refinement (FDR) tool is used to verify Communicating Sequential Processes (CSP) models by comparing processes and checking that one process is a valid refinement of the other [Formal Systems 2005]. CSP is a language for specifying concurrent processes that communicate by message passing [Roscoe 1997].

- UPPAAL, KRONOS The UPPAAL [Larsen and Pettersson 1997] and Kronos [Bozga et al 1998] model checkers allow checking of real-time systems, using a technique based on the theory of timed automata. Each automaton in the model has an associated clock value to keep track of timing, and interprocess communication is achieved through message passing and shared variables. These model checkers use a symbolic representation of the state-space of the system [McMillan 1993].

#### 3.2 OVERVIEW OF THE SPIN MODEL CHECKER

SPIN is a model checker that has become increasingly popular in industry. In SPIN, the input specification language for describing the model is called Process Meta-Language (PROMELA). Correctness properties to be checked against the system are described using Linear Temporal Logic (LTL). A processes is created in PROMELA to represent the control flow of a program. The individual threads of a multi-threaded application or simultaneously executing nodes on a distributed network are modelled in PROMELA by creating multiple processes. Shared variables and message channels are used to model interprocess communication.

A concurrent program can be visualised as a Finite State Machine (FSM) represented as a state transition diagram. This is commonly referred to as an automaton in model checking. The state of the system is the current expression being executed in each of the concurrent processes and the corresponding set of values of variables. The FSM contains nodes to represent every possible state the system enters, and edges to

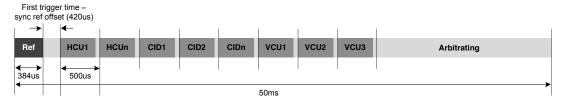

Figure 3.1 Block diagram of main components of the SPIN model checker.

represent possible transitions between states [Ben Ari 2008]. The SPIN model checker is used to traverse all possible paths through the concurrent system's FSM, checking specified safety and liveness properties at each step.

#### 3.2.1 Overview of the structure of the SPIN model checker

A block diagram of the main components of the SPIN model checker is shown in Figure 3.1 [Ben Ari 2008]. Initially, the concurrent system to be model checked is described using the PROMELA specification language. The PROMELA parser will find any syntax errors in the model. SPIN is able to perform random simulation runs through the model to check that it behaves as expected. Each simulation run takes a non-deterministic path through the state-space of the model. A SPIN simulation uses a random number generator to make any non-deterministic choice with the current time used as a seed.

The main use of SPIN is to verify the correctness of a model against a set of correctness specifications for all possible sequences of executions of events in the model. To perform this verification SPIN is applied to the PROMELA model to create a set of verifier output files that make a C program. The files have historically been given the prefix pan.\*. The verifier program is compiled using the gcc compiler. Running the verifier traverses every possible path of the FSM to check safety and liveness properties specified for the model. The Linear Temporal Logic (LTL) interpreter is used to convert an LTL formula into correctness claims that are checked against the model during verification. If any correctness property is violated an error will be flagged and a counter-example trail file will be created. The counter-example trail file is able to be

run by SPIN as a simulation showing the sequence of steps leading to the error [Holzmann 2004].

# 3.3 SPECIFICATION OF MODEL AND CORRECTNESS PROPERTIES

The models to be verified by the SPIN model checker are specified using a language known as PROMELA. PROMELA is a system description language used to model concurrent systems. It is not an implementation language. PROMELA is designed to efficiently describe the way different processes in a system interact with each other.

#### 3.3.1 Overview of the PROMELA specification language

In PROMELA, multiple processes are used to model the control flow of concurrently executing modules of a system. These may be the individual threads of a multi-threaded program or multiple nodes on a distributed networked system. Interprocess communication is modelled using shared variables, that processes have read and write access to, and by message channels where messages are sent between processes. Message channels are used to model synchronous and asynchronous communications. Asynchronous communications is modelled using a message buffer with multiple entries; messages are placed in the buffer if there is room and retrieved in FIFO order. Synchronous communication is modelled using a zero length buffer. In this case, the sender will block until the receiving process has reached the corresponding receive channel statement [Holzmann 2004].

#### 3.3.2 Specification of correctness properties with LTL

Temporal logic formulae are logical statements that allow sequences of a program's states to be described. LTL formulae are built from atomic propositions; symbols representing expressions which evaluate to true or false. Propositions are combined by a set of logical operators: and  $(\land)$ , or  $(\lor)$ , not  $(\neg)$ , implies  $(\rightarrow)$ , and equivalent  $(\leftrightarrow)$ . Temporal operators, always  $(\Box)$ , eventually  $(\diamondsuit)$ , and until (U), are used to add an element of time to a formula. For example, p U q means proposition p is true until the instant when q is true [Holzmann 2004].

In SPIN, LTL properties are used to specify safety and liveness properties against a model. Safety properties are specifications that a correctness property should hold over an exhaustive state space search of a model. This is represented in LTL by the always operator ( $\square$ ), meaning the specified proposition is always invariantly satisfied throughout the search. A liveness property specifies that some event eventually happens. Liveness is represented in LTL by the eventually operator ( $\diamondsuit$ ), meaning the

specified property is eventually satisfied during the search. Checking liveness properties is important, as a safety property may hold in the trivial case where the process is doing nothing at all. Operators can be combined to check more interesting properties, for example, the always and eventually operators are combined to check that an event occurs infinitely often in a system. The model must always eventually pass through a certain state to satisfy the property [Ben Ari 2008].

# 3.3.3 Specification of a model and correctness properties for a coffee shop

This model is a simple example to show how the specification of a model and correctness properties are developed in SPIN. The process of placing an order at a coffee shop is modelled. The initial model consists of two Customer processes representing customers named Joe and Kaye, and a CoffeeServer process. As customers arrive they queue up and place an order for a coffee. The coffee server makes their coffee and gives the coffees to the customers in the order they have arrived. Correctness properties are used to show that customers always receive the correct order and that customers eventually get a chance to order.

Listing 3.1 PROMELA source for 'Customer' process from the coffee shop model.

```

proctype Customer(byte customer)

{

mtype orderedCoffee;

mtype receivedCoffee;

/* A customer can place an order for a coffee of any type

and will accept a coffee when it is ready. */

ORDER_COFFEE: atomic

{

/* First customers queue up. */

QUEUE ! customer;

10

/* Customer orders any type of coffee. */

:: skip ->

orderedCoffee = LATTE;

:: skip ->

orderedCoffee = CAPPUCCINO;

fi;

ORDERS ! orderedCoffee;

/* Wait for the coffee. */

20

COFFEE[customer] ? receivedCoffee;

RECEIVED_COFFEE:

goto ORDER_COFFEE;

}

```

When customers arrive at the coffee shop they queue up for a coffee. This is represented in the model using the QUEUE asynchronous message channel, as shown in Listing 3.1. In the model, messages representing customer's identifiers are placed into the queue in the order they have arrived. The queued messages are received by the CoffeeServer process in FIFO order. A non-deterministic condition is used to select the coffee ordered by the customer. A message representing the type of coffee ordered by the customer is placed in the ORDERS asynchronous message channel. This is again received by the CoffeeServer process, where the orders are processed in FIFO order. An atomic block is required so the queuing and ordering events in different Customer processes cannot interleave. This way the sequences in which customers arrive and place orders for coffee are the same. It is assumed in the model that the customers place their orders in the order that they arrive, as is usually the case in a shop.

Initially, the CoffeeServer process takes the coffee orders out of the ORDERS queue in the order they have been placed by the customers. Following this, the coffees are then delivered to the customers in the order they have queued; the most recent coffee made is given to the first customer in the queue. Finally, the type of coffee prepared is passed as a channel parameter through the COFFEE zero-length synchronisation message channel to this customer.

**Listing 3.2** PROMELA source for 'CoffeeServer' process from the coffee shop model.

Listing 3.3 Definitions of state labels and local variables used in the coffee shop model.

```

/* Type of coffee received by Joe. */

#define joe_received_type Customer[1]:receivedCoffee

/* Type of coffee ordered by Joe. */

#define joe_order_type Customer[1]:orderedCoffee

/* Joe receives a coffee. */

#define joe_received_coffee Customer[1]@RECEIVED_COFFEE

/* Joe receives the correct coffee. */

#define joe_correct_order (joe_order_type == joe_received_type)

```

A safety and liveness property are checked against this model. A liveness property is checked to ensure that Kaye eventually receives a coffee. The LTL formula specifies

that the Customer process representing Kaye always eventually passes through the RECEIVED\_COFFEE state (defined in Listing 3.3).

```

[] <> kaye_received_coffee

```

This property initially failed verification due to the case where Joe repeatedly orders coffees, not giving Kaye a chance to order. This is commonly known as starvation of the process. The property passes verification when fairness is enabled in the verification. Enabling fairness means that if a process has an executable statement that is always executable in a run then the statement must eventually be executed [Ben Ari 2008]. In this model, the Customer processes are given a 'fair' chance to place orders for coffees.

A safety property is also checked to ensure that customers always receive the coffee that they ordered. The LTL formula specifies that it is always the case that when Joe receives a coffee, the coffee ordered is the same as the coffee received. The formula uses the implication operator (->) so the property only checks the coffees are the same when the order is received.

```

[] (joe_received_coffee -> joe_correct_order)

```

Listing 3.4 shows a modification of the CoffeeServer process, where coffee making jobs are dispatched by the coffee server to other workers in the coffee shop. In this model, there are two workers named Bob and Mark. Each is represented by a CoffeeMaker process, as shown in Listing 3.5. The liveness property checked in the previous model holds in this model; assuming weak fairness, a customer always eventually receives a coffee. However, the safety property, checking that the customers always receive the coffee they ordered, does not hold in this model.

**Listing 3.4** PROMELA source for 'CoffeeServer' process, modified to give jobs to separate 'CoffeeMaker' processes.

```

proctype CoffeeServer()

mtype orderedCoffee;

mtype finishedCoffee;

byte firstCustomer;

/* Current state of the coffee makers. */

mtype makerState[TOTAL_MAKERS];

makerState[BOB] = READY;

makerState[MARK] = READY;

10

START:

if

:: ORDERS ? orderedCoffee ->

/* Send a request for a coffee maker to go make the

coffee, if they are not busy. */

15

i f

:: makerState[MARK] != BUSY ->

makerState[MARK] = BUSY;

```

```

MAKE_COFFEE[MARK] ! orderedCoffee;

:: makerState[BOB] != BUSY ->

20

makerState[BOB] = BUSY;

MAKE_COFFEE[BOB] ! orderedCoffee;

:: else ->

skip

25

fi:

:: FINISHED_COFFEE[MARK] ? finishedCoffee ->

/* Received the coffee made by Mark. */

makerState[MARK] = READY;

/* Coffees given to customers in the order they are queued. */

QUEUE ? firstCustomer;

30

COFFEE[firstCustomer] ! finishedCoffee;

:: FINISHED_COFFEE[BOB] ? finishedCoffee ->

/* Received the coffee made by Bob. */

makerState[BOB] = READY;

QUEUE ? firstCustomer;

35

COFFEE[firstCustomer] ! finishedCoffee;

fi;

goto START;

}

```

**Listing 3.5** PROMELA source for 'CoffeeMaker' process from the coffee shop model.

```

proctype CoffeeMaker(byte maker)

{

mtype orderedCoffee;

START:

/* Receive a request to make a coffee. */

MAKE_COFFEE[maker] ? orderedCoffee;

/* Finished making the coffee. */

FINISHED_COFFEE[maker] ! orderedCoffee;

goto START;

```

Listing 3.6 shows an error trail file generated by the violation of the safety property checked against the modified coffee shop model. As the names of workers and customers in the model are defined using the preprocessor, usually the raw values would appear in the output trace. To improve readability the trail is modified by replacing the raw values with the defined names. The mtype construct is used where possible to simplify the model. However, it cannot be used for the customer and worker names as they are used to index into arrays and these index values cannot be assigned to mtype elements.

The error trail shows the sequence of events that caused the property to be disproved. The sequence of events leading to the error begins with Kaye queueing then placing an order for a Latte. An order to make the coffee is then given to one of the coffee makers that is not busy. In the mean time, Joe arrives and places an order for a Cappuccino, and this order is promptly made by the other coffee maker. The coffee

server gives this coffee to the first queued customer. In this case, it is Kaye. Kaye is given the Cappuccino when she asked for a Latte. Some time later, the other coffee maker finishes making the Latte and this is then given to Joe. The orders have been mixed up due to the first coffee maker taking longer than the other to finish making the coffee, and the assumption that the server only remembers the order in which the customers arrived and not what each customer actually ordered. The model is an example of a race-condition, as the sequence of events in concurrent processes causes unexpected results in the model.

**Listing 3.6** SPIN error trail when checking the safety property against the modified coffee shop model.

```

QUEUE!KAYE

Customer: (KAYE), Order: (LATTE)

ORDERS!LATTE

ORDERS?LATTE

Send order to Bob to prepare

MAKE_COFFEE[BOB]!LATTE

4

MAKE COFFEE [BOB]?LATTE

QUEUE! JOE

Customer: (JOE), Order: (CAPPUCHINO)

2

ORDERS! CAPPUCHINO

10

ORDERS?CAPPUCHINO

Send order to Mark to prepare

MAKE_COFFEE[MARK]!CAPPUCCINO

3

MAKE_COFFEE[MARK]?CAPPUCCINO

5

FINISHED_COFFEE [MARK] ! CAPPUCCINO

15

FINISHED_COFFEE [MARK]?CAPPUCCINO

QUEUE?KAYE

COFFEE [KAYE]! CAPPUCCINO

8

COFFEE [KAYE]? CAPPUCCINO

Customer: (KAYE), Recv: (CAPPUCCINO)

FINISHED_COFFEE[BOB]!LATTE

FINISHED_COFFEE [BOB]?LATTE

QUEUE?JOE

COFFEE [JOE] ! LATTE

COFFEE [JOE] ? LATTE

25

Customer: (JOE), Recv: (LATTE)

```

# 3.4 OVERVIEW OF TECHNIQUES FOR MODELLING THE PROGRESSION OF TIME IN A SYSTEM

In the coffee shop example (Section 3.3.3) it may be necessary to check a property that a coffee is always received within a certain time frame. To check this timing property the specification of the model has to be modified to model the progression of time. This section gives an overview of various techniques that have been used to model the

progression of time in model checkers. The technique used to model the progression of time for the models developed during this research is described in Section 4.1.

Saha and Roy used a variant of SPIN modified to model discrete time called Discrete Time SPIN (DT-SPIN) to verify correctness the TTCAN protocol [Saha and Roy 2007]. DT-SPIN allows multiple timers to be declared in the model. The increment of a global 'tick' variable is used to control the progression of time throughout the model. Events occurring at predefined times are modelled by initialising a timer with a timeout value for an event and triggering the event on this timeout. This allows the timing of events to be scheduled to occur in a certain time-slot. The time events occur and time elapsed between events is able to be modelled. A limitation of this approach is that the timing of events within the same time-slice is not known, but only the order the events occur. If the events are in the same time-slice but in different processes, verification of the model will check all possible interleavings of events in the time-slice, as would occur in an untimed model [Bosanacki and Dams 1999].

Saha and Roy have also used a technique called synchronous calendar to model the progression of time when verifying the TTCAN startup protocol using the SAL model checker [Saha et al 2007]. Synchronous calendar is a variant of a technique previously developed by Dutertre and Sorea to model time when verifying the fault-tolerant real-time startup protocol in the Time Triggered Architecture (TTA) [Dutertre and Sorea 2004]. The technique is based on time scheduling techniques commonly used in discrete event simulation; multiple concurrent processes each have an associated time-out value that is used to control the timing of execution of events in each process. Constructs known as 'event calendars' are used to model asynchronous communication between processes. These calendar events are used to model interaction between processes by message passing that may cause a receiving process to perform a discrete state transition. Saha and Roy have modified this technique to model the synchronous message transmissions that they have assumed to occur in this TTCAN model.

A similar technique to handle the progression of time known as Variable Time Advance (VTA) has also been used by a number of authors to reduce the state-space required when solving optimisation problems using the SPIN model checker. In VTA, when time is advanced, the current time skips forward to the instant when an event causes the next state transition. The current time is increased by varying amounts, unlike a fixed-time strategy where time is incremented in a pre-defined interval with events becoming active when the time-step reaches their interval. VTA allows periods of no activity, that are not of interest in the verification, to be skipped reducing the state-space of the model. VTA was used by Brinksma and Mader to handle timing in a model used to first verify then optimise the program for a Programmable Logic Controller (PLC) for a chemical plant [Brinksma et al 2002]. The technique has also been used subsequently by Ruys when optimising a schedule for producing personalised identification cards [Ruys 2003] and by Gu, He, and Yuan when finding an optimal bus

and task schedule of a distributed embedded system [Gu et al 2007]. Also, Weininger and Cofer used an explicit representation of time similar to this to reduce the state-space when modelling the ASCB-D startup synchronisation algorithm using SPIN [Weininger and Cofer 2000].