# An Auxiliary Power Distribution Network for an Electric Vehicle

A Thesis submitted in partial fulfilment of the requirements for the degree of Master of Engineering (Electrical and Electronic)

at the

University of Canterbury Christchurch, New Zealand

By William Wen-Hou Chen B.E. (Hon.)

University of Canterbury Christchurch, New Zealand 31<sup>st</sup> May 2003 The University of Canterbury purchased a modern Toyota MR2 sports car with the intention of converting it into an electric vehicle. Similar to the common combustion engine vehicles, electric vehicles requires power and control systems to operate the 12Vdc auxiliaries, such as lights, indicators and wipers. Traditional technology results in a large number of wires in the wiring harness. To reduce the number of wires, an alternative method is to use a pair of control lines and a universal power connection around the vehicle. This power and control system is named the "Power Distribution Network" and it is implemented by using multiple power converters and a differential control system.

This thesis presents the design, implementation, and test results of the Power Distribution Network for the MR2. The 300Vdc nominal battery voltage is converted to an intermediate voltage of 48V. This configuration is considered more efficient than the usual 12V distribution system since smaller and lighter wires can be used to carry same amount of power. The Power Distribution Network operates off the 48V intermediate voltage, and provides 12V output power to drive all the auxiliaries in the vehicle. The Power Distribution Network also has the ability of detect faults from the auxiliary loads as well as turn on and off these loads.

The Power Distribution Network is implemented with two major systems: the Auxiliary Power System, which consists of a 360W Cuk converter with current limiting control circuits to step-down voltage from the 48V intermediate voltage to the 12V. The other system is the CAN Control system, it is developed using micro-controllers and standalone CAN controllers that control and monitor the auxiliary loads in the vehicle.

The prototype Power Distribution Network is fully operational and has been tested with eight of 12V light bulbs which are used to simulate the auxiliary loads in the vehicle. Experimental measurements show that the prototype is able to successfully control the light bulbs under the full load condition. This confirms that in principle the Power Distribution Network is suitable as the power and control system for the auxiliary loads in an electric vehicle.

| <u> </u> | Page ii |  |  |

|----------|---------|--|--|

## **ACKNOWLEDGMENTS**

I would like to express my gratitude to those who have helped me in the course of this thesis. First and foremost, I would like to gratefully thank my supervisors, Dr. Richard Duke and Dr. Simon Round for their guidance, assistance and encouragement throughout the thesis.

Thanks are also extended to the technical staff members: Mr. Ken Smart and Mr. Ron Battersby – for their technical assistance in the laboratory. I would also like to thank Mr. Philipp Hof for his assistance with the software testing and Mr. Nick Smith for his help with the PCBs manufacturing.

I would like to thank the members of power electronics postgraduate group, Dr. Hamish Laird, Tony Rocco, Si Kuok Ting, Irene Ting and Leo Hsieh for providing good advice and a pleasant working environment in the laboratory.

Last but not least, I would like to express my deepest thank to my friend Nicole and my parents David and Mimi for their encouragement and support over the years of study.

| <del></del> | <br> | Page iv |  |  |

|-------------|------|---------|--|--|

## **PUBLICATION RELATED TO THIS THESIS**

William Chen, Richard Duke, Simon Round "Design of an Auxiliary Power Distribution Network for an Electric Vehicle", Delta 2002, the first international workshop conference. Christchurch, New Zealand, Jan 2002.

William Chen, Richard Duke, Simon Round "Design of an Auxiliary Power Distribution Network for an Electric Vehicle", AUPEC 2003, Australian Universities Power Engineering Conference. Christchurch, New Zealand, Sept 2003.

# **TABLE OF CONTENTS**

| AE | STRA       | CT                                                         | I   |

|----|------------|------------------------------------------------------------|-----|

| AC | CKNOV      | VLEDGMENTS                                                 | III |

| PU | BLICA      | ATION RELATED TO THIS THESIS                               | V   |

| TA | BLE C      | OF CONTENTS                                                | VII |

| LI | ST OF      | FIGURES                                                    | IX  |

| LI | ST OF      | TABLES                                                     | XI  |

| 1  | INTRO      | DDUCTION                                                   | 1   |

|    | 1.1<br>1.2 | University of Canterbury's Electric Vehicle Thesis Outline |     |

| 2  | POW        | VER DISTRIBUTION NETWORK                                   | 5   |

|    | 2.1        | AUXILIARY LOAD CURRENT INVESTIGATION                       | 7   |

|    | 2.2        | EFFICIENCY IMPROVEMENT METHOD                              |     |

|    | 2.3        | POWER SUPPLY PLACEMENT IN THE MR2                          | 13  |

|    | 2.4        | Auxiliary Power System                                     |     |

|    | 2.5        | CAN (CONTROLLER AREA NETWORK) CONTROL SYSTEM               | 15  |

|    | 2.6        | SUMMARY                                                    | 16  |

| 3  | CON        | VERTER DESIGN                                              | 17  |

|    | 3.1        | CUK CONVERTER TOPOLOGY                                     | 19  |

|    | 3.2        | Design Objectives                                          | 20  |

|    | 3.3        | COMPONENT CALCULATION                                      |     |

|    | 3.4        | CONVERTER SIMULATION                                       |     |

|    | 3.5        | CIRCUIT LOSSES ESTIMATION                                  |     |

|    |            | 3.5.1 Conduction Loss in the Switching Devices             |     |

|    |            | 3.5.2 Switching Loss in the Switching Devices              |     |

|    | 26         | 3.5.3 Losses in the Passive Components                     |     |

|    | 3.6<br>3.7 | SWITCHING FREQUENCY SELECTIONINDUCTOR DESIGN               |     |

|    | 3.7        | COMPONENT SELECTIONS                                       |     |

|    | 5.0        | 3.8.1 Capacitor                                            |     |

|    |            | 3.8.2 MOSFET and Diode Switch                              |     |

|    | 3.9        | SUMMARY                                                    |     |

| 4          | CON      | VERTER CONTROL DESIGN                               | 31                                      |

|------------|----------|-----------------------------------------------------|-----------------------------------------|

|            | 4.1      | Voltage Mode Control                                | 31                                      |

|            | 4.2      | CURRENT MODE CONTROL                                | 33                                      |

|            | 4.3      | CURRENT MODE CONTROL CIRCUIT DESIGN                 | 34                                      |

|            | 4.4      | VOLTAGE FEEDBACK COMPENSATION DESIGN                | 38                                      |

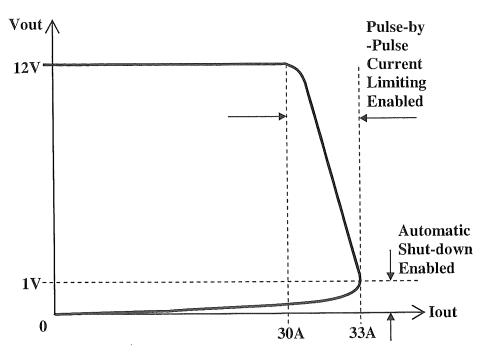

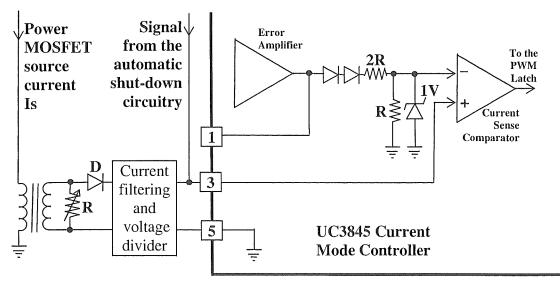

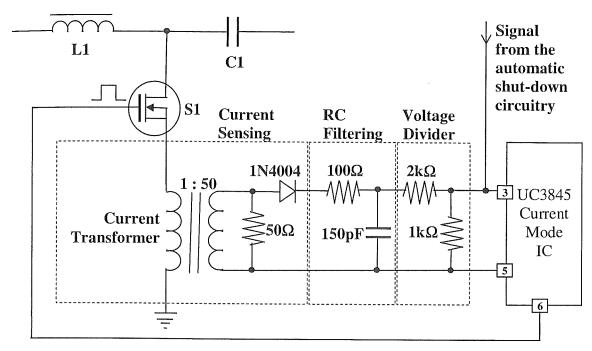

|            | 4.5      | CURRENT SENSING AND PULSE-BY-PULSE LIMITING CONTROL | 40                                      |

|            | 4.6      | AUTOMATIC SHUT-DOWN PROTECTION                      | 44                                      |

|            | 4.7      | CONSTRUCTION                                        | 45                                      |

|            | 4.8      | SUMMARY                                             | 46                                      |

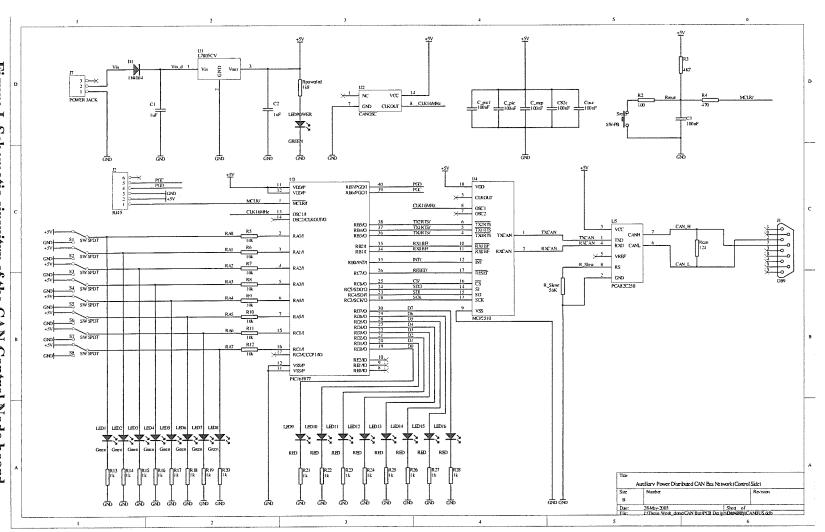

| 5          | CAN      | CONTROL SYSTEM DESIGN                               | 47                                      |

|            | 5.1      | THE CAN PROTOCOL                                    | 49                                      |

|            | ٥.1      | 5.1.1 CAN Protocol Standards                        | 50                                      |

|            |          | 5.1.2 Message Frame Format                          | 51                                      |

|            | 5.2      | CAN IMPLEMENTATION METHOD                           | 52                                      |

|            | 5.3      | SERIAL PERIPHERAL INTERFACE (SPI)                   |                                         |

|            | 5.4      | CAN CONTROL SYSTEM DESIGN                           | 55                                      |

|            | 5.4      | 5.4.1 Requirements                                  |                                         |

|            |          | 5.4.2 Implementation of the CAN Control System      | 55                                      |

|            | 5.5      | SUMMARY                                             | 59                                      |

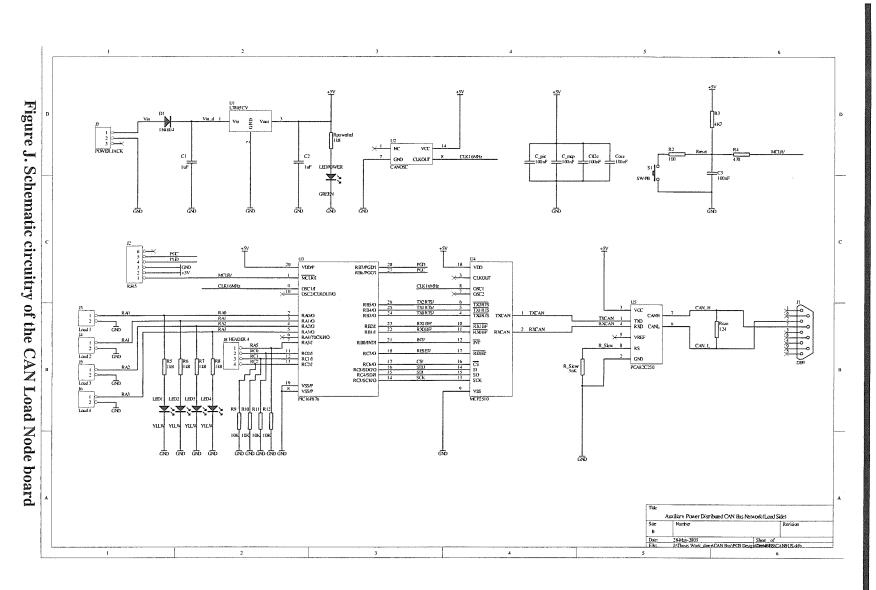

| 6          |          | CAN CONTROL NODE                                    |                                         |

|            | 6.1      | CAN CONTROL NODECAN LOAD NODE                       |                                         |

|            | 6.2      | Load Fault-Detector                                 | 67                                      |

|            | 6.3      | LOAD FAULT-DETECTOR                                 | 69                                      |

|            | 6.4      | SYSTEM SOFTWARE                                     | 71                                      |

|            |          | 6.4.1 Message Reception                             | 72                                      |

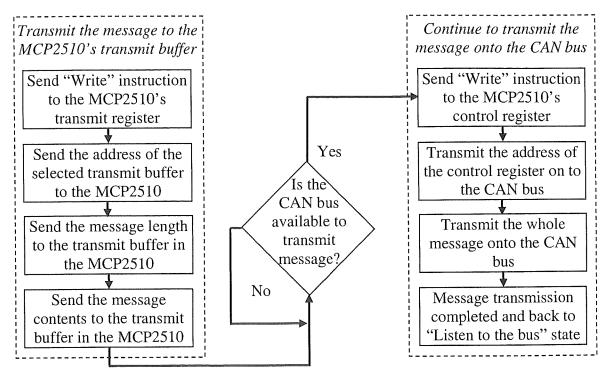

|            | 6.5      | 6.4.2 Message Transmission                          | 72                                      |

|            | 6.5      | SUMMARY                                             |                                         |

| 7          | PRO      | OTOTYPE PERFORMANCE                                 |                                         |

|            | 7.1      | CONVERTER TESTS                                     |                                         |

|            | 7.2      | CONVERTER CONTROL TESTS                             |                                         |

|            | 7.3      | CAN CONTROL SYSTEM TESTS                            | 81                                      |

|            | 7.4      | POWER DISTRIBUTION NETWORK (OVERALL) TESTS          | 84                                      |

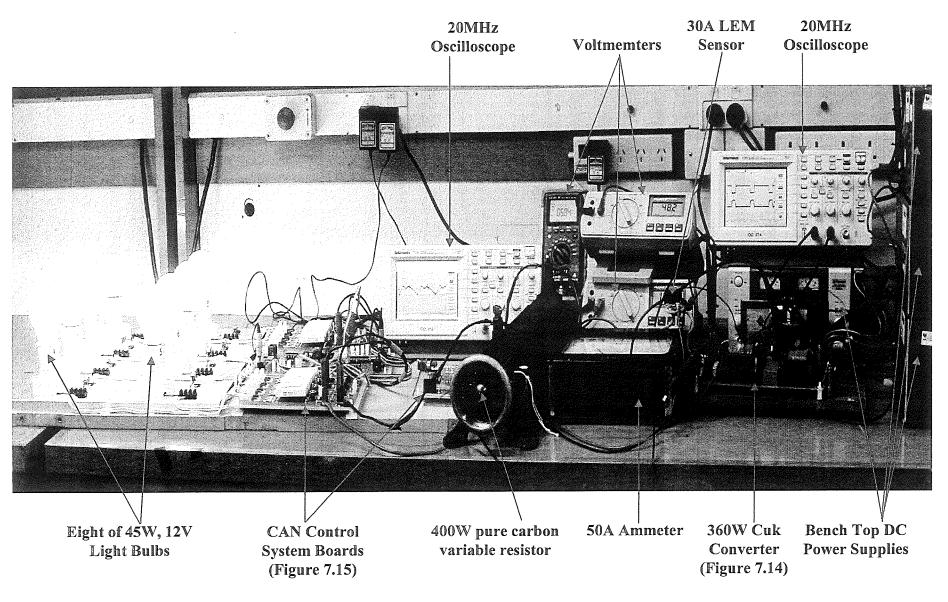

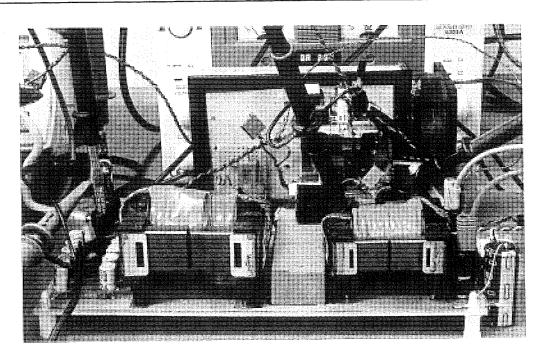

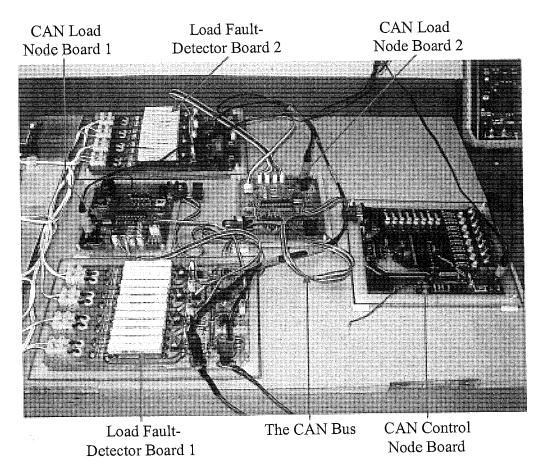

|            | 7.5      | PROTOTYPE PHOTOGRAPHS                               | 85                                      |

|            | 7.6      | SUMMARY                                             | 88                                      |

| 8          | FU       | TURE DEVELOPMENT & CONCLUSION                       | 89                                      |

|            | 8.1      | FUTURE DEVELOPMENT                                  | 89                                      |

|            | 8.2      |                                                     | 90                                      |

| ו פרצו     | ा जाना न | ENCES                                               | 93                                      |

| K          | trek!    | UNCED                                               | ~~~410000000000000000000000000000000000 |

| <b>A</b> 1 | PPENI    | DIX                                                 | 95                                      |

# LIST OF FIGURES

| Figure 1.1 1903 Krieger Electric Car                                                                              | 1                 |

|-------------------------------------------------------------------------------------------------------------------|-------------------|

| FIGURE 2.1 POWER DISTRIBUTION NETWORK OVERALL DIAGRAM                                                             | 9<br>. 11<br>. 12 |

| FIGURE 2.5 POWER SUPPLY PLACEMENTS IN MR2                                                                         | . 17              |

| Figure 3.1 Cuk Converter                                                                                          | . 20              |

| FIGURE 3.2 THE CUK CONVERTER SIMULATION MODEL                                                                     | . 23              |

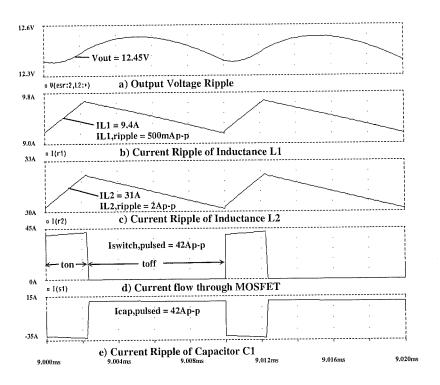

| FIGURE 3.3 SIMULATION WAVEFORMS                                                                                   | . 24              |

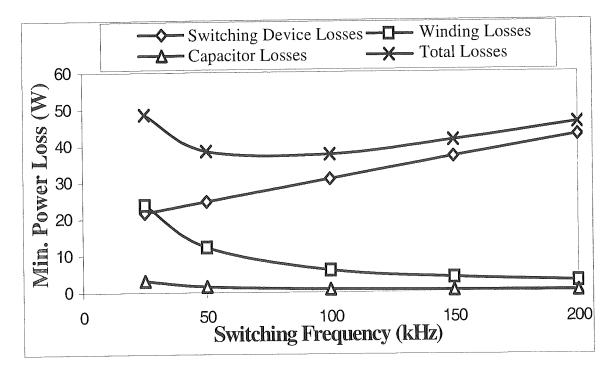

| FIGURE 3.4 ESTIMATED CUK CONVERTER COMPONENT LOSS                                                                 | . 26              |

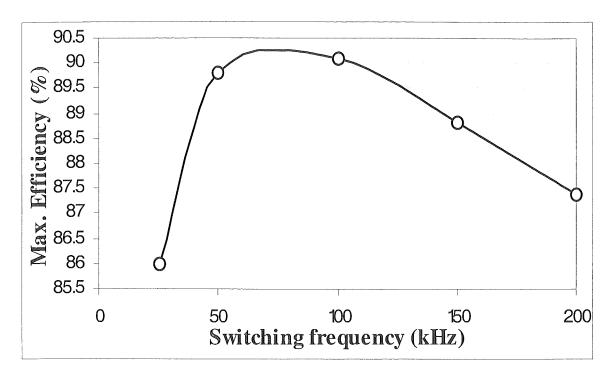

| FIGURE 3.5 SIMULATED CUK CONVERTER EFFICIENCY                                                                     | .27               |

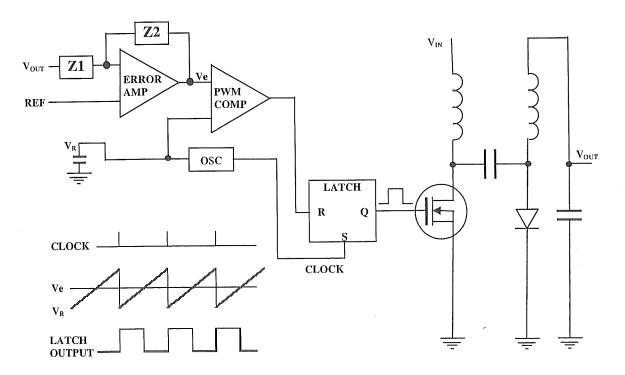

| FIGURE 4.1 VOLTAGE MODE CONTROL                                                                                   | 32                |

| FIGURE 4.2 CURRENT MODE CONTROL                                                                                   | 34                |

| FIGURE 4.3 INTERNAL CIRCUITRY OF THE UC3845                                                                       | 35                |

| FIGURE 4.4 CURRENT MODE CONTROL CIRCUIT FOR THE CUK CONVERTER                                                     | 37                |

| FIGURE 4.5 BLOCK DIAGRAM OF THE VOLTAGE FEEDBACK COMPENSATION NETWORK                                             | 38                |

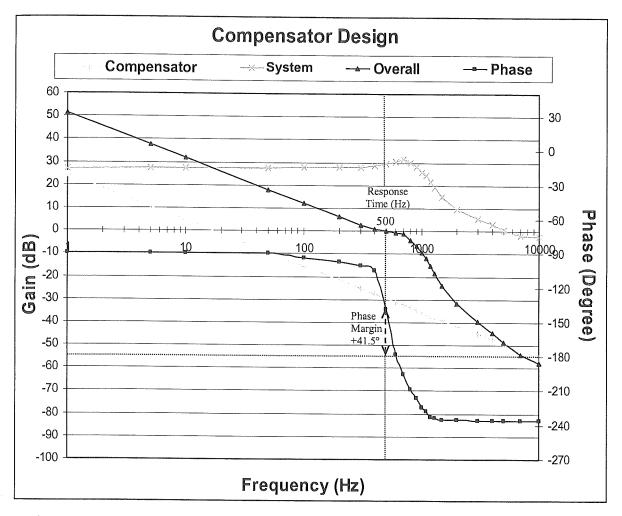

| FIGURE 4.6 BODE-PLOT OF THE CUK CONVERTER                                                                         | 39                |

| FIGURE 4.7 PLANNED CURRENT LIMITING STRATEGY                                                                      | 41                |

| FIGURE 4.8 THE UC3845 CURRENT SENSE INPUT CONFIGURATION                                                           | 42                |

| FIGURE 4.9 TRANSFORMER-COUPLED CURRENT SENSING AND FILTERING CIRCUITS                                             | 43                |

| FIGURE 4.10 SOURCE CURRENT SENSED AFTER THE RC FILTERED AND VOLTAGE DIVIDED                                       | . 43              |

| FIGURE 4.11 AUTOMATIC SHUT-DOWN PROTECTION FOR THE CUK CONVERTER                                                  | 44                |

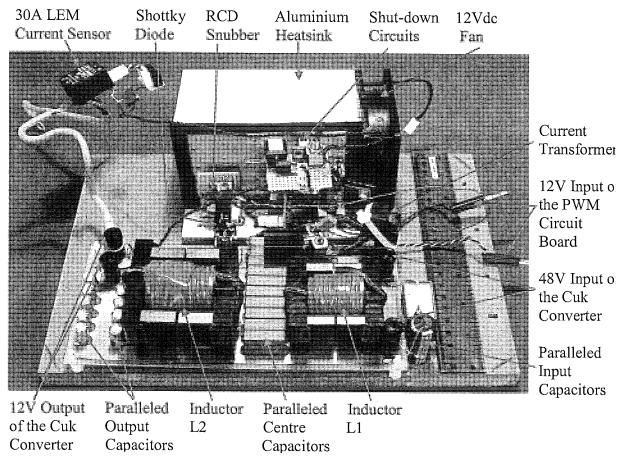

| FIGURE 4.12 PHOTOGRAPH OF THE CONSTRUCTED 36W CUK CONVERTER                                                       | 45                |

|                                                                                                                   | 40                |

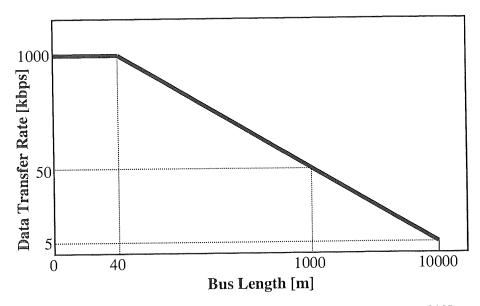

| FIGURE 5.1 RELATION BETWEEN DATA TRANSFER AND BUS LENGTH                                                          | 40                |

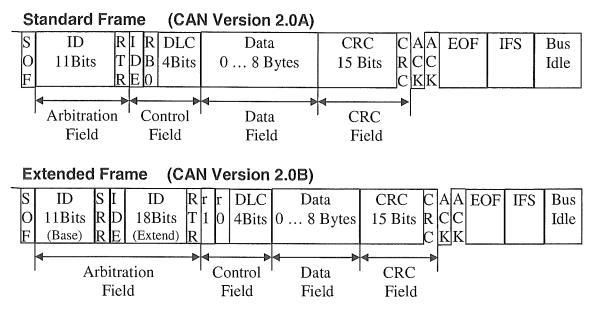

| FIGURE 5.2 ISO/OSI REFERENCE MODEL [14]                                                                           | 30<br>51          |

| FIGURE 5.3 STANDARD AND EXTENDED FRAMES FORMAT USED IN CAN                                                        | JI                |

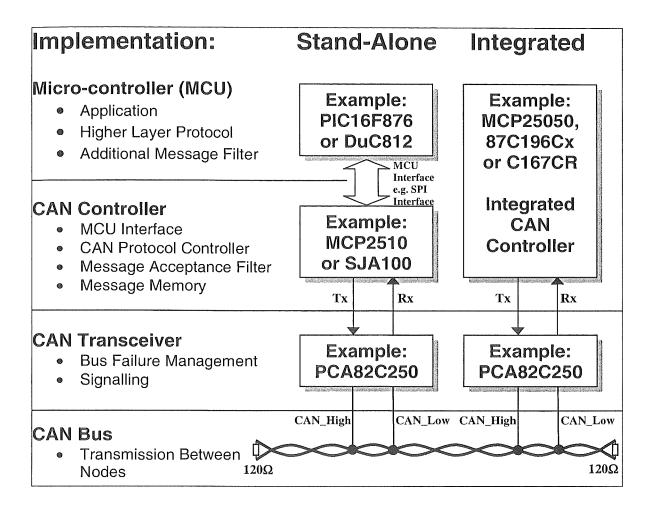

| FIGURE 5.4 POSSIBLE STRUCTURE OF THE CAN NODE                                                                     | 33<br>54          |

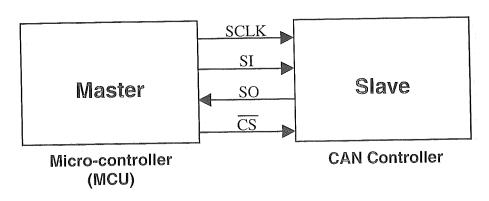

| FIGURE 5.5 SINGLE MASTER, SINGLE SLAVE SPI IMPLEMENTATION                                                         | 54<br>57          |

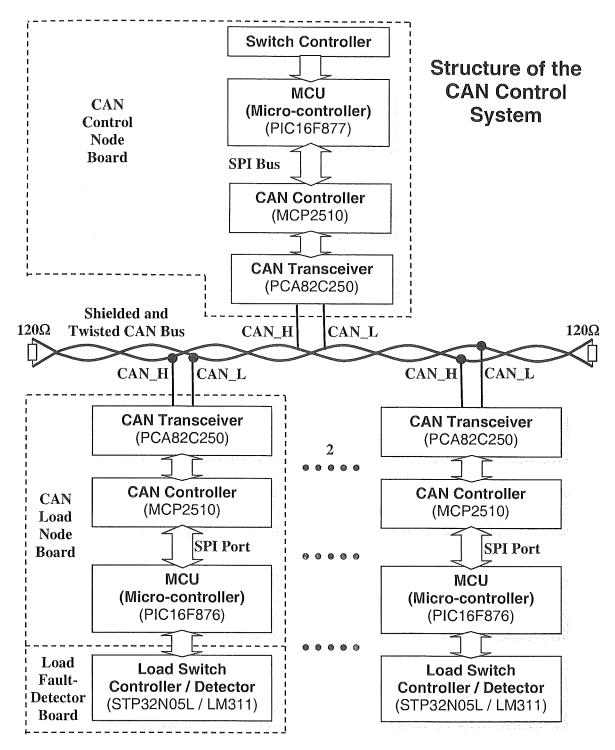

| FIGURE 5.6 CAN CONTROL SYSTEM IN THE EV                                                                           | 37<br>50          |

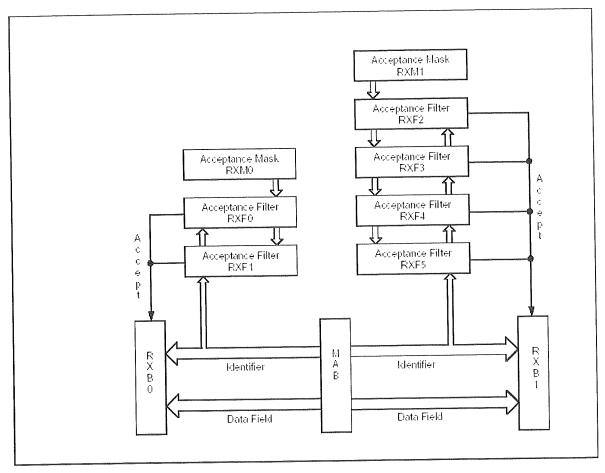

| FIGURE 5.7 RECEIVE BUFFER BLOCK DIAGRAM [15]                                                                      | 38                |

| CAN CONTROL ED NODE                                                                                               | 63                |

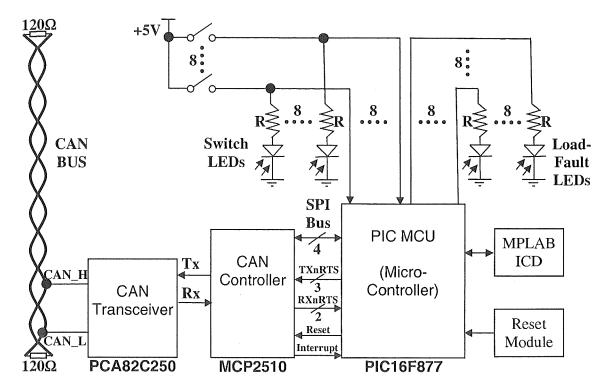

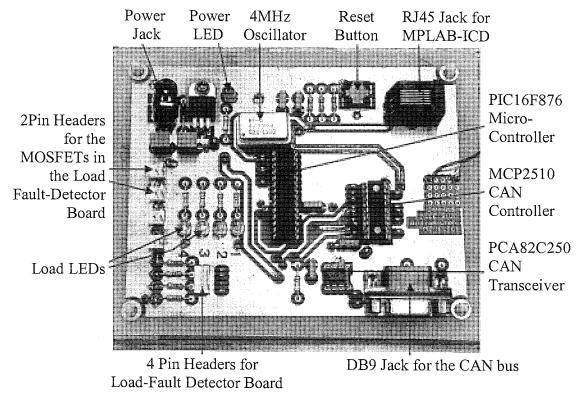

| FIGURE 6.1 DETAILED BLOCK DIAGRAM OF THE CAN CONTROLLER NODE                                                      | 65                |

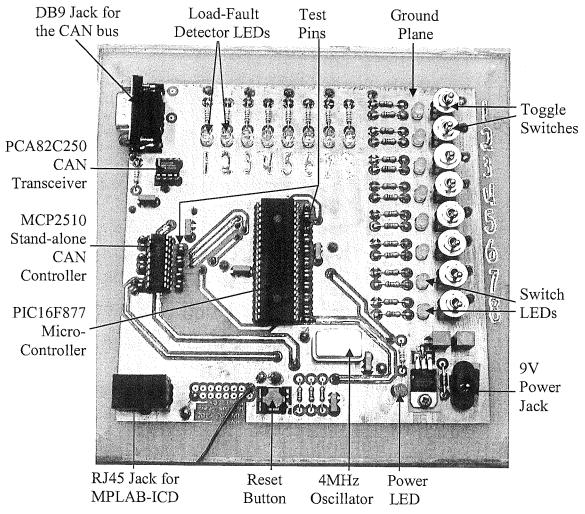

| FIGURE 6.2 THE CAN CONTROL NODE BOARD                                                                             | 66                |

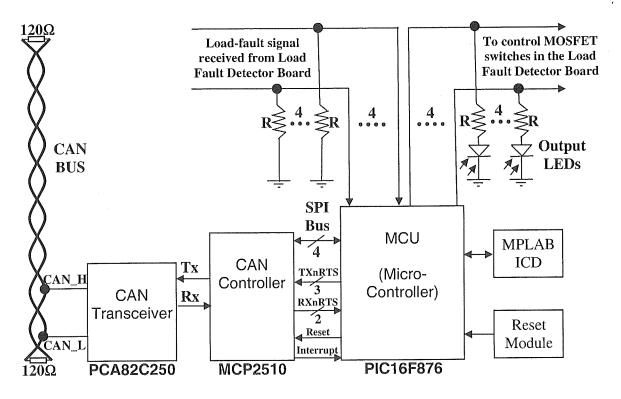

| FIGURE 6.3 DETAILED BLOCK DIAGRAM OF THE CAN LOAD NODE  FIGURE 6.4 ONE OF THE COMPLETED CAN LOAD NODE BOARD       | 67                |

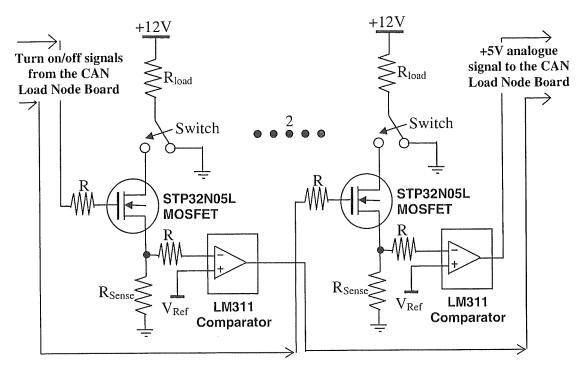

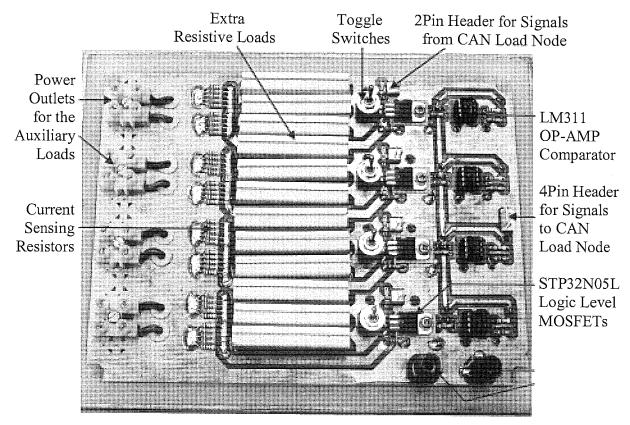

| FIGURE 6.4 ONE OF THE COMPLETED CAN LOAD NODE BOARD  FIGURE 6.5 DETAILED BLOCK DIAGRAM OF THE LOAD FAULT-DETECTOR | 68                |

| FIGURE 6.5 DETAILED BLOCK DIAGRAM OF THE LOAD FAULT-DETECTOR                                                      | 69                |

| FIGURE 6.6 ONE OF THE COMPLETED LOAD FAULT-DETECTOR BOARD                                                         | 70                |

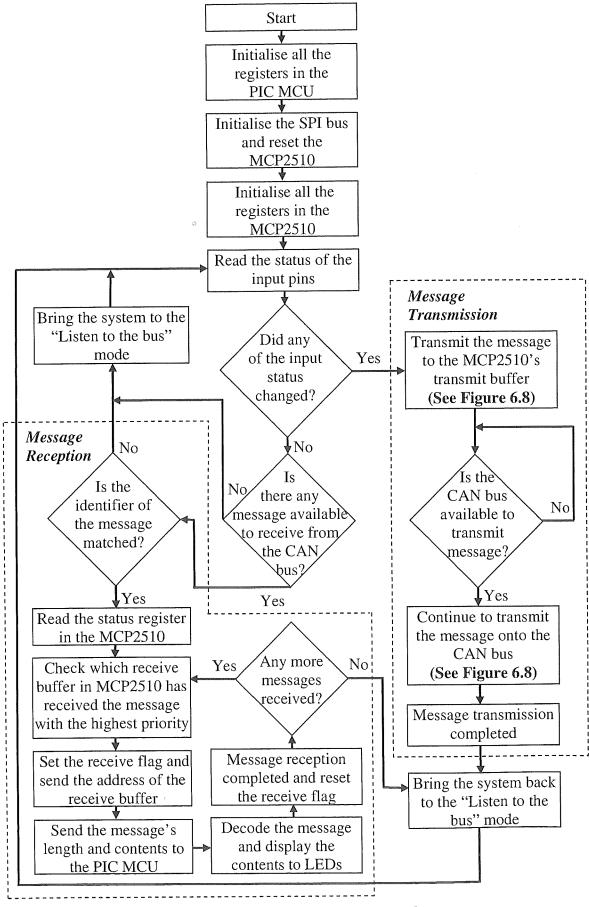

| FIGURE 6.7 THE MAIN PROGRAM FLOW OF THE OPERATION CODE                                                            | 73                |

| FIGURE 0.8 CAN IMESSAGE TRANSMISSION                                                                              | / -               |

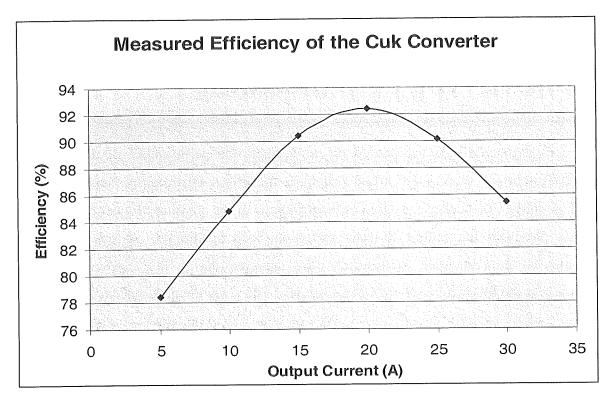

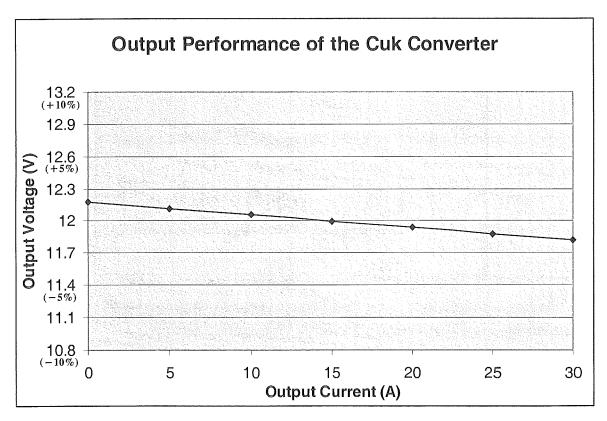

| FIGURE 7.1 MEASURED EFFICIENCY OF THE 360W CUK CONVERTER PROTOTYPE          | .76   |

|-----------------------------------------------------------------------------|-------|

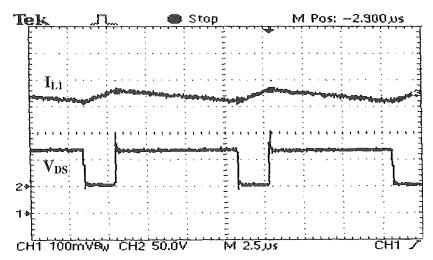

| FIGURE 7.2 INPUT INDUCTOR CURRENT RIPPLE & MOSFET SWITCHING WAVEFORM        | .77   |

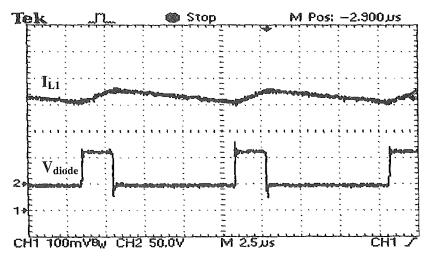

| FIGURE 7.3 INPUT INDUCTOR CURRENT RIPPLE & DIODE SWITCHING WAVEFORM         | .77   |

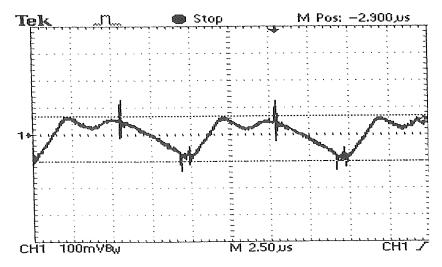

| FIGURE 7.4 12V OUTPUT VOLTAGE RIPPLE (100MV/DIV). TIME SCALE: 2.5 µS/DIV    | 77    |

| FIGURE 7.5.12V OUTPUT VOLTAGE CHARACTERISTIC                                | 78    |

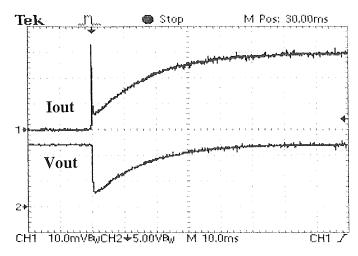

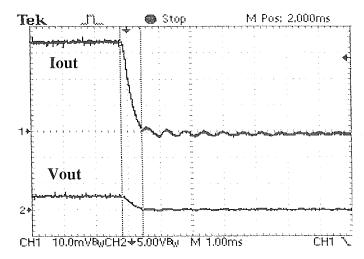

| FIGURE 7.6 TRANSIENT LOADING RESPOND UNDER FULL LOAD, TIME SCALE: 10MS/DIV  | 80    |

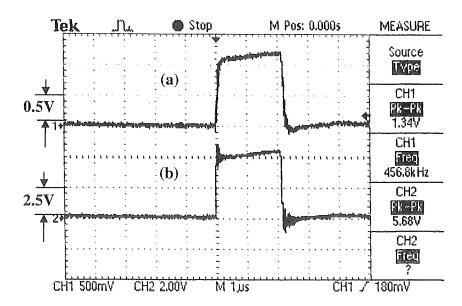

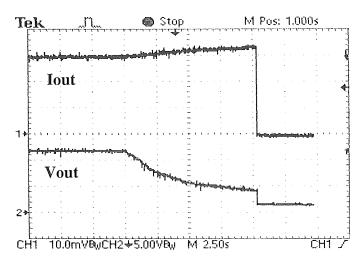

| FIGURE 7.7 CURRENT LIMITING AND SHUT-DOWN AT FULL LOAD, TIME SCALE: 2.5/DIV | 80    |

| FIGURE 7.8 A CLOSE LOOK AT THE SHUT-DOWN OPERATION, TIME SCALE: 1MS/DIV     | 80    |

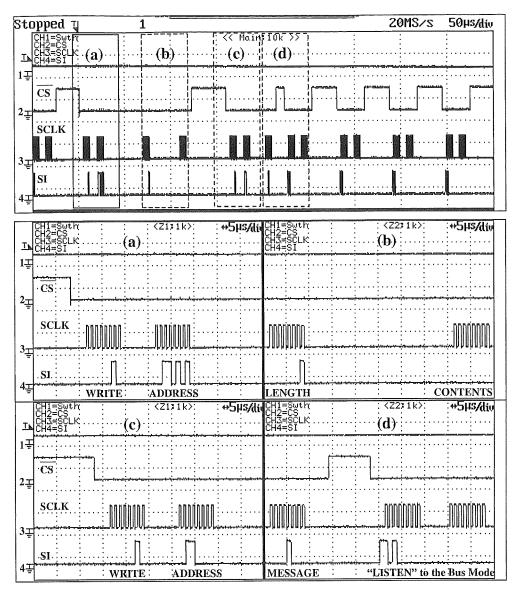

| FIGURE 7.9 MESSAGE TRANSMISSION ON SPI BUS TO THE MCP2510 AND THE CAN BUS   | 82    |

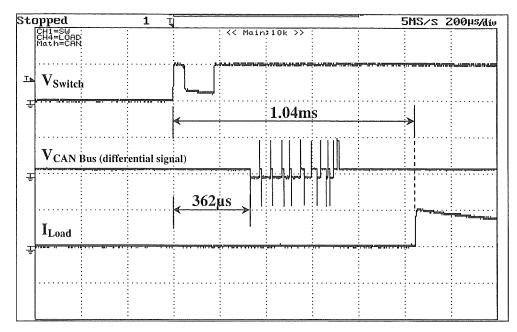

| FIGURE 7.10 TRANSMISSION DELAY WHEN THE LOAD SWITCHED ON                    | 83    |

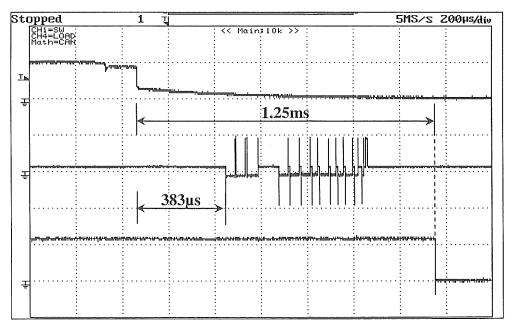

| FIGURE 7.11 TRANSMISSION DELAY WHEN THE LOAD SWITCHED OFF                   | 83    |

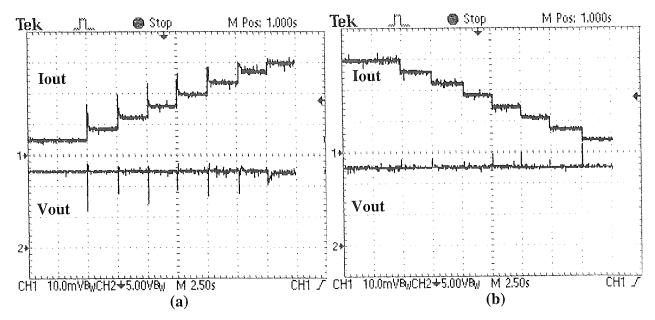

| FIGURE 7.12 WAVEFORM CAPTURED AT THE OUTPUT                                 | 84    |

| FIGURE 7.14 CUK CONVERTER (THE AUXILIARY POWER SYSTEM) TESTING PHOTOGRAPH   | 87    |

| FIGURE 7.15 CAN CONTROL SYSTEM PROTOTYPE TESTING PHOTOGRAPH                 | 87    |

|                                                                             |       |

| FIGURE A. CURRENT CONSUMPTION TABLE 1 OF 2                                  | 97    |

| FIGURE B. CURRENT CONSUMPTION TABLE 2 OF 2                                  | 98    |

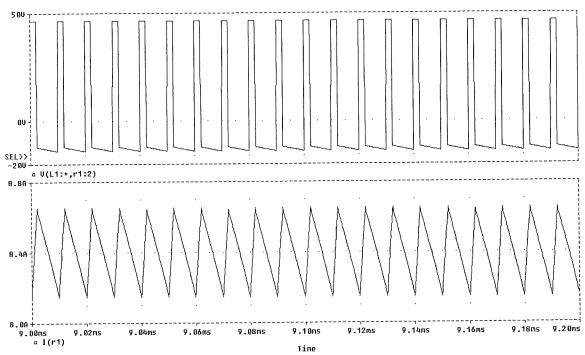

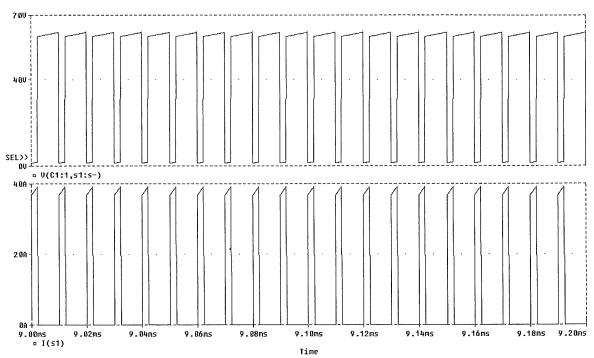

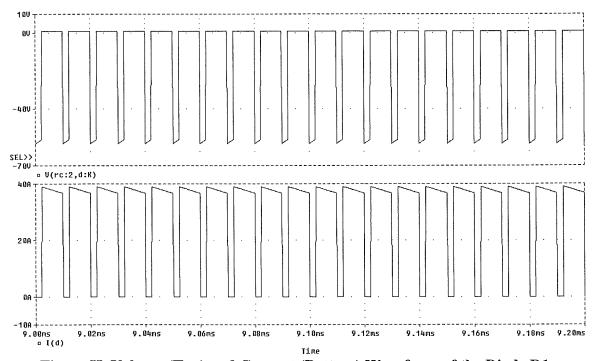

| FIGURE C. VOLTAGE (TOP) AND CURRENT (BOTTOM) WAVEFORM OF THE INDUCTOR L1    | 101   |

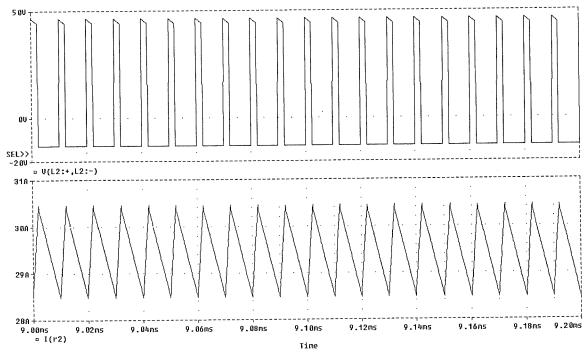

| FIGURE D. VOLTAGE (TOP) AND CURRENT (BOTTOM) WAVEFORM OF THE INDUCTOR L2    | 101   |

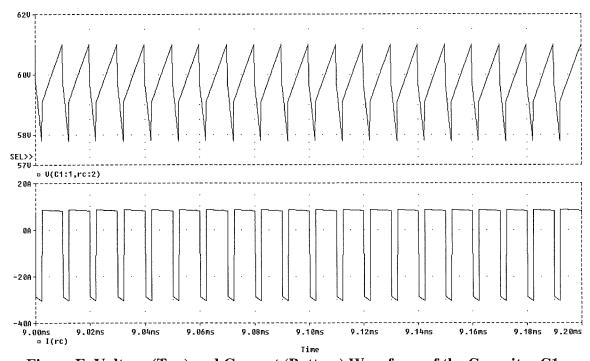

| FIGURE E. VOLTAGE (TOP) AND CURRENT (BOTTOM) WAVEFORM OF THE CAPACITOR C1   | 102   |

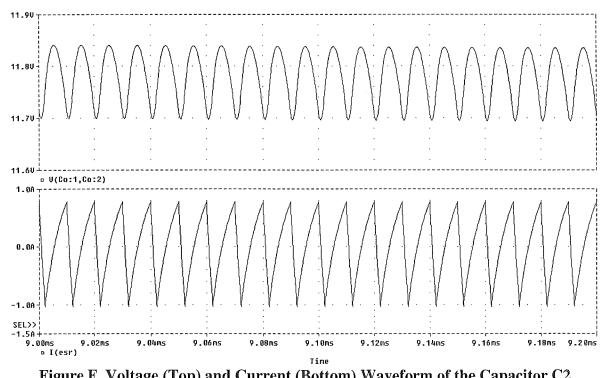

| FIGURE F. VOLTAGE (TOP) AND CURRENT (BOTTOM) WAVEFORM OF THE CAPACITOR C2   | 102   |

| FIGURE G. VOLTAGE (TOP) AND CURRENT (BOTTOM) WAVEFORM OF THE MOSFET S1      | 103   |

| FIGURE H. VOLTAGE (TOP) AND CURRENT (BOTTOM) WAVEFORM OF THE DIODE D1       | .103  |

| FIGURE I. SCHEMATIC CIRCUITRY OF THE CAN CONTROL NODE BOARD                 | . 105 |

| FIGURE J. SCHEMATIC CIRCUITRY OF THE CAN LOAD NODE BOARD                    | . 107 |

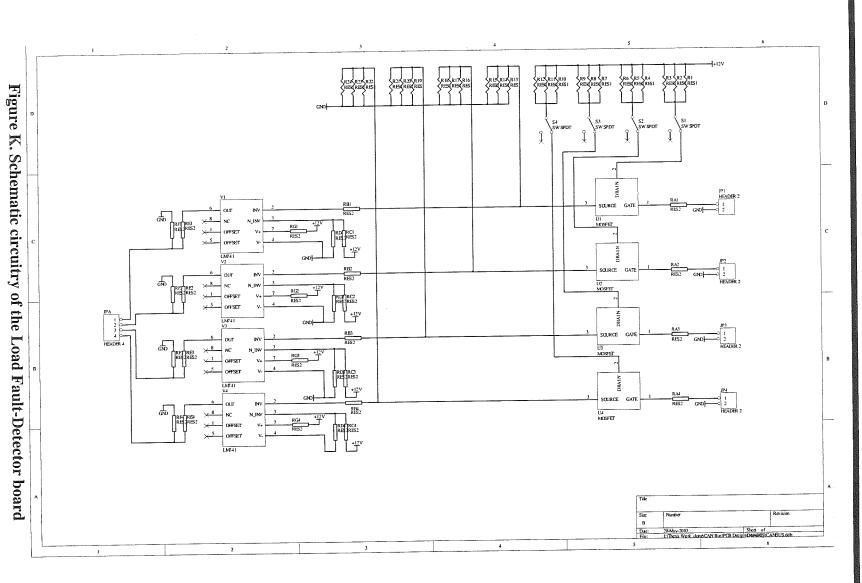

| FIGURE K. SCHEMATIC CIRCUITRY OF THE LOAD FAULT-DETECTOR BOARD              | 100   |

| FIGURE K SCHEMATIC CIRCUITRY OF THE LOAD FAULT-DETECTOR BOAKD               | 、10フ  |

# LIST OF TABLES

| Table 2.1 Auxiliary Loads in the Vehicle – MR2<br>Table 2.2 Maximum Current Demand of the Loads<br>Table 2.3 Power Consumption of Vehicle's Lights with Replacement of LEDs. | 9  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.1 Equations of Cuk Converter                                                                                                                                         | 20 |

| TABLE 3.2 DESIGN REQUIREMENT                                                                                                                                                 |    |

| TABLE 3.3 CALCULATED COMPONENT SIZES AT THE SWITCHING FREQUENCY OF 100 KF                                                                                                    |    |

| TABLE 3.4 INPUT PARAMETERS OF INDUCTANCE DESIGN                                                                                                                              |    |

| TABLE 3.5 DESIGN RESULTS OF INPUT AND OUTPUT INDUCTOR                                                                                                                        |    |

| Table 4.1 Pin Function Description (Refer to Figure 4.3)                                                                                                                     | 35 |

| TABLE 5.1 KEY FEATURES OF THE MCU AND CAN CONTROLLER USED                                                                                                                    | 56 |

|  |            | • |  |  |

|--|------------|---|--|--|

|  |            |   |  |  |

|  |            |   |  |  |

|  |            |   |  |  |

|  | -          |   |  |  |

|  |            |   |  |  |

|  |            |   |  |  |

|  |            |   |  |  |

|  |            |   |  |  |

|  |            |   |  |  |

|  | Page xii   |   |  |  |

|  | - 450 /111 |   |  |  |

## 1 INTRODUCTION

Electric Vehicles have a much longer history than most people realise. Electric vehicles were seen soon after Joseph Henry first introduced the first DC powered motor in 1830. A small model of electric vehicle is built by Professor Stratingh in the Dutch town of Gröningen in 1835. The first full sized electric vehicle was built in 1834 by Thomas Davenport in USA and followed by Moses Farmer who built the first two passengers electric vehicle in 1847. There were no rechargeable electric cells (Batteries) at this time. An electric vehicle did not become a viable option until the Frenchmen Gaston Plante and Camille Faure respectively invented (1865) and improved (1881) the storage battery [1].

Figure 1.1 shows a 1903 Krieger electric car. This car is a front wheel drive electric-gasoline hybrid car and has power steering. A gasoline engine supplements the battery pack. Between 1890 and 1910, there were many hybrid electric cars and four wheel drive electric cars. Electric cars were more expensive than gasoline cars and electrics were considered more reliable and safer [1].

Figure 1.1 1903 Krieger electric car [1].

Electric vehicles are known as Zero Tailpipe Emissions Vehicles, and they produce less pollution than Petrol or LPG powered vehicles. As electric vehicles have fewer moving parts, maintenance is also minimal. With no internal combustion engine there are no oil changes, tune-ups, timing and most of all no exhausts. Electric vehicles are also far more energy efficient than gasoline engines and they are very quiet too.

Electric vehicles have been in continual use since the 1900s in various applications. Today these quiet vehicles with no tailpipe emissions are no longer limited to golf carts. New advances in battery technology, system integration and aerodynamics, and research and development by major vehicle manufacturers have led to the producing of electric vehicles that will play a practical role on city streets.

## 1.1 University of Canterbury's Electric Vehicle

The University of Canterbury has been involved in the electric vehicle development since 1974 [2]. The objective was to provide a suitable laboratory test bed by which to demonstrate the drive system, control system and various other systems. The University's first electric vehicle development, the "Mark I" was completed in 1976 [3]. Although the vehicle had a limited range of only 40km on one charge, it had demonstrated that an electric powered vehicle could be viable for operation in urban driving conditions.

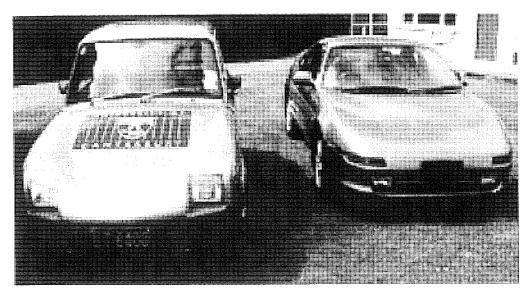

In the early 1980's a second electric vehicle, the "Mark II" was completed in conjunction with the Mechanical Engineering department. The vehicle was based on a 1962 Austin A40 Farina as shown in Figure 1.2. Major body is undertaken to lower the car's aerodynamic drag. With its much improved drag co-efficient over the Mark I, the range of the Mark II is improved to 60km on one charge at a constant 65km/h speed with a top speed of up to 80km/h [4]. As of February 2000, the Mark II had been registered for road use for over 18 months and has clocked up more than 2000 km. The car is now sporting new University logo and a new paint job.

Figure 1.2 University of Canterbury's Mark II (left) and MR2 (right) electric car [5]

The University of Canterbury has purchased a Toyota "MR2" for use as the next version in the electric car research programme. The car as shown in Figure 1.2 was purchased in the early December 1999. Initial planning has commenced on this project by interested staff and students. It is expected to take 2 to 5 years for the conversion and the main areas to investigate are: Auxiliary system, Battery system, Drive system, and Mechanical modifications [5]. This thesis focuses on the Auxiliary system of the MR2.

Similar to the common combustion engine vehicles, electric vehicles requires power supplies and control systems to operate the 12V auxiliaries, such as lights, indicators and wipers. Nowadays, the power and control system for the auxiliaries normally use a pair of wires for supplying power and a single wire for controlling each auxiliary load in a vehicle. This results in a large number of wires in the wiring harness.

An alternative power and control system for the auxiliaries is to use a pair of control lines and a universal power connection around the vehicle. At selected points around the vehicle, small control units are placed to apply power to the desired auxiliary, depending on the current requirements. This reduces the number of wires in the harness and makes it easier to isolate specific circuits. This power and control system is named the "Power Distribution Network" and it is implemented by using multiple power converters (the Auxiliary Power System) and a differential control system (the CAN Control System).

## 1.2 Thesis Outline

This thesis looks at the development of the Power Distribution Network for the electric vehicle, MR2 application. The Power Distribution Network is developed to control and supply power to the auxiliary loads in the vehicle. The main objectives are to demonstrate the operation of the Power Distribution Network, and to investigate whether the efficiency of operation is able to provide fast and reliable control signals to the auxiliary loads.

Chapter 2 of this thesis introduces the Auxiliary Power System and the CAN Control System of the Power Distribution Network including their operating principles. Chapter 3 presents the design of the Auxiliary Power System and its control and protection circuitries are detailed in Chapter 4. In Chapter 5, the design of the CAN Control System is presented and Chapter 6 describes the components and construction of a prototype CAN Control System. Experimental testing is then undertaken to examine the operating characteristics of the completed Power Distribution Network prototype. The results of which are given in Chapter 7. Finally, further development and conclusions are drawn in Chapter 8.

## 2 POWER DISTRIBUTION NETWORK

The University of Canterbury purchased a modern Toyota MR2 sports car with the intention of converting it into an electric vehicle. This chapter presents the plan of designing the Power Distribution Network for the MR2. In the electric vehicle, the Power Distribution Network is designed to control and supplies power to the auxiliaries such as power windows, indicator lights and power steering.

In an electric vehicle, the electrical power is the only source that keeps the vehicle moving. Unlike the common combustion engine vehicle, where the battery can be charged by an alternator while it is travelling. All the major components/parts in an electric vehicle, for instance, the motor, power inverters and all the auxiliary loads, use the limited power that is supplied by the batteries. Therefore in an electric vehicle, energy efficiency is extremely important and the Power Distribution Network must be designed for high efficiency.

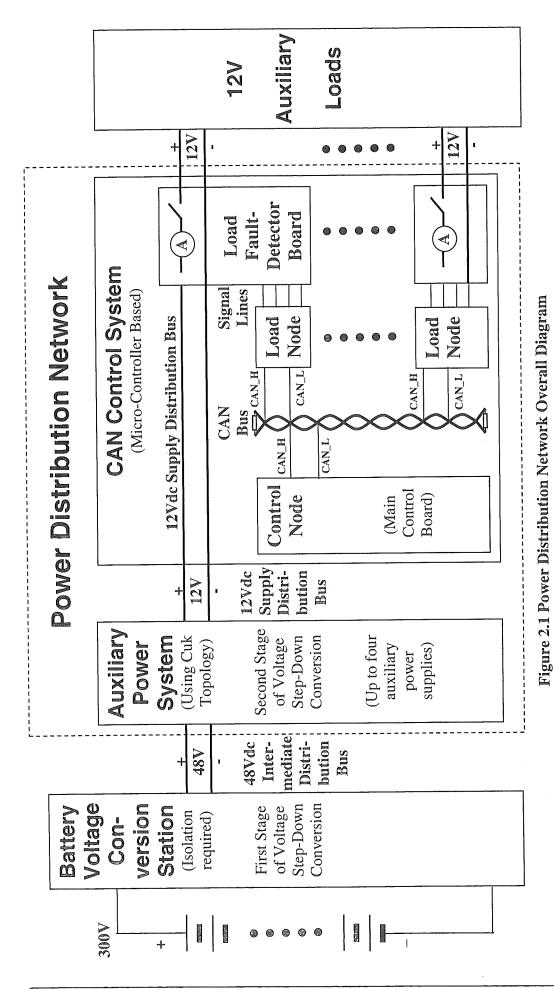

Figure 2.1 shows the Power Distribution Network that is planned for this electric vehicle. The nominal battery voltage of the electric vehicle will be 300Vdc. To provide power to the auxiliary loads, the voltage is stepped down to 12Vdc in two stages. The Battery Voltage Conversion Station block produces a 48Vdc intermediate distribution bus, while the Auxiliary Power System block produces the 12Vdc.

The 48Vdc voltage distribution network is considered more efficient than the usual 12Vdc distribution system because of the following reasons. First, it had a higher voltage which resulted in a lower current that could be withdrawn to deliver the same amount of power to the loads when compared with the usual 12Vdc distribution system.

Page 6

This is a decreased power loss in the wires due to lower current is carried. Second, with a 48Vdc voltage bus, the weight and space required for the wiring could be reduced since smaller and lighter wires could be used in the vehicle. While carrying on with this concept, a 300Vdc distribution network may be more efficient, it is not considered an option because of safety issues. As illustrated in Figure 2.1, the Power Distribution Network consisted of two major systems:

- 1. The Auxiliary Power System, it is designed to provide power to the loads using up to four distributed auxiliary power supplies.

- 2. The CAN (Controller Area Network) Control System, it is designed to provide control to the loads using the standardised Controller Area Network Bus (so-called the CAN Bus) topology. The system has another function of monitoring the status of the loads.

All further details about these two systems will be presented later in the chapter.

#### 2.1 Auxiliary Load Current Investigation

The power requirements of loads that are to be retained in the petrol-electric conversion need to be determined. The power rating is one of the factors that helped determine the type of dc-dc converters that will be used. Current consumption of the loads is important for an electric vehicle as it determines the power rating, number and placement of the dc-dc converters that are going to be built for the Auxiliary Power System in the vehicle.

Auxiliary loads in the vehicle can be classified into two main categories: resistive and inductive. Resistive loads consist of lightings such as headlights, external and internal lights. Other electronics like car audio system and rear defogger are also considered as resistive loads. Inductive loads normally involve motors, such as power steering, heater fans, power window and window wipers. Table 2.1 summarises all the auxiliary loads that are in the MR2 vehicle.

Table 2.1 Auxiliary loads in the vehicle - MR2

| Loads           | Type      | Description                                                     |

|-----------------|-----------|-----------------------------------------------------------------|

| Headlights      | Resistive | Two light bulbs inside each headlight for high beam and         |

| J 0             |           | low beam sight.                                                 |

| External Lights | Resistive | Included red taillights (in dim or brake situation), fog lights |

| 2/1101111112    |           | (not working), reverse lights and hazard (signal) lights.       |

| Internal Lights | Resistive | Included door lights, reading lights and boot light.            |

| Power Steering  | Inductive | Included a motor for hydraulic pressure.                        |

| Fan Heater      | Resistive | Heating elements.                                               |

|                 | Inductive | Included air conditioning system (not working) and fans.        |

| Other           | Resistive | Included car audio system (CD/Tape/Radio player and             |

| Electronics     |           | speakers), real defogger and combination meters.                |

| Liconomos       | Inductive | Included power windows, window wipers, central locking,         |

|                 |           | radio aerial winder, wing mirror and horn.                      |

Measurements are made on the MR2's auxiliary loads. This is harder than first expected. The wiring system is hidden away and difficult to reach. Further measurements may need to be made once the conversion of the car takes place. A multi-meter is used to get some purely average DC current readings from the fuse boxes. Fuses are removed and the probes of the multi-meter are used to complete the circuit and the currents are measured in this way. This method is not acceptable for all measurements due to the fluctuations in current and the type of load. An oscilloscope is used to capture the actual current waveforms. This is done with the addition of a loop of wire into the fuse holder and a CT clamp used in conjunction with the oscilloscope. These waveforms are used to gather detailed information about the auxiliary loads of the Toyota MR2 and the loading requirements for the future Power Distribution Network. Thus, they are all recorded and the magnitude of currents are measured and tabulated for easy reference in Appendix A1.

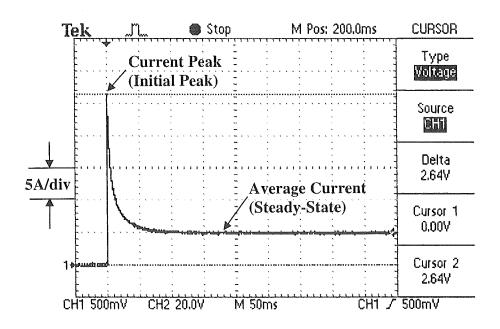

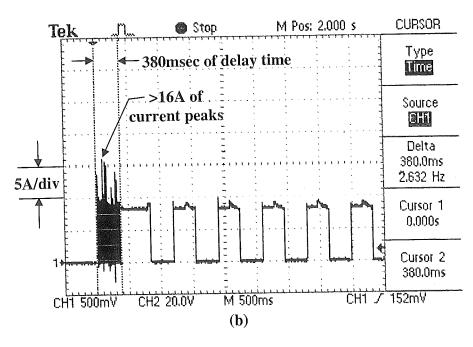

Transient current peaks occurred in the measurements and they exist because loads are switched in and out. Figure 2.2 shows an example of measured red tail-lights current waveform with a dim setting. It appeared that when the light is turned on, the current rises up immediately to an enormous peak value of 26.4A. Although the current is then stabilised relatively quickly down to 5A within 75ms, the amount of the high current peak may still load down the auxiliary power supplies and cause them to drop out or shut down.

Table 2.2 shows the summarised current consumption of the auxiliary loads in the vehicle. It is seen that the headlights, other external lights and power steering consumed the major amount of power. It also shows that the magnitude of current peaks is extremely large. They are about twice as large as the average current of the loads. These current peaks resulted in a significant power loss and this can not be afforded by the supply batteries because of the limited energy stored in it. Therefore, efficient use of the power becomes a major concern in the design.

Figure 2.2 Current waveform of red taillights in dim situation (Current scale: 5A/div; Time scale: 50ms/div)

Table 2.2 Maximum current demand of the loads

|                             | Maximum Current Consumed |                 |  |  |

|-----------------------------|--------------------------|-----------------|--|--|

| Loads                       | Peak Current             | Average Current |  |  |

|                             | (Initial peak)           | (Steady-State)  |  |  |

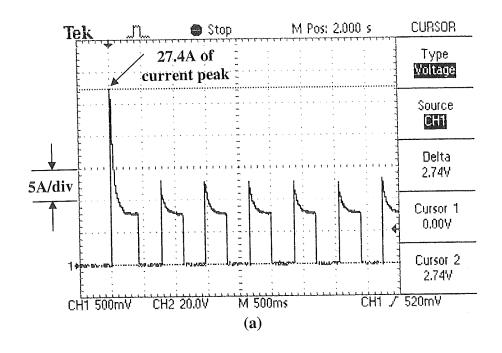

| Headlights                  | 27.4A                    | 15A             |  |  |

| External Lights             | 53.8A                    | 31A             |  |  |

| Internal Lights             | 10.3A                    | 2.1A            |  |  |

| Power Steering              | 49.2A                    | 25A             |  |  |

| Fan Heater                  | 25.6A                    | 11.8A           |  |  |

| All Other Electronics (see  | 42.1A                    | 20A             |  |  |

| Table 2.1 for descriptions) |                          |                 |  |  |

| Total                       | 208.4A                   | 104.9A          |  |  |

## 2.2 Efficiency Improvement Method

Current peaks have to be reduced as they lead to a significant power loss in the system. In order to minimise the peaks, an experiment to check performance under current limiting conditions is undertaken on most of the loads. In the experiment, the auxiliary parts are tested under the condition of limiting the supply current to its average value (see Table 2.2) and seeing whether it still functions the same.

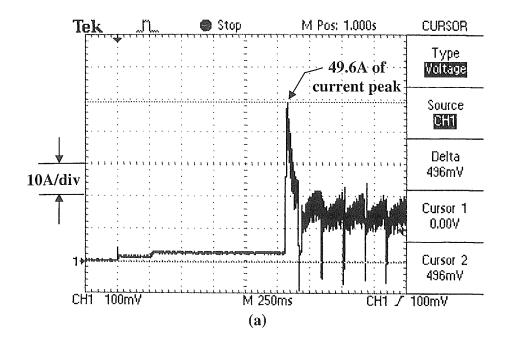

Since all the auxiliary loads are classified as being either resistive or inductive as indicated in Table 2.1, an auxiliary load from each category is picked as an example to demonstrate how the experiment is carried out. Power steering (inductive) and hazard lights (resistive) are selected due to their significant power consumption and high peak current as shown in Figure 2.3(a) and Figure 2.4(a).

In the experiment, power steering is tested using 25A as the limited current. The power steering operates successfully at current levels less than 25A. Peak current limiting only occurs when the steering operates in hard lock. In hard lock no power steering boot is required so the current limit to 25A does not affect the steering operation. Figure 2.3(b) shows the current waveform of the power steering under the current limiting test of 25A. The graph revealed that the current peak has been reduced significantly from the original 49.6A down to less than 28A. The use of current limiting result in reduced energy consumption from the supply batteries.

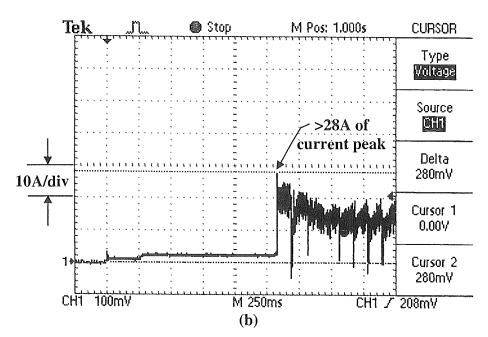

Figure 2.4(b) shows the current waveform of the hazard lights captured when 8A of current limiting is applied. It appeared that the current has been reduced successfully down to 16A from the original current peak of 24.4A as shown in Figure 2.4(a). Note that with the current limiting on the hazard lights, a delay time of 380ms, due to current limiting exists before the hazard lights start to flash. This is not considered as a problem because 380ms is not a significant delay time which may be noticed by people.

Figure 2.3 (a) Current waveform of the power steering with no current limiting applied. (Current scale: 10A/div; Time scale: 250ms/div)

(b) Current waveform of the power steering under the 25A of current limiting test. (Current scale: 10A/div; Time scale: 250ms/div)

Figure 2.4 (a) Current waveform of the hazard lights with no current limiting applied. (Current scale: 5A/div; Time scale: 500ms/div)

(b) Current waveform of the hazard lights under the 8A of current limiting test. (Current scale: 5A/div; Time scale: 500ms/div)

All other auxiliary parts under the test are found to operate properly in the current limit tests, thus, the power ratings of the converters are decided based on the average current values of the loads. Also, the current limiting capability is required to be added to these converters in order to reduce the peak current demand of the auxiliary loads.

Another way of reducing power consumption in the car is to replace all the external and internal light bulbs in the vehicle, except headlights, with high intensity LEDs. Preliminary calculations are carried out to show that the current consumption of these loads can be decreased significantly if LEDs are used. For example, the current consumption of external lights could be reduced from 31A to 10A by replacing all the external lights by LEDs. Table 2.3 summarised current consumption of the external and internal light bulbs in the vehicle after the high intensity LEDs are applied.

Table 2.3 Power consumption of the vehicle lights before and after the replacement of high intensity LEDs

| Lights                | Current Required in normal light bulbs | Current Required in high intensity LEDs |

|-----------------------|----------------------------------------|-----------------------------------------|

| External Lights       | 31A                                    | 10A                                     |

| (Excluded Headlights) |                                        |                                         |

| Internal Lights       | 2.1A                                   | 0.7A                                    |

#### 2.3 Power Supply Placement in the MR2

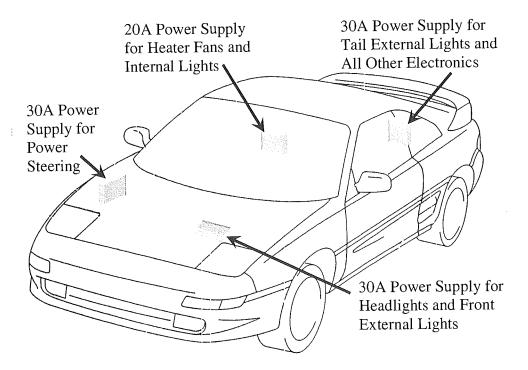

Using the information provided by the Table 2.2 and Table 2.3, a decision is made to use up to four converters with output current ratings that ranged from 20 to 30A. Specifically, as the average current consumed in power steering is around 25A, one converter with a 30A output is placed nearby it to supply the power. Another 30A power supply is going to be located in front of the vehicle and supplied the headlights and front external lights. A 20A converter is placed behind the driver's seat to supply the internal lights and heater fans. Finally, the power of all other electronic equipments and the external taillights is supplied by a 30A power supply inside the boot of the vehicle. Figure 2.5 illustrates the placement of the four power supplies used in the vehicle.

As an initial step in the project, a dc-dc converter with a 30A output current has been built and deign procedures are presented in the following chapters.

Figure 2.5 Power supply placements in MR2

## 2.4 Auxiliary Power System

The Auxiliary Power System is designed to provide power to the 12Vdc auxiliary loads with various current ratings. The power received from the 48Vdc intermediate bus could be stepped-down to 12Vdc either by using a single power supply with large power rating or by using number of lower power rating power supplies. Since efficiency is the major concern of the research, smaller power rating power supplies will be built because of lower current that could be withdrawn and the reduction in the power loss in the wires. Another advantage of this configuration is that smaller wire and wire loops can be formed in the vehicle to reduce the space required and radiated RFI (Radio Frequency Interferences).

The Auxiliary Power System consisted of four power supplies with differences in the power consumption due to the type of individual auxiliary load. These power supplies are dc-dc step-down converters with no transformer isolation as isolation is already involved in the Battery Voltage Conversion Station block as shown in Figure 2.1.

To design the Auxiliary Power System, all the possible topologies of dc-dc converters are required to be researched. Since efficiency is the major concern in the application, a high efficiency converter is required to be selected as the most appropriate topology to supply the various distributed auxiliary loads. More information on the converter's topology research and its design are presented in Chapter 3. Chapter 4 described the control circuitry and construction of the converter.

## 2.5 CAN (Controller Area Network) Control System

The CAN Control System is developed to control the auxiliary loads such that the auxiliary loads could be turned on and off using logic level MOSFET switches. It is also designed to monitor the status of the auxiliary loads which provide extra protection on both the network and loads.

The CAN Control System consisted of various micro-controller and CAN protocol controller based circuit boards (so-called CAN nodes). All the CAN nodes are connected to a twisted pair of wires (so-called the CAN Bus) to transmit and receive messages. The reason of selecting CAN is because it reduced the wiring harness weight and complexity in the vehicle. The design and construction of the CAN Control System are presented in the Chapter 5 and Chapter 6.

## 2.6 Summary

The Power Distribution Network is presented and can be used in an electric vehicle application. It is divided into two major systems: the Auxiliary Power System, which is in charged of converting and delivering power to the loads, and the CAN Control System, that is used to control and monitor the auxiliary loads.

The 300Vdc nominal battery voltage is converted to 48V intermediate voltage. This configuration is considered more efficient than the usual 12Vdc distribution system since smaller and lighter wires can be used to carry same amount of power. Current consumption investigations are made on the MR2's auxiliary loads. Transient current peaks occurr when switch loads are switched in and out. These may load down the auxiliary power supplies and cause them to drop out or shut down. In order to use the limited battery energy more efficiently, current limiting capability is added to the converters with the intention of reducing the peak current demand of the auxiliary loads. Additionally, high intensity LEDs could be used to replace the existing light bulbs to further improve efficiency.

The type of loads determines the power rating, number and placement of the auxiliary dc-dc converters that form the Auxiliary Power System in the vehicle. The converter's topology research and its design are presented in the next chapter, Chapter 3.

## **3 CONVERTER DESIGN**

In order to implement the Power Distribution Network as outlined in chapter 2, the Power Distribution Network must provide both power and control to all the auxiliary loads in the vehicle. In order to provide the power, an Auxiliary Power System is required to convert voltage from 48V-to-12Vdc using up to four distributed auxiliary power supplies as mentioned in Section 2.3. The required power ratings of these power supplies are in the range of 240Watts to 360Watts. There are three major dc-to-dc power supply technologies that can be considered to implement the auxiliary power supplies and they are:

- 1. Linear regulators.

- 2. Pulse Width Modulated (PWM) switching power supplies.

- 3. Resonant/quasi-resonant switching power supplies.

Linear regulators are used predominantly in ground-based equipment where the generation of heat and low efficiency are not of major concern. Each linear regulator has an average efficiency of between 35 and 50 percent and the loss is dissipated as heat. Since energy efficiency is the major requirement in the electric vehicle application, linear regulators have not been considered as an appropriate topology for the auxiliary power supplies.

Topologies of PWM switching power supplies are more suitable for the auxiliary power supplies due to their higher efficiency (between 70 and 85 percent) and more flexible use than linear regulators. One commonly finds them used within aircraft, automotive products and generally those applications where high efficiency is required. Their weight is much less than that of linear regulators since they required less heatsinking for the same output power ratings.

Resonant/quasi-resonant switching power supplies can be built with a smaller size and lighter weight when compared to PWM switching power supplies for the same output power ratings. This is because of the resonant/quasi-resonant switching power supplies are normally operated with higher switching frequencies (> 200 kHz), which decreases the size of the magnetic components. They are also suitable for applications that required high output power ratings (> 1kW). Since the auxiliary power supplies have a power rating of less than 500W and does not required to be operated with a very high switching frequency, resonant/quasi-resonant switching power supplies have not been selected although they may offer higher efficiencies.

There are numbers of possible converter topologies using PWM switching technology. Transformer isolation was not required in the auxiliary power supplies since isolation exists in the Battery Voltage Conversion Station (see Figure 2.1). However, transformers can still be used to provide step down ratios. Topologies of transformer isolated PWM converters are investigated; these include Forward, Flyback, Push-pull, Half-bridge and Full-bridge converters.

A Full-bridge converter is not considered due to it being more applicable to higher output power ratings (>1kW). Push-pull and Half-bridge converters are not selected, because the power supply is required to be reliable and controlled by single switch if possible. Since the Flyback converter has a discontinuous input current, and with a small duty ratio will draw a high peak current (around 30Ap-p for the design) from the output of the Battery Voltage Conversion Station. This poses a significant difficulty for the conversion design; therefore, the Flyback converter is not a suitable choice. A Forward converter is not selected due to its magnetic complexity and extra windings are needed which lead to an increase of the converter's overall size.

Although that the transformer isolated converters may develop a slightly higher overall efficiency, when compared to the non-isolated PWM converters, they are not suitable for the design due to their characteristics as mentioned above and the transformer isolation was not required. Topologies of non-isolated PWM dc-dc converters are therefore selected to implement the auxiliary power supplies.

A standard approach of using non-isolated PWM technology to convert 48-to-12Vdc is to use a buck converter with an output filter. However, due to the discontinuous input current characteristic of buck converters, the topology is found not to be acceptable.

The Cuk converter topology is selected because it has both continuous input and output current with a low current ripple. Since the input and output inductor currents are essentially constant in steady state, the switching current is confined entirely within the converter, in the transistor-coupling capacitor-diode loop. With careful layout, this loop can be made physically small, which will reduce the radiated RFI and improves the efficiency. In addition, the voltage and current waveforms in this converter are particularly clean, with very little ringing or overshoot, and therefore very little snubbing is required [6].

As an initial stage in designing the auxiliary power supplies using Cuk converter topology, a 360W Cuk converter is designed and implemented as the power supply for the power steering in the vehicle.

The following sections of the chapter present the design of the 360W Cuk converter. This includes a brief description of the Cuk topology, followed by the design objectives and specifications of the converter implementation. Switching frequency selection is found to be the key parameter to gain the best compromise between the converter's size and efficiency. Therefore, preliminary calculations and PSPICE simulations are made to estimate the component loss in the converter. Then a simulated Cuk Converter's efficiency graph, over a range of switching frequencies, is derived to select the switching frequency of the converter. After that, inductor design procedures are presented and followed by the reasons for component selection. Finally, a summary is attached in the end of the chapter to summarise the design of the 360W auxiliary power supply using Cuk converter topology.

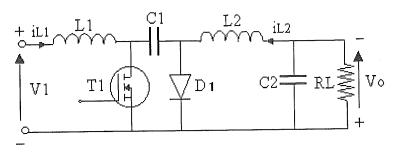

## 3.1 Cuk Converter Topology

Figure 3.1 illustrates the schematic Cuk converter and Table 3.1 shows the theoretical formulae derived from the operation [7]. Referring to the Figure 3.1, when switch T1 is open, the diode D1 is forward biased and capacitance C1 is charging in

positive direction through inductance L1. Consequently, during the interval when T1 is closed, D1 is reverse biased and C1 discharge through L2 and load RL, thus charging the output capacitance C2 to a negative voltage. Finally, to close the complete cycle, when T1 is opened again, D1 conducts again and the capacitance C1 is charged positively using the stored energy in L2. [8].

Figure 3.1 Cuk converter

| Vo/V <sub>1</sub>                                    |                                                                                                                                      |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| $\Delta Vo/V_1$                                      | $\frac{1-D}{8\cdot L\cdot C\cdot f^2}$                                                                                               |

| L (Where D = Duty ratio and f = Switching frequency) | $L1 = \frac{V1 \cdot D}{f \cdot \frac{iL1}{dt}}$ $L2 = \frac{V1 \cdot D}{f \cdot \frac{diL2}{dt}}$                                   |

| (Where $\frac{dV}{dt}$ = Rate of change of voltage)  | $C1 = \frac{Vo \cdot D}{RL \cdot \frac{dvC1}{dt} \cdot f}$ $C2 = \frac{Vo \cdot (1 - D)}{8 \cdot \frac{dVo}{dt} \cdot L2 \cdot f^2}$ |

Table 3.1 Equations of Cuk converter [7]

## 3.2 Design Objectives

In the auxiliary loads investigation carried out in Chapter 2, the normal functional voltage for auxiliaries in the vehicle is found between 11V to 13Vdc. Therefore, the output voltage supplied from the Cuk converter is specified as 12Vdc ±10%, which is inside the normal operational range of the auxiliary loads. Current ripple is not the main factor that influences the performance of the auxiliary loads in the vehicle, a maximum current ripple of 4.2Ap-p is found during the investigation. This specified the output current rating of the Cuk converter of 30A±10%. Table 3.2 tabulated the specifications of the Cuk converter design.

Table 3.2 Design requirement

| Input Voltage             | 48Vdc                               |

|---------------------------|-------------------------------------|

| Output Voltage            | 12Vdc ± 10%                         |

| Output Current            | $30A \pm 10\%$                      |

| Maximum Output Voltage    | 1.2V peak-to-peak                   |

| Ripple                    | (≤10% of 12V)                       |

| Maximum Current Ripple of | 3A peak-to-peak                     |

| Inductance L2             | $(\le 10\% \text{ of } 30\text{A})$ |

| Minimum Efficiency        | Preferably > 85%                    |

| Input Protection          | Reverse voltage                     |

| Output Protection         | Over voltage, Over                  |

|                           | current, Short circuit              |

The output voltage and current ripple values are set to  $\pm 10\%$  to match the tolerance of the output voltage and current. According to the paper [8], with a proper design and PCB layout, Cuk converters are be able to obtain a high efficiency of 90 percent. Thus, the efficiency of the design is preferably to be greater than 85 percent. Since the Cuk converter is required to be robust and reliable, input and output protection is required for the converters. All the details on this protection are presented in the Chapter 4.

#### 3.3 Component Calculation

In order to design a converter, the switching frequency is required to be set initially since it determines the efficiency and size of the converter. For hard switching topologies, the switching frequency is normally in the range of 25~200 KHz. At the various switching frequencies, preliminary calculations on component sizes are made based on each individual switching frequency of 25, 50, 100, 150 and 200 kHz. Theoretical equations listed in Table 3.1 are used to carry out the component calculations.

To initial size the converter a switching frequency of 100 kHz is selected as being middle of the range. It also provides a good compromise between the efficiency and component sizes. The design specification listed in Table 3.2 is applied and the calculation results at the 100 kHz switching frequency is tabulated in Table 3.3.

Table 3.3 Calculated component sizes at the switching frequency of 100 kHz.

| Duty Rati | o, D    | 33%         |

|-----------|---------|-------------|

| Inductano | e, L1   | 211.2μΗ     |

|           | L2      | 52.8µH      |

| Capacitar | nce, C1 | 33µF        |

|           | C2      | 15.86µF     |

| Load      | RL      | $0.4\Omega$ |

An efficiency of 100 percent is assumed for the calculations and the component values listed in Table 3.3 are the exact values derived. However, during the implementation of the converter, the assumption is proved not to be completely valid and modification to the component sizes is required. These will be discussed later in Section 3.7 and 3.8.

All the calculation results at the various switching frequencies are included in Appendix B1. Converter simulations are carried out based on the results and they are presented in the following section.

## 3.4 Converter Simulation

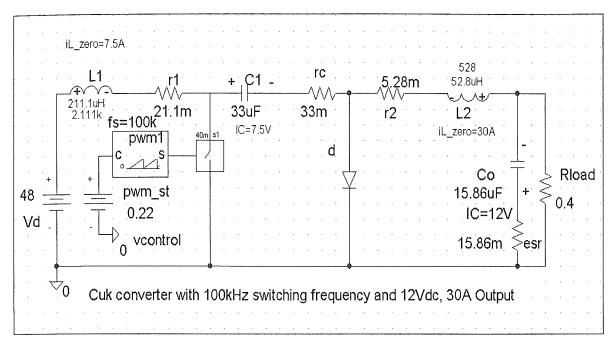

PSpice is used to simulate the converter at the discrete switching frequencies from 25 kHz to 200 kHz. The simulation results are included in Appendix B2. Since the switching frequency of 100 kHz is presumed to provide a good compromise between the efficiency and component size as mentioned in Section 3.2, the calculation results listed in Table 3.3 are used in the simulation.

Figure 3.2 shows the simulation model of the 360W Cuk converter in Pspice. The 48V DC source is assumed to be constant and ripple free and the switching devices, s1 and d are assumed to be ideal. The switching devices, s1 and d are also modelled with a MOSFET model RFP40N10 (40A/100V) and a diode model 30CPQ100 (30A/100V, Schottky). These switching device models are chosen as they have the closest ratings to the results of the theoretical calculations [9]. Further details on the selecting reasons will be discussed in Section 3.8.

Figure 3.2 The Cuk converter simulation model

As shown in Figure 3.2, the passive components, L1, L2, C1 and C2 each simulated with a series resistance component. These series resistances present the losses of the passive components and the values are derived from the theoretical calculations [9]. All the further details in the circuit loss estimation are presented in the following section.

Figure 3.3 shows the voltage and current waveforms generated from the simulation at the switching frequency of 100 kHz. The waveforms are captured when the steady-state is reached and lasted for two switching periods.

A voltage ripple of 140mVp-p (2%) is obtained at the output of the converter as shown in Figure 3.3(a). Figure 3.3(b) and (c) show the inductor L1 and L2 current waveforms respectively. In inductor L2 the current ripple is 2Ap-p (6.7%). A large amount of pulsed current, 42Ap-p, flows through the switch and capacitor C1 on each PWM cycle as shown in Figure 3.3(d) and (e) respectively. These waveforms showed the voltage and current ripple requirement set in Table 3.2 has been meet in the simulation.

Figure 3.3 Simulation waveforms

### 3.5 Circuit Losses Estimation

At the various switching frequencies, theoretical calculations are made to determine the component values and their losses [9]. Figure 3.4 illustrates the estimated component losses of the converter over a range of switching frequencies.

In the hard-switching PWM converter, the major power losses are the conduction and switching losses in the switching devices. Conduction losses occur because of the voltage drop across the device and the current flowing through the device occur simultaneously during conduction. Switching losses are incurred by the simultaneous presence of voltage and current during switching. These losses can be calculated using simplified device model.

### 3.5.1 Conduction Loss in the Switching Devices

For the conduction loss calculation, the device can be simplified either as a constant voltage drop in or a linear resistor. The conduction loss in MOSFETs and diodes can be calculated using the measured values of turn-on drain-to-source resistance, Ron and the forward voltage drop,  $V_f$  respectively from the data sheets. The conduction loss of a MOSFET and a diode are expressed in Equations 1 and 2 respectively.

$$Pc_{MOSFET} = I_d^{2*}Ron*D$$

(Equ. 1)

$$Pc_{\text{diode}} = V_f * I_{\text{diode}}$$

(Equ. 2)

Where  $I_d$  and  $I_{diode}$  are the currents flowing through the MOSFET and diode respectively. The duty cycle, D is set to 0.22 while the calculation is carried out.

#### 3.5.2 Switching Loss in the Switching Devices

In the hard-switching PWM converter, three components of the switching losses can be identified; MOSFET turn on losses, MOSFET turn off losses, and the losses due to diode reverse recovery. The switching losses in the hard switching PWM converter can be calculated using the measured values of switching energy from the data sheets. Data sheets normally give the measured values of turn-on, turn-off time (ton, toff) and reverse recovery time, trr. The switching losses in the hard-switching PWM converter are expressed in Equation 3 and 4 respectively as follows:

$$Ps,MOSFET = 0.5*Vds*Id*fs*(ton+toff)$$

(Equ.3)

$$Ps, diode = fs*(trr*IRM)/2$$

(Equ.4)

Where Vds is the voltage across the MOSFET, fs is the switching frequency (using 25 kHz to 200kHz) and IRM is the maximum reverse recovery current of the diode.

#### 3.5.3 Losses in the Passive Components

The power losses in the passive components are determined by finding the product of their series resistance and the current flowing through them. Using the information provided in Figure 3.4, PSPICE simulations are carried out again to determine the overall efficiency of the converter over a range of switching frequencies as shown in Figure 3.5.

Figure 3.4 Estimated Cuk converter component loss

# 3.6 Switching Frequency Selection

The need for a high efficiency converter indicates a careful selection of switching frequency. This in turn has an impact on the size of the passive components. Using Figures 3.6 and 3.7 a choice of 100 kHz as the switching frequency is made. This choice is a compromise between choosing high efficiency and small components. For maximum efficiency, 75 kHz of switching frequency will be the choice. However, when looking at Figure 3.7, there is not a significant difference in efficiency between the 75 kHz and 100 kHz. But also the 100 kHz provides smaller component size. In terms of the realistic, savings in the weight and space in the vehicle is a more important factor than the marginal changes in the efficiency. Thus, to achieve a best compromise between efficiency and component size, a switching frequency of 100 kHz is used.

Figure 3.5 Simulated Cuk converter efficiency

# 3.7 Inductor Design

The design of inductor L1 is carried out before L2. The basic inductor design procedure of Billings is followed [10]. Using the simulated current ripple as shown in Figure 3.3(b) and (c) and the input parameters listed in Table 3.4, the inductors are designed.

Table 3.4 Input parameters of inductance design

| Inductor     | L1      | L2     |

|--------------|---------|--------|

| Inductance   | 211.2uH | 52.8uH |

| Peak Current | 9.6A    | 32A    |

| DC Current   | 9.4A    | 31A    |

| Max. Temp.   | 100°C   | 100°C  |

Inductor L1 and L2 are wound on ETD49 and ETD59 ferrite core respectively. Theoretical calculations are carried out and found that without a air-gap, both inductor cores would be saturated at the 100kHz switching frequency. Therefore an air-gap must be added in these cores to reduce the magnetic flux density. However, there is an impact on the extra windings will be needed to gain the required inductance. To achieve the best

compromise between the core size and the copper loss, an air-gap of 3mm is selected for both cores. This is verified from the tables and figures provided in the Philips Soft Ferrite data book [11]. Table 3.5 lists the results of the inductor design.

Table 3.5 Design results of input and output inductor

| L1                   | L2                                                             |

|----------------------|----------------------------------------------------------------|

| ETD49                | ETD59                                                          |

| 3mm                  | 3mm                                                            |

| 29 turns             | 12 turns                                                       |

| Copper               | Copper                                                         |

| 0.45mm               | 0.45mm                                                         |

| 15 wires             | 35 wires                                                       |

| 3.6A/mm <sup>2</sup> | 4.5A/mm <sup>2</sup>                                           |

| 213uH                | 52uH                                                           |

|                      | ETD49 3mm 29 turns Copper 0.45mm 15 wires 3.6A/mm <sup>2</sup> |

# 3.8 Component Selections

### 3.8.1 Capacitor

In the Cuk converter topology, all the current transferred from input to output must pass through the capacitor C1. The converter as designed delivers high currents and this results in an enormous ripple current flowing through the capacitance C1 during each PWM period. This is confirmed by PSPICE simulation as shown in Figure 3.5(e). Due to a large ripple current of up to 40Ap-p, electrolytic capacitors are considered not to be suitable. Plastic Film type of MKT capacitors are used since they offer high AC stress properties. The capacitors that form the output filter must also be able to handle an appreciable amount of ripple current of up to 3Ap-p. Ten of  $4.7\mu F$  electrolytic capacitors are placed in parallel as the output capacitors C2 to take this ripple.

### 3.8.2 MOSFET and Diode Switch

To maximize the efficiency of the converter, the switch is chosen to have low conduction and switching losses. An Intersil RFP40N10 N-channel MOSFET is selected to provide higher than necessary current and voltage ratings with low  $R_{DS,(ON)}$  of  $0.04\Omega$  and fast on and off switching times 47ns and 62ns respectively.

Since the converter is used in a step-down application, high forward-voltage drop in the diode that will result an enormous power loss in the converter. An International Rectifier 30CPQ100 high efficiency, schottky diode is chosen that offer a low forward-voltage drop of 0.86V with the capability of handling large current and reverse blocking voltage drop of 30A and 100V respectively.

### 3.9 Summary

Various DC-to-DC PWM converter topologies that are suitable for implementing the Auxiliary Power System have been researched. The Cuk converter is selected because it has both continuous input and output current with high efficiency. The topology of the Cuk converter is studied and the design specification is set. PSpice simulations are then carried out to determine the characteristics of the converter under the full load condition. Theoretical calculations are made to estimate the component losses in the converter at the various switching frequencies and a switching frequency of 100 kHz was selected as the best compromise between the efficiency and the component size.

To construct the prototype of the converter, passive components and switching devices are selected according to the results from the calculations and the simulations. PWM and protection circuits are required to control and protect the converter. These control circuits for the Cuk converter are presented in the following chapter, Chapter 4.

|  |  | Chapter | 3: | Converter | Design |

|--|--|---------|----|-----------|--------|

|--|--|---------|----|-----------|--------|

# **4 CONVERTER CONTROL DESIGN**

This chapter describes the circuits used to control the PWM operation of the 360W Cuk converter. The overall control design consists of implementing negative feedback compensation, current sensing and pulse-by-pulse current limiting around an analogue PWM controller IC. In addition, an automatic shut-down control circuit is also implemented to provide extra protection for against over current at the output.

There are two types of PWM control mode strategies available nowadays, the voltage mode control and the current mode control. Before starting the whole process of the control circuit design, a question is generated when looking at the design requirements listed Table 3.2. Which PWM control mode strategy is more suitable for this specific application? However, there is no single strategy which is optimum for all applications. Therefore, to answer the question as to which control strategy is the best for this specific application, one must start with knowledge of both the advantages and disadvantages of each strategy. The strategy chosen will be based on which approach closer meets the design requirements. The following sections attempts to discuss this in a consistent way for these two power supply control strategies.

# 4.1 Voltage Mode Control

The basic voltage mode configuration for the Cuk converter is shown in Figure 4.1. The major characteristic of this design are that there is a single voltage feedback path. The output PWM signal is generated by the LATCH after comparing the voltage error signal Ve with a constant ramp waveform (or the "sawtooth") at a fixed frequency clock. The voltage error signal, Ve, is the voltage generated after passing the output voltage, Vout, through the compensation network that consists of the error amplifier and two impedances. The

sawtooth waveform  $V_R$  is produced from the external RC circuit at the ramping frequency with respect to the clock pluses from the oscillator. In voltage mode control, current limiting must be implemented in a separate circuit. The advantages of voltage-mode control are [12]:

- A single feedback loop is easier to design and analyse.

- A low-impedance power output provides better cross-regulation for multiple output supplies.

- A large-amplitude ramp waveform provides good noise margin for a stable modulation process.

Voltage mode's disadvantages can be listed as [12]:

- Any changes in line or load must first be sensed as an output change and then corrected by the feedback loop. This usually means slow response.

- The output filter adds two poles to the control loop requiring either a dominant-pole low frequency roll-off at the error amplifier or an added zero in the compensation.

- Compensation is further complicated by the fact that the loop gain varies with input voltage.

Figure 4.1 Voltage Mode Control

# **4.2 Current Mode Control**

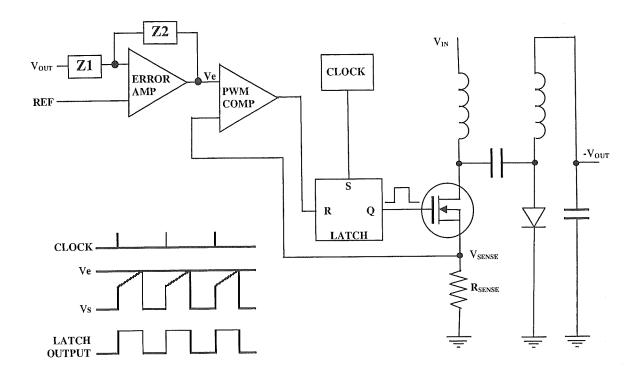

Another control strategy is current mode control. In this case the MOSFET current is controlled as well as the output voltage. As can be seen from the diagram of Figure 4.2, basic current mode control uses the oscillator only as a fixed frequency clock and the ramp waveform is now replaced with a signal derived from MOSFET current instead of the sawtooth as mentioned in the voltage control mode. Therefore, the PWM comparator now compares the error voltage signal, Ve, from the compensator and the MOSFET sensed current signal, V<sub>SENSE</sub>, from the current-to-voltage conversion resistor, R<sub>SENSE</sub>. The output PWM signal is generated by the LATCH using the information provided by the PWM comparator with the respect to the fixed frequency clock pulses. The advantages which this control technique offers include the following [12]:

- Since inductor current rises with a slope determined by Vin-Vo, this waveform will respond immediately to line voltage changes, eliminating both the delayed response and gain variation with changes in input voltage.

- The Error Amplifier is now used to command an output current rather than voltage, the effect of the output inductor is minimised and the filter now offers only a single pole to the feedback loop (at least in the normal region of interest). This allows both simpler compensation and a higher gain bandwidth over a comparable voltage-mode circuit.

- Additional benefits with current-mode circuits include inherent pulse-by-pulse current limiting by merely clamping the command from the Error Amplifier, and the ease of providing load sharing when multiple power units are paralleled.

Disadvantages of current mode control are [12]:

- There are now two feedback loops, making circuit analysis more difficult.

- The control loop becomes unstable at duty cycles above 50% unless slope compensation is added.

- A particularly troublesome noise source is a current spike on the leading edge of the current signal, typically caused by transformer winding capacitance and output diode recovery current.

Figure 4.2 Current Mode Control

Therefore it can be concluded that current mode control overcomes the limitations of voltage mode control. Since voltage feedback compensation and pulse-by-pulse current limiting are the requirements of the project as stated in Table 3.2, the current mode control strategy is then selected. A Unitrode current mode PWM IC, UC3845 is used as the basis of the control circuit for the Cuk converter and the details of the design is discussed in the next section.

# 4.3 Current Mode Control Circuit Design

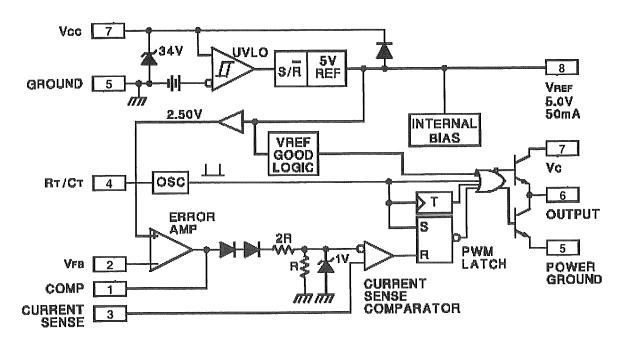

The current mode controller chip, UC3845 is selected since it provides the necessary features to implement a fixed frequency, current mode control Cuk converter with a minimum number of external parts. Figure 4.3 shows the simplified internal circuitry of the 8-pin IC. The UC3845 features an oscillator, a voltage reference, a high gain error amplifier, current sense comparator and a high current totem pole output ideally suited for driving a power MOSFET. Also included are protective features consisting of input and reference under-voltage lockout circuitry, and pulse-by-pulse current limiting. In addition, there is a toggle flip-flop which blanks the output on every second clock pulse, therefore

ensuring that the duty cycle never exceeds 50%. This is particularly useful for the step-down Cuk converter application. Table 3.1 lists the pin descriptions of the UC3845.

Figure 4.3 Internal circuitry of the UC3845 (Refer to Table 3.1)

Table 4.1 Pin Function Description (Refer to Figure 4.3)

| Pin | Feature       | Description                                                                   |  |  |

|-----|---------------|-------------------------------------------------------------------------------|--|--|

| 1   | Compensation  | This pin is Error Amplifier output and is made available for Type one         |  |  |

|     | _             | feedback compensation loops (Section 4.4).                                    |  |  |

|     | Voltage       | This is the inverting input of the Error Amplifier. It is connected to        |  |  |

| 2   | Feedback      | the Cuk converter's output through the resistor divider and the OP-           |  |  |

|     | $ m V_{FB}$   | AMP (Section 4.4)                                                             |  |  |

|     |               | A voltage proportional to the MOSFET current is connected to this             |  |  |

| 3   | Current Sense | point. The PWM uses this information to terminate the conduction of           |  |  |

|     |               | the power MOSFET switch. (Section 4.5)                                        |  |  |

|     |               | The oscillator frequency of 100kHz and the maximum output duty                |  |  |

| 4   | $R_T/C_T$     | cycle of 33% are programmed by connecting a resistor R <sub>T</sub> to the 5V |  |  |

|     |               | $V_{ref}$ and the capacitor $C_T$ to the ground.                              |  |  |

| 5   | Ground        | This pin is combined control circuitry and power ground.                      |  |  |

|     |               | This output directly drives the gate of the power MOSFET. Peak                |  |  |

| 6   | Output        | currents of up to 1A are sourced and sunk by this pin. The output             |  |  |

|     |               | switched at one-half of the 100kHz oscillator frequency.                      |  |  |

| 7   | Vcc           | Positive supply (+15Vdc) of the control IC.                                   |  |  |

| 8   | $V_{ref}$     | The 5V reference output. It provides the charging current for the             |  |  |

|     |               | capacitor $C_T$ and through the resistor $R_T$ .                              |  |  |

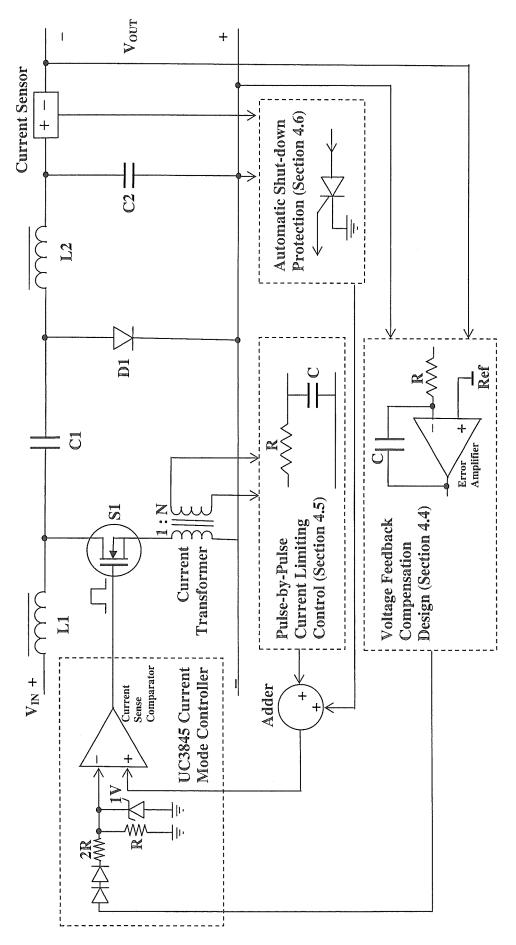

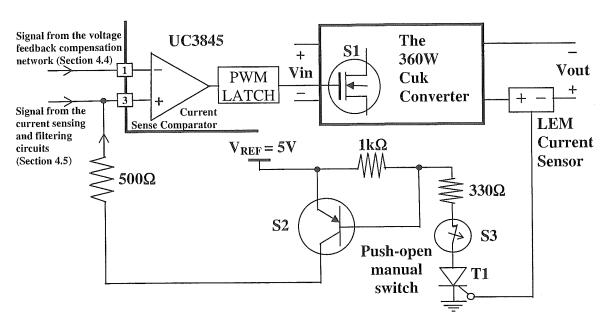

Figure 4.4 shows the current mode control that is implemented for the Cuk converter using the UC3845 chip. There are two main control loops in the current mode control, the voltage feedback compensation and the pulse-by-pulse current limiting as shown in Figure 4.3. The designs of these two feedback loops are to be discussed in Section 4.4 and Section 4.5 respectively. Note that there is an extra input for the Automatic Shutdown Protection. It is used as an extra protection, which will shut-down the converter when over-current is sensed at the output. Section 4.6 discusses the design details of the Automatic Shut-Down Protection loop.

Figure 4.4 Current Mode Control Circuit for the Cuk Converter

automatic shut-down circuits. (see Figure 4.11)

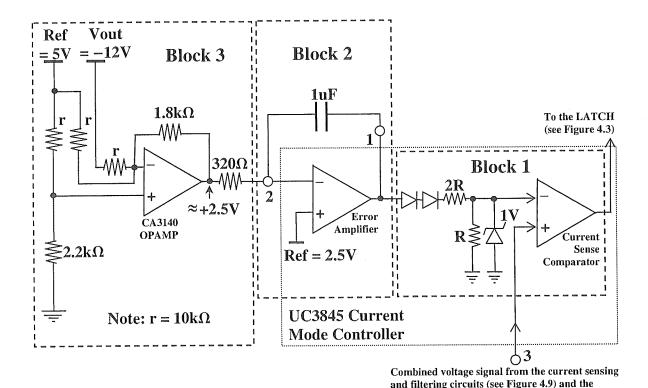

## 4.4 Voltage Feedback Compensation Design

The voltage feedback compensation is designed to regulate the output at 12Vdc. This closed loop feedback also enables a fast and stable response for the Cuk converter. Figure 4.5 shows the closed loop feedback Cuk converter with the major elements separated into three parts. Block 1 is the current sense comparator, which is internally implemented in the UC3845 IC. The output of the comparator is connected to the SR LATCH, which provides the PWM output signal to drive the power MOSFET of the converter. The output of the comparator is produced by comparing the error voltage and the sensed MOSFET current.

Figure 4.5 Block diagram of the voltage feedback compensation network for the Cuk converter.